O 引 言

嵌入式系統(tǒng)就:是一個具有特定功能或用途的計算機(jī)軟硬件結(jié)合體,或指裝入另一個設(shè)備并且控制該設(shè)備的專用計算機(jī)系統(tǒng) 嵌入式系統(tǒng)的最大特點(diǎn)是其具有目的性和針對性,即每一套嵌入式系統(tǒng)的開發(fā)都有其特殊的應(yīng)用場合與特定功能。嵌人式系統(tǒng)包含硬件和軟件兩部分。硬件架構(gòu)以嵌入式處理器為中心,配置存儲器、I/O設(shè)備、通信模塊等;軟件部分以軟件開發(fā)平臺為核心,向上提供應(yīng)用編程接口API,向下屏蔽具體硬件特性的板級支持包BSP。嵌入式系統(tǒng)中,軟件和硬件緊密配合,協(xié)調(diào)工作,共同完成系統(tǒng)預(yù)定的功能。

擴(kuò)頻通信是當(dāng)今國際上高新技術(shù)熱點(diǎn)之一,其理論基礎(chǔ)是香農(nóng)(C.E.Shannon)的信道容量公式。該公式表明,在高斯信道中,當(dāng)傳輸系統(tǒng)的信號噪聲功率比SNR下降時,可用增加系統(tǒng)傳輸帶寬W的辦法來保持信道容量C不變;對于任意給定的信號噪聲功率比,可以用增大傳輸帶寬來獲得較低的信息差錯率。擴(kuò)頻技術(shù)正是利用這一原理,用高速率擴(kuò)頻碼來達(dá)到擴(kuò)展待傳輸數(shù)字信息帶寬的目的。擴(kuò)頻通信系統(tǒng)的帶寬比常規(guī)通信體制大幾百倍至幾千倍,故在相同信噪比的條件下,具有較強(qiáng)的抗噪聲干擾能力。

1 基于嵌入式系統(tǒng)的數(shù)字?jǐn)U頻收發(fā)信機(jī)的硬件設(shè)計

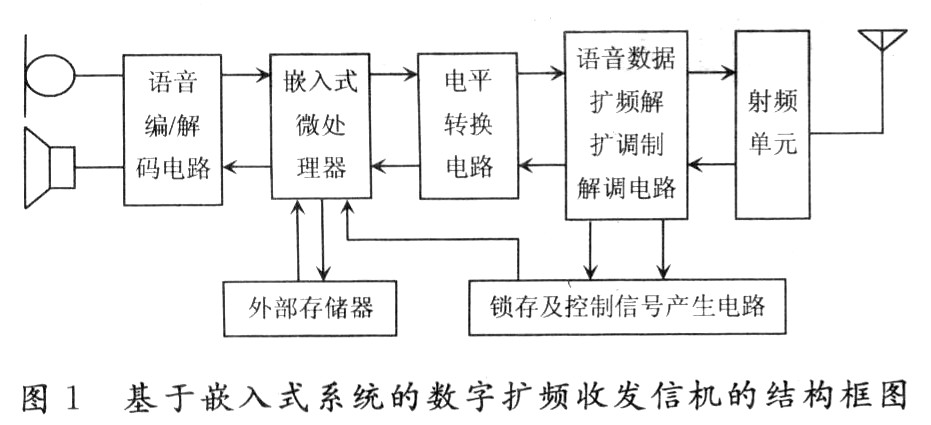

設(shè)計的基于嵌入式系統(tǒng)的數(shù)字?jǐn)U頻收發(fā)信機(jī)結(jié)構(gòu)框圖如圖1所示。

該數(shù)字?jǐn)U頻收發(fā)信機(jī)是雙通道的(圖中只畫出單一通道)。通道由語音編解碼電路、嵌入式微處理器、電平轉(zhuǎn)換電路、語音數(shù)據(jù)擴(kuò)頻解擴(kuò)調(diào)制解調(diào)電路、鎖存及控制信號產(chǎn)生電路、外部存儲器和射頻單元電路組成。

語音編解碼電路采用PHLIPS半導(dǎo)體公司生產(chǎn)的低功耗立體聲音頻編解碼芯片UDAl344TS。該芯片3.O V電源供電,可工作在L3微控制器模式,也可工作在靜態(tài)引腳工作模式,通過模式控制引腳MCl(8腳)、MC2(21腳)設(shè)置為靜態(tài)引腳工作模式(均為高電平),在該模式下,可控制的特征有系統(tǒng)時鐘選擇、數(shù)據(jù)輸入/輸出格式設(shè)置、重低音和靜音控制以及ADC控制,這些特征是由引腳MPl(9引腳)、MP2(13引腳)、MP3(14引腳)、MP4(15引腳)、MP5(20引腳)控制的。

嵌入式微處理器選用SAMSUNG公司為手持設(shè)備設(shè)計的低功耗、高集成度基于ARlM920T核的微處理器S3C2410X。該處理器集成了16 KB指令和16 KB數(shù)據(jù)緩存、MMU、外部存儲器控制器、LCD控制器、NAND FLASH控制器、4個DMA通道、3個UART通道、1個I2C總線控制器、1個I2S總線控制器、4個PWM定時器和一個內(nèi)部定時器、通用I/O口、實(shí)時時鐘、8通道10位ADC和觸摸屏接口、USB主/從接口、SD/MMC卡接口等。

語音數(shù)據(jù)擴(kuò)頻解擴(kuò)調(diào)制解調(diào)電路選用Zilog公司研制的可編程單片直接序列擴(kuò)頻收發(fā)芯片Z87200。該芯片包括發(fā)送部分、接收部分和控制部分,它將擴(kuò)頻通信收發(fā)主要電路的各個部分都集成于一塊100個管腳的芯片中。發(fā)送部分包括了發(fā)送數(shù)據(jù)的白化處理、串并變換、差分編碼、PN碼產(chǎn)生、擴(kuò)頻、QPSK/BPSK調(diào)制及發(fā)定時控制,完成由數(shù)據(jù)輸入到已調(diào)中頻信號輸出的擴(kuò)頻、調(diào)制處理。接收部分包括中頻到基帶的數(shù)字下變換、PN碼產(chǎn)生、數(shù)字匹配濾波、解擴(kuò)、相關(guān)峰檢測、差分解調(diào)、并串轉(zhuǎn)換、去白化處理、數(shù)控振蕩器及位定時處理等,完成由數(shù)字中頻信號輸入到數(shù)據(jù)輸出的全過程解調(diào)解擴(kuò)處理。此外,Z87200還設(shè)置了86 B的片內(nèi)寄存器,用于對芯片功能的編程設(shè)置,使得對擴(kuò)頻系統(tǒng)的設(shè)置具有靈活性,芯片具有通用性,可與計算機(jī)或單片微處理器連接,完成對內(nèi)部寄存器的編程控制。

電平轉(zhuǎn)換電路采用MAXIM公司的雙向8通道電平轉(zhuǎn)換芯片MAX3001E。由于嵌入式微處理器S3C2410X工作電壓通常是3.3 V,而直序擴(kuò)頻收發(fā)器Z87200工作電壓通常是5 V,所以可采用多個MAX3001E來連接這兩個芯片,以實(shí)現(xiàn)它們之間。的邏輯電平轉(zhuǎn)換。

鎖存及控制信號產(chǎn)生電路采用74LV373鎖存器和復(fù)雜可編程邏輯器件EPM7128SLC84-15。在通過接口控制單元向直序擴(kuò)頻收發(fā)器Z87200讀寫數(shù)據(jù)時,為了確保數(shù)據(jù)的穩(wěn)定,采用74LV373鎖存器對要讀寫的數(shù)據(jù)先進(jìn)行鎖存,然后才完成數(shù)據(jù)的讀寫。EPM7128SLC84-15是ALTERA公司生產(chǎn)的一款MAX7000S系列的CPLD器件,用VHDL編程設(shè)計一個8位同步移位寄存器和一個9位同步計數(shù)器,在.Max +PlusⅡ開發(fā)平臺上進(jìn)行編譯仿真后下載在CPLD器件EPM7128SLC84-15上。由于直序擴(kuò)頻收發(fā)器Z87200被設(shè)置為突發(fā)工作模式,為方便數(shù)據(jù)處理,可設(shè)置突發(fā)塊的長度為8符號/幀,配合使用9位計數(shù)器和8位移位寄存器,每移位9次可得到真正需要的8位語音數(shù)據(jù)。

射頻單元采用北京迅通科技公司的PTR8000(以nRF905作為數(shù)據(jù)無線傳輸芯片)高性能嵌入式無線模塊,它專為點(diǎn)對多點(diǎn)無線通信設(shè)計,內(nèi)置數(shù)據(jù)協(xié)議和CRC檢錯,可工作在430/868/915 MHz,工作電壓在1.9~3.6 V之間,最大發(fā)射功率+10 dBM,高抗干擾GFSK調(diào)制,可跳頻,數(shù)據(jù)速率50 Kb/s,獨(dú)特的載波監(jiān)測輸出,地址匹配輸出,地址就緒輸出。由于與RF協(xié)議相關(guān)的高速信號處理部分已經(jīng)嵌入在模塊內(nèi)部,PTR8000可與各種單片機(jī)配合使用,也可以與DSP等高速處理器配合使用;PTR8000提供一個SPI接口,速率由微控制器自己設(shè)定的接口速度決定,在RX(接收)模式中,地址匹配(AM)和數(shù)據(jù)準(zhǔn)備就緒(DR)信號通知MCU一個有效的地址和數(shù)據(jù)包已經(jīng)各自完成,微控制器即可通過SPI讀取接收的數(shù)據(jù)。在TX(發(fā)送)模式中,PTRR8000自動產(chǎn)生前導(dǎo)碼和CRC校驗(yàn)碼,數(shù)據(jù)準(zhǔn)備就緒(DR)信號通知MCu數(shù)據(jù)傳輸完成。

外部存儲器由一塊8 MB的SDRAM(采用HY57V641620)和一塊2 MB的FLASH(采用HY29LVl60)構(gòu)成,主要用于存放程序和數(shù)據(jù)。

2 軟件設(shè)計

嵌入式系統(tǒng)的軟件開發(fā)采用武漢創(chuàng)維特信息技術(shù)有限公司的ADT IDE集成開發(fā)環(huán)境,它提供高效、清晰、可視化的嵌入式軟件開發(fā)平臺,包括一整套完備的面向嵌入式系統(tǒng)的開發(fā)和調(diào)試工具:編輯器、編譯器、鏈接器、工程管理器以及調(diào)試器等,它運(yùn)行于WindowsNT/95/98/2000/XP,采用類似Visual Studio界面風(fēng)格,支持中、英文版本。

在用戶的應(yīng)用程序之前,需要由專門的一段代碼完成對系統(tǒng)的初始化,即系統(tǒng)啟動加載程序。當(dāng)ARM微處理器上電或者復(fù)位之后,處理器從0x0取值,在這個地址處安排的程序就是系統(tǒng)啟動加載程序。由于這類代碼直接面對處理器內(nèi)核和硬件控制器進(jìn)行編程,故采用匯編語言,其任務(wù)包括建立異常向量表、重構(gòu)異常向量表、初始化存儲器系統(tǒng)、初始化堆棧、初始化應(yīng)用程序執(zhí)行環(huán)境、屏蔽所有中斷和呼叫主應(yīng)用程序。

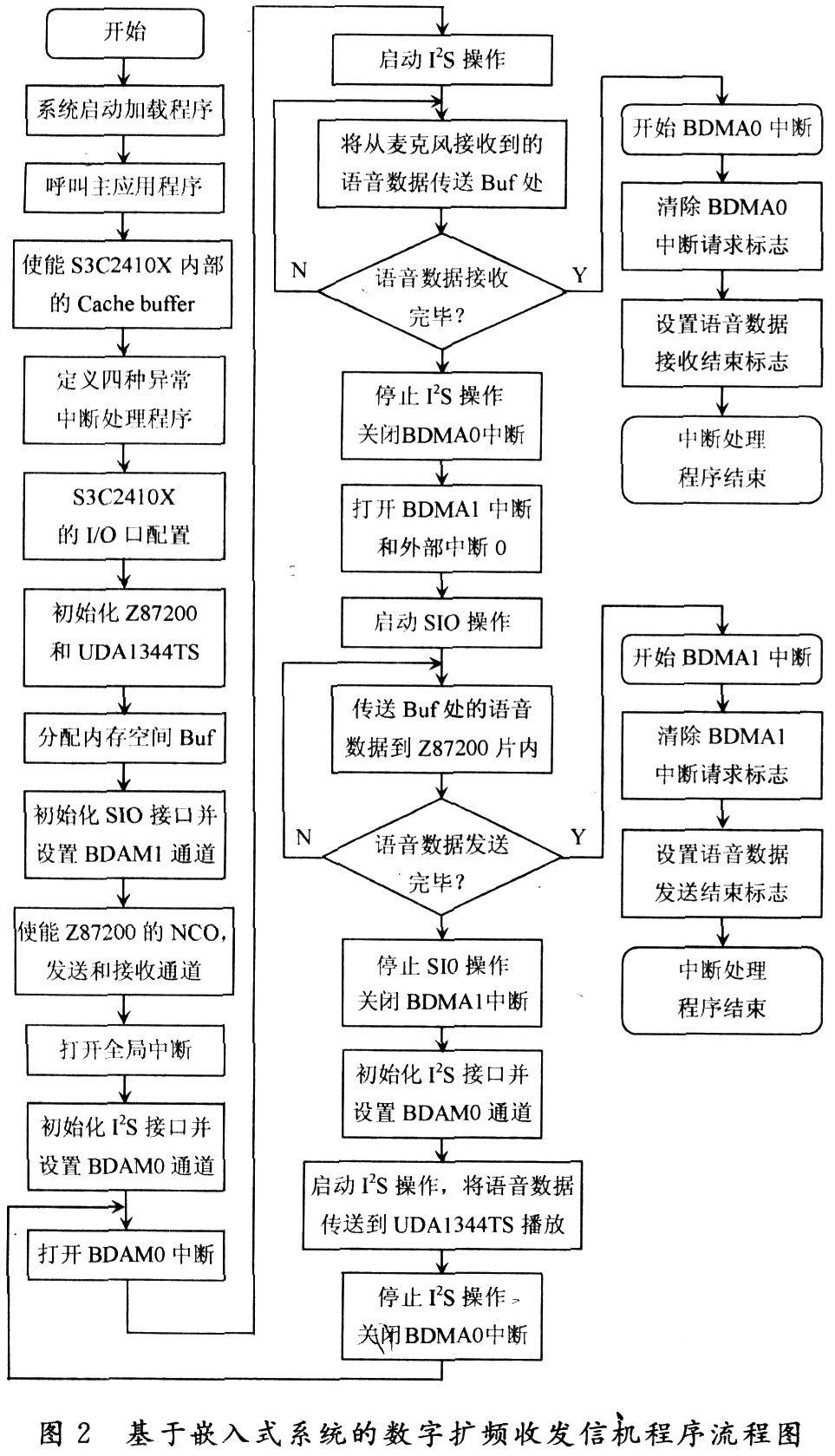

收發(fā)機(jī)系統(tǒng)的主程序主要完成芯片的初始化、接口的配置、語音數(shù)據(jù)流控制和中斷處理等工作,使得收發(fā)機(jī)系統(tǒng)在嵌入式微處理器的控制下能有效地完成語音的錄人、發(fā)送、接收和播放全過程,基于嵌入式系統(tǒng)的數(shù)字?jǐn)U頻收發(fā)信機(jī)程序流程圖如圖2所示。

3 實(shí)驗(yàn)結(jié)果

用匯編語言編寫系統(tǒng)啟動加載程序,用c語言編寫嵌入式微處理器的數(shù)字?jǐn)U頻收發(fā)信機(jī)程序,在ADTIDE集成開發(fā)環(huán)境下添加源代碼,保存后加入到工程中進(jìn)行設(shè)置和編譯,通過后經(jīng)過JTAG簡易調(diào)試器,將應(yīng)用程序燒錄到FLASH中,下載到SDRAM中。將語音編解碼電路、嵌入式微處理器S3C2410X、電平轉(zhuǎn)換電路、語音數(shù)據(jù)擴(kuò)頻解擴(kuò)調(diào)制解調(diào)電路、鎖存及控制信號產(chǎn)生電路、外部存儲器和射頻單元電路正確焊接在PCB板上,上電,運(yùn)行程序。

在發(fā)送端,話音通過麥克風(fēng)送人語音編解碼芯片UDAl344TS,經(jīng)過語音編碼處理后,產(chǎn)生I2-bus格式的串行語音數(shù)據(jù)通過標(biāo)準(zhǔn)I2S語音接口傳送到嵌入式微處理器S3C2410X。S3C2410X將得到的8位語音數(shù)據(jù)存儲到預(yù)先分配好的數(shù)據(jù)區(qū),接著將該數(shù)據(jù)通過同步串行接口SIO一位一位地發(fā)送到語音數(shù)據(jù)擴(kuò)頻解擴(kuò)調(diào)制解調(diào)芯片Z87200片內(nèi)進(jìn)行擴(kuò)頻、BPSK調(diào)制等一系列處理后,得到8位數(shù)字中頻語音信號;最后,通過射頻單元PTR8000無線發(fā)送出去。

在接收端,通過射頻單元PTR8000無線接收到8位數(shù)字中頻語音信號,送入z87200片內(nèi)進(jìn)行解擴(kuò)、解調(diào)等一系列處理,得到串行語音數(shù)據(jù)信號;該信號被送入CPLD器件EPM7128SLC84-15的8位同步移位寄存器;CPLD每得到一個8位語音數(shù)據(jù)就將該數(shù)據(jù)鎖存并產(chǎn)生一個外部中斷,通知嵌入式微處理器S3C2410X將這8位語音數(shù)據(jù)讀走;最后在S3C2410X的控制下將語音數(shù)據(jù)通過I2S接口傳送給語音編解碼芯片UDAl344TS,解碼處理后通過揚(yáng)聲器播放出來。

發(fā)送通道實(shí)現(xiàn)了話音錄人、擴(kuò)頻和BPSK調(diào)制、無線發(fā)送;接收通道實(shí)現(xiàn)了無線接收、BPSK解調(diào)、解擴(kuò)和播放。兩通道可同時進(jìn)行;在無線傳輸時,采用PTR8000高性能嵌人式無線模塊,最大傳輸速率可達(dá)20 Kb/s,最遠(yuǎn)傳輸距離可達(dá)1 km左右。

4 結(jié) 語

闡述了嵌入式系統(tǒng)和擴(kuò)頻通信的含義,以嵌入式微處理器S3C2410X為核心,利用Z87200,UDAl344TS,PTR8000等模塊設(shè)計出了數(shù)字?jǐn)U頻收發(fā)信機(jī)。該文創(chuàng)新點(diǎn)是將嵌入式技術(shù)和擴(kuò)頻技術(shù)融合在一起,同時采用ADT IDE集成開發(fā)環(huán)境調(diào)試嵌入式系統(tǒng)軟件,用嵌入式微處理器對系統(tǒng)其他芯片進(jìn)行編程控制,因而具有很好的靈活性和通用性;根據(jù)所提出的設(shè)計思路,可方便地設(shè)計其他無線通信系統(tǒng),有廣闊的應(yīng)用前景和很好的經(jīng)濟(jì)效益。