NiosII系統(tǒng)是Altera公司的SOPC解決方案,HDLC協(xié)議是通信領(lǐng)域中面向比特的高級(jí)數(shù)據(jù)鏈路控制規(guī)程。

介紹了基于NiosII軟核的HDLC通信協(xié)議的實(shí)現(xiàn)方法,并在協(xié)議實(shí)現(xiàn)的基礎(chǔ)上,完成了對(duì)無(wú)人值守基站系統(tǒng)的監(jiān)控與管理。基站端的功能由基于NiosII軟核的SoPC完成,PC機(jī)作為監(jiān)控中心完成對(duì)基站的遠(yuǎn)程監(jiān)控與管理。本系統(tǒng)在保證雙方可靠通信的前提下,最終實(shí)現(xiàn)PC主控機(jī)與基站之間實(shí)時(shí)、可靠的信息交互與監(jiān)控管理功能。

一 引言

HDLC(High-level Data Link Control)協(xié)議是通信領(lǐng)域中應(yīng)用最廣泛的協(xié)議之一,是面向比特的高級(jí)數(shù)據(jù)鏈路控制規(guī)程,具有強(qiáng)大的差錯(cuò)檢測(cè)功能和同步傳輸特點(diǎn),保證數(shù)據(jù)的可靠傳輸[3]。市場(chǎng)上很多專用的HDLC芯片因追求功能的完備,而使芯片的控制變得復(fù)雜。實(shí)際上對(duì)某些特殊的場(chǎng)合,可選擇HDLC協(xié)議中最符合系統(tǒng)要求的部分功能,設(shè)計(jì)一種功能相對(duì)簡(jiǎn)單、使用靈活的控制器。

NiosII系統(tǒng)是Altera公司的SoPC解決方案,它是一個(gè)運(yùn)行在FPGA上的32位RSIC處理器。Altera公司對(duì)于NiosII的開(kāi)發(fā)提供了強(qiáng)大的設(shè)計(jì)開(kāi)發(fā)平臺(tái)QuartusII、SOPC Builder以及NiosII IDE[2] [4]。這樣,硬件電路與外設(shè)的連接,NiosII軟核的配置,C語(yǔ)言編寫(xiě)與調(diào)試可有機(jī)地結(jié)合起來(lái),大大提高了系統(tǒng)設(shè)計(jì)的效率,便于系統(tǒng)的更新與升級(jí)。

本設(shè)計(jì)即是采用Altera公司的CYCLONEII芯片EP2C35-672 FPGA實(shí)現(xiàn)基于NiosII的HDLC協(xié)議控制系統(tǒng)。在完成通信協(xié)議、保證可靠通信的前提下,最終實(shí)現(xiàn)主控機(jī)與基站終端之間實(shí)時(shí)、可靠的信息交互與監(jiān)控管理功能[1]。

二 HDLC協(xié)議說(shuō)明[3]

HDLC協(xié)議具有以下特點(diǎn):數(shù)據(jù)報(bào)文可透明傳輸;全雙工通訊;采用窗口機(jī)制和捎帶應(yīng)答;采用幀校驗(yàn)序列,并對(duì)信息幀進(jìn)行順序編號(hào),防止漏收或重收,傳輸可靠性高;傳輸控制功能和處理功能分離,應(yīng)用非常靈活。HDLC執(zhí)行數(shù)據(jù)傳輸控制功能,一般分為3個(gè)階段:數(shù)據(jù)鏈路建立階段、信息幀傳送階段、數(shù)據(jù)鏈路釋放階段。

HDLC協(xié)議以幀為基本信息單位傳輸數(shù)據(jù),無(wú)論是傳輸數(shù)據(jù)信息或是控制信息,每個(gè)幀都采用統(tǒng)一的幀格式,如圖1所示:

圖1 HDLC幀格式

1. 標(biāo)志字段(F)

HDLC協(xié)議規(guī)定,所有信息的傳輸必須以一個(gè)標(biāo)志字開(kāi)始,且以同一個(gè)標(biāo)志字結(jié)束,這個(gè)標(biāo)志字就是01111110。接收方可以通過(guò)搜索01111110來(lái)判斷幀的開(kāi)始和結(jié)束,以此建立幀同步。

2. 地址字段(A)

地址字段表示鏈路上站的地址。地址字段為8位,也可用8的倍數(shù)進(jìn)行擴(kuò)展,用于標(biāo)識(shí)接收該幀的站地址。

3. 控制字段(C)

控制字段為8位,用來(lái)表示幀類(lèi)型、幀編號(hào)以及命令、響應(yīng)等。由圖1知,由于C字段的構(gòu)成不同,可以把HDLC幀分為三種類(lèi)型:信息(I)幀、監(jiān)控(S)幀、無(wú)編號(hào)(U)幀。在控制字段中,第1位是“0”的為I幀,第1、2位是“10”的為S幀,第1、2位是“11”的為U幀。

4. 信息字段(I)

信息字段內(nèi)包含了用戶的數(shù)據(jù)信息和來(lái)自上層的各種控制信息。在I幀和某些U幀中,具有該字段。HDLC幀的信息長(zhǎng)度是可變的,其長(zhǎng)度由收發(fā)站緩沖器的大小和線路的差錯(cuò)情況決定,但必須是8bit的整數(shù)倍。它可傳送標(biāo)志字以外的任意二進(jìn)制信息。

5.幀校驗(yàn)序列字段(FCS)

幀校驗(yàn)序列用于對(duì)幀進(jìn)行CRC循環(huán)冗余校驗(yàn)。在HDLC協(xié)議中采用16位循環(huán)冗余校驗(yàn)碼進(jìn)行差錯(cuò)控制,其校驗(yàn)范圍從地址字段的第1比特到信息字段的最后1比特的序列,并且規(guī)定為了透明傳輸而插入的“0”不在校驗(yàn)范圍內(nèi)。它的生成多項(xiàng)式為g(x)=X16+X12+X5+1。

三 系統(tǒng)簡(jiǎn)介

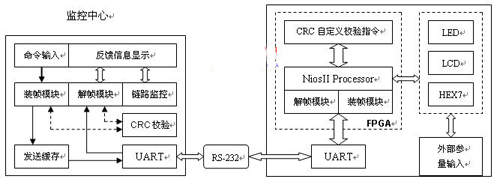

基站系統(tǒng)往往被安置在比較分散、環(huán)境比較惡劣且無(wú)人值守的地方,因此它運(yùn)行的可靠性就顯得尤為重要。SOPC的諸多特點(diǎn)滿足了此類(lèi)系統(tǒng)的要求。基于此定位,該系統(tǒng)選用pc機(jī)作為監(jiān)控中心,SOPC片上系統(tǒng)作基站端,它們之間采用HDLC協(xié)議來(lái)實(shí)現(xiàn)可靠通信。監(jiān)控中心完成建立和斷開(kāi)鏈路的功能,SOPC基站系統(tǒng)除了接收、執(zhí)行監(jiān)控中心發(fā)來(lái)的命令外,還要完成現(xiàn)場(chǎng)數(shù)據(jù)的采集控制,并將數(shù)據(jù)上傳至監(jiān)控中心。

對(duì)于通信雙方,數(shù)據(jù)都有發(fā)送與接收兩個(gè)傳輸方向,即上行數(shù)據(jù)流和下行數(shù)據(jù)流。發(fā)送數(shù)據(jù)時(shí),按照HDLC協(xié)議,先將數(shù)據(jù)封裝成幀,即加上幀頭、地址字段、控制字段、信息字段、CRC校驗(yàn)段、幀尾,當(dāng)緩沖區(qū)有空間時(shí),將成幀數(shù)據(jù)送交緩沖區(qū)待發(fā)送,數(shù)據(jù)幀再經(jīng)UART送到對(duì)方的RS-232接口,數(shù)據(jù)進(jìn)入收方的緩沖區(qū),收方則執(zhí)行與發(fā)送相反的操作,即從緩沖區(qū)讀出數(shù)據(jù)、對(duì)其解幀、CRC校驗(yàn)判斷、解碼,并按照所提取的信息執(zhí)行相應(yīng)操作。完整的系統(tǒng)總框圖如圖2所示:

圖2 系統(tǒng)框圖

四 基于NiosII的SOPC功能設(shè)計(jì)

分為硬件設(shè)計(jì)與軟件設(shè)計(jì),分別在QuartusII、SOPC Builder和NiosII IDE中完成。

1 硬件設(shè)計(jì)

(1) 硬件設(shè)計(jì)結(jié)構(gòu)

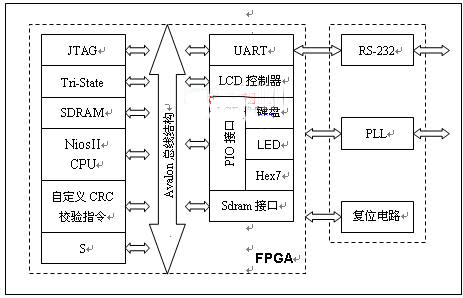

硬件設(shè)計(jì)結(jié)構(gòu)包括RS-232接口、PIO接口、顯示模塊和自定義CRC校驗(yàn)指令,這些部分都是用NiosII軟核來(lái)配置的。NiosII作為系統(tǒng)的流程控制中心,其作用是不言而喻的,通過(guò)采用SOPC Builder對(duì)NiosII進(jìn)行定制,極大的減少了系統(tǒng)的使用資源。整個(gè)系統(tǒng)硬件設(shè)計(jì)框圖如圖3所示:

圖3 NiosII硬件原理圖

(2)NiosII軟核配置

利用QuartusII軟件中的SOPC Builder,添加處理器、總線、片內(nèi)ROM、PIO、UART、NiosII其它外設(shè)及接口。系統(tǒng)的頂層模塊由NiosII軟核處理器標(biāo)準(zhǔn)版和系統(tǒng)時(shí)鐘組成,系統(tǒng)時(shí)鐘通過(guò)鎖相環(huán)PLL再分配給各外設(shè)及SDRAM。

(3)自定義CRC校驗(yàn)指令

可編程軟核處理器最大的特點(diǎn)是靈活到可以方便的增加指令,這樣可以把系統(tǒng)中用軟件處理耗時(shí)多的關(guān)鍵算法用硬件邏輯電路來(lái)實(shí)現(xiàn)。自定義指令其實(shí)就是用戶讓NiosII軟核完成的一個(gè)功能,這個(gè)功能由采用HDL語(yǔ)言描述的電路模塊來(lái)實(shí)現(xiàn),該模塊被連接到NiosII軟核的算術(shù)邏輯部件上。

CRC校驗(yàn)的一般算法需要大量的邏輯與循環(huán)運(yùn)算,如果用軟件來(lái)實(shí)現(xiàn)則要占用很多個(gè)時(shí)鐘周期,使系統(tǒng)的效率降低,而用硬件完成則僅需要幾個(gè)時(shí)鐘周期。NiosII正好提供了用戶自定義指令的功能,因此給NiosII添加自定義CRC校驗(yàn)指令來(lái)完成該部分功能,大大提高了系統(tǒng)的效率。

2 NiosII應(yīng)用軟件設(shè)計(jì)

NiosII應(yīng)用軟件用C語(yǔ)言實(shí)現(xiàn),完成了HDLC協(xié)議和對(duì)基站系統(tǒng)的控制兩個(gè)任務(wù)。首先完成HDLC協(xié)議中所要求的解幀校驗(yàn)處理、數(shù)據(jù)重新打包轉(zhuǎn)發(fā)、錯(cuò)誤處理等操作,確保通訊的暢通與可靠。基站端在接收到監(jiān)控中心的命令后,在應(yīng)用軟件的控制下,驅(qū)動(dòng)設(shè)備執(zhí)行相應(yīng)操作,主要是對(duì)溫度、濕度、電壓、煙感度等參數(shù)的讀取及環(huán)境參數(shù)的調(diào)整,執(zhí)行完畢后將結(jié)果反饋回監(jiān)控中心。基于此思想,NiosII軟件分為HDLC協(xié)議實(shí)現(xiàn)部分和命令執(zhí)行部分。

(1) 協(xié)議實(shí)現(xiàn)部分

a、接收數(shù)據(jù)

首先,建立鏈路完成對(duì)幀序列、各種外設(shè)參量、標(biāo)志位等變量的初始化。函數(shù)void DeFrame( )用于每收到一幀后的解幀處理,即包括幀長(zhǎng)度的判斷、CRC 校驗(yàn)、幀類(lèi)型辨認(rèn)、幀序號(hào)的對(duì)照。CRC校驗(yàn)碼的運(yùn)算由函數(shù)ALT_CI_CRC_CCITT( )完成,具體操作是調(diào)用配置的自定義CRC校驗(yàn)指令,賦數(shù)據(jù)值,然后通過(guò)硬件運(yùn)算返回計(jì)算的CRC碼,再和數(shù)據(jù)幀中的校驗(yàn)碼對(duì)比,相同則是正確信息,不等則判為錯(cuò)誤信息。

b、發(fā)送數(shù)據(jù)

定義變量volatile int edge_capture來(lái)進(jìn)行基站環(huán)境參數(shù)信息的捕捉,如溫度、濕度、電壓等。NiosII應(yīng)用軟件根據(jù)對(duì)環(huán)境參量的讀取和判斷,還要對(duì)異常狀況做特殊處理。比如,如果某參量出現(xiàn)超標(biāo)則必需立刻發(fā)送信息幀進(jìn)行告警,以使用戶進(jìn)行及時(shí)的調(diào)整。

具體發(fā)送時(shí),數(shù)據(jù)先裝幀再送入緩沖區(qū)等待。為了防止幀丟失造成通訊雙方處于僵滯的等待狀態(tài),引入計(jì)時(shí)器,即每發(fā)一次信息幀都要啟動(dòng)計(jì)時(shí)器進(jìn)行計(jì)時(shí),若計(jì)時(shí)器溢出,重發(fā)上一幀并重新計(jì)時(shí)。以發(fā)送電壓值為例,對(duì)其具體過(guò)程進(jìn)行說(shuō)明:

void InfoVoltageFrame( ); //裝電壓幀

void SendBuf(unsigned char Frame[],int SendDataLen); //幀送緩沖區(qū)

void TimeDelay( ); //啟動(dòng)計(jì)時(shí)器

若超時(shí),置超時(shí)標(biāo)志DelayFlag=1;

在此條件下,調(diào)用函數(shù)ReSendFrame( ); //重發(fā)上一幀

再次啟動(dòng)計(jì)時(shí)器TimeDelay( );

c、HDLC協(xié)議中滑動(dòng)窗口的處理

只將滑動(dòng)窗口協(xié)議中最關(guān)鍵的幀序號(hào)變化的具體代碼呈現(xiàn)出來(lái):

……

If ((RvByte(2) And &HF)/2)=VR Then 'NS與VR作比較,相等則接收并發(fā)送確認(rèn)幀

VR = ((VR + 1) And & H7)

……

If (RvByte(2) And &HF) = 1 Then '收到確認(rèn)S幀

SysTime.Enabled = False

VS = ((VS + 1) And & H7)

……

(2)命令執(zhí)行軟件部分

這部分軟件主要是驅(qū)動(dòng)設(shè)備執(zhí)行相應(yīng)命令。一方面,監(jiān)控中心啟動(dòng)自動(dòng)監(jiān)控功能, NiosII每隔5秒會(huì)接收到監(jiān)控中心發(fā)來(lái)的讀取參量信息命令,NiosII執(zhí)行命令并讀取外設(shè)參量送至發(fā)送緩存;另一方面,若環(huán)境參量發(fā)生變化,NiosII會(huì)對(duì)其進(jìn)行判斷,如果超標(biāo)則立即主動(dòng)發(fā)告警信息幀給監(jiān)控中心。

五 結(jié)束語(yǔ)

本文提出了一種基于FPGA的HDLC協(xié)議控制系統(tǒng)設(shè)計(jì)方案,并利用Altera公司的CYCLONEII芯片EP2C35-672來(lái)實(shí)現(xiàn)。實(shí)踐表明,利用NiosII實(shí)現(xiàn)的HDLC協(xié)議控制系統(tǒng)操作簡(jiǎn)單、使用靈活,能夠很好地應(yīng)用于各種小型通信設(shè)備。通過(guò)不同階段大量的測(cè)試,系統(tǒng)工作可靠、穩(wěn)定,完成了實(shí)時(shí)可靠的通訊與準(zhǔn)確的控制。

本文作者創(chuàng)新點(diǎn):

1、 技術(shù)手段的創(chuàng)新:使用NiosII這種新型的SOPC技術(shù)實(shí)現(xiàn)了HDLC協(xié)議。

2、 應(yīng)用領(lǐng)域的創(chuàng)新:實(shí)現(xiàn)了對(duì)基站各種信息(如工作電壓、環(huán)境溫度、濕度、煙感度等)的實(shí)時(shí)監(jiān)控與可靠管理。

參考文獻(xiàn)

1羅朝霞,張高記 基于TMS320F2407A DSP的MODBUS通信協(xié)議的實(shí)現(xiàn) 微計(jì)算機(jī)信息2005 No.20 P.138-139,

2任愛(ài)鋒,初秀琴 等.基于FPGA的嵌入式系統(tǒng)設(shè)計(jì).西安電子科技大學(xué)出版社.2004

3謝希仁.計(jì)算機(jī)網(wǎng)絡(luò)教程.人民郵電出版社.2002

4 Altera.NiosII Processor Reference Handbook.2006