評(píng)價(jià)存儲(chǔ)器的一個(gè)重要指標(biāo)就是它的可靠性,在一般的數(shù)據(jù)存儲(chǔ)中,,幾個(gè)位的錯(cuò)誤可能不是很關(guān)鍵的問題,,如果但是發(fā)生在某個(gè)敏感的數(shù)據(jù)上,這個(gè)小小的故障可能會(huì)導(dǎo)致嚴(yán)重的后果,。因此,,必須采取一些措施來及時(shí)檢出并糾正出錯(cuò)的數(shù)據(jù)。目前常用的方法有:奇偶校驗(yàn),、CRC校驗(yàn),、重復(fù)碼校驗(yàn)等。

ECC校驗(yàn)是在奇偶校驗(yàn)的基礎(chǔ)上發(fā)展而來的,,它將數(shù)據(jù)塊看作一個(gè)矩陣,,利用矩陣的行、列奇偶信息生成ECC校驗(yàn)碼,。它能夠檢測(cè)并糾正單比特錯(cuò)誤和檢測(cè)雙比特錯(cuò)誤,,但對(duì)雙比特以上的錯(cuò)誤不能保證檢測(cè)。它克服了傳統(tǒng)奇偶校驗(yàn)只能檢出奇數(shù)位出錯(cuò),、校驗(yàn)碼冗長(zhǎng),、不能糾錯(cuò)的局限性。文中在高速大容量固態(tài)存儲(chǔ)器的硬件結(jié)構(gòu)基礎(chǔ)上,,詳細(xì)介紹了ECC校驗(yàn)碼的生成規(guī)則以及ECC校驗(yàn)流程,,并用C語言和VHDL語言兩種方法實(shí)現(xiàn)了該算法。

1 存儲(chǔ)器的硬件結(jié)構(gòu)及芯片介紹

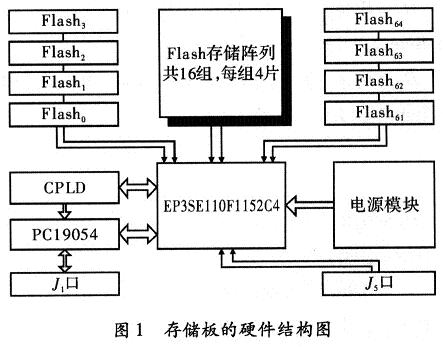

本存儲(chǔ)器是以FPGA為控制核心,,用64片F(xiàn)lash芯片構(gòu)成存儲(chǔ)陣列,,采用CPCI接口實(shí)現(xiàn)數(shù)據(jù)的高速率存儲(chǔ)。Flash存儲(chǔ)陣列分為16組,,每組4片,,每組Flash芯片共用數(shù)據(jù)和控制總線。該存儲(chǔ)器的硬件結(jié)構(gòu)圖,,如圖1所示,。

存儲(chǔ)板上的存儲(chǔ)芯片用的是Samsung公司的高速大容量固態(tài)存儲(chǔ)芯片K9W8G08U1 M Nand Flash Memory,其容量為1 G×8 bit,,分為8 192個(gè)塊,每個(gè)塊又分為64頁(yè),,1頁(yè)有(2 k+64)Byte,,其中一頁(yè)有64 bit的空閑區(qū)。存儲(chǔ)板上的控制芯片是Ahera公司的高端FPGA芯片EP3SE110F1152C4,,它負(fù)責(zé)數(shù)據(jù)的緩沖和整個(gè)存儲(chǔ)器的時(shí)序控制,,并負(fù)責(zé)以頁(yè)為單位生成校驗(yàn)碼,,并把校驗(yàn)碼存人到頁(yè)的空閑區(qū)內(nèi)。下面以1頁(yè)2 048 bit為單位介紹校驗(yàn)碼的生成以及校驗(yàn)流程,。

2 EGG算法分析及校驗(yàn)流程

2.1 EGG校驗(yàn)碼生成規(guī)則

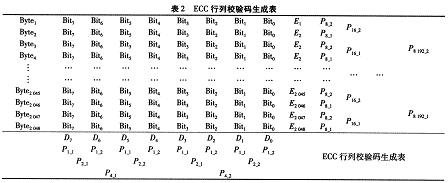

Flash在讀寫數(shù)據(jù)的時(shí)候是以頁(yè)為單位進(jìn)行的,,一頁(yè)有2 048個(gè)數(shù)據(jù),所以可以以2 048 bit為單位生成校驗(yàn)碼,。每個(gè)數(shù)據(jù)有8位信息組成,,可以把這2 048個(gè)數(shù)據(jù)看成2 048×8的矩陣,這樣就可以分別生成行校驗(yàn)碼和列校驗(yàn)碼來分別校驗(yàn),。ECC校驗(yàn)中,,每2 048個(gè)數(shù)據(jù)生成4個(gè)字節(jié)的校驗(yàn)碼,這32位的校驗(yàn)碼分成3個(gè)部分:6位的列校驗(yàn)信息,,22位的行校驗(yàn)信息,,其余的4位置1,ECC校驗(yàn)碼組成,,如表1所示,。

其中P4_l,P4_2,,P2_1,,P2_2,P1_1,,P1_2是列校驗(yàn)碼,,而P8_1,P8_2,,P16_1,,P16_2,P32_1,,P32_2,,P64_1,P64_2,,P128_1,,P128_2,P256_1,,P256_2,, P512_1,P512_2,,P1024_1,,P1 024_2, P2 048_1,, P2 048_2,, P4 096_1,,P4096_2,P8192_1,,P8192_2是行校驗(yàn)碼,。行列校驗(yàn)碼生成表,如表2所示,。

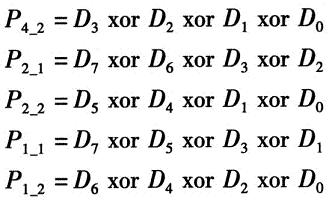

列校驗(yàn)碼生成用數(shù)學(xué)表達(dá)式表示為

![]()

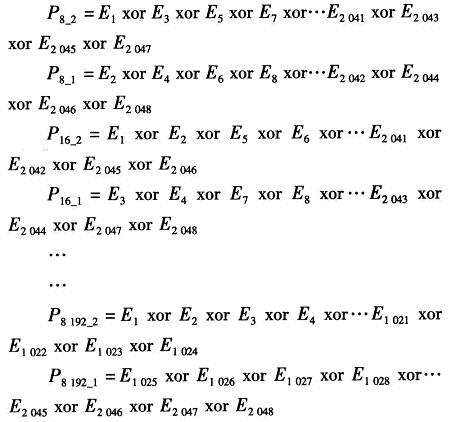

行校驗(yàn)碼生成用數(shù)學(xué)表達(dá)式表示為

這里xor表示異或操作,。

因?yàn)榘l(fā)生錯(cuò)誤的數(shù)據(jù)位在該數(shù)據(jù)塊中的字節(jié)的偏移量為

發(fā)生錯(cuò)誤的數(shù)據(jù)位在所處的字節(jié)中的位偏移量為P4_1,P2_1,,P1_1

所以根據(jù)字節(jié)的偏移量和字節(jié)中的位的偏移量即可確定該頁(yè)數(shù)據(jù)中哪一位發(fā)生了變化,。

2.2 ECC校驗(yàn)流程

當(dāng)向NAND Flash的頁(yè)中寫入數(shù)據(jù)的時(shí)候,每2 048 bit生成4 bit的ECC校驗(yàn)碼,,稱之為寫ECC校驗(yàn)碼,,保存到每一頁(yè)的空閑數(shù)據(jù)區(qū)中。

當(dāng)從NAND Flash中讀取數(shù)據(jù)的時(shí)候,,每2 048 bit生成4 bit的ECC校驗(yàn)碼,,稱之為讀ECC校驗(yàn)碼。校驗(yàn)的時(shí)候,,根據(jù)上述ECC生成原理不難推斷:將從頁(yè)空閑區(qū)中讀出的寫ECC校驗(yàn)碼和讀ECC校驗(yàn)碼按位異或,,若結(jié)果為0,則表示不存在錯(cuò),;若4 bit的異或結(jié)果中存在14 bit為1,,表示存在1 bit錯(cuò)誤,且可糾正,;若4個(gè)bit的異或結(jié)果中只存在1 bit為1,,表示空閑區(qū)中的校驗(yàn)碼出錯(cuò);其他情況均表示出現(xiàn)了無法糾正的錯(cuò)誤,,校驗(yàn)流程圖,,如圖2所示。

3 ECC算法的實(shí)現(xiàn)

3.1 C語言實(shí)現(xiàn)ECC算法

以一頁(yè)數(shù)據(jù)2 048個(gè)字節(jié)作為測(cè)試數(shù)據(jù)產(chǎn)生ECC校驗(yàn)碼,,數(shù)據(jù)是0x00~0xFF,,循環(huán)8次產(chǎn)生2048個(gè)數(shù)據(jù),數(shù)據(jù)序列,,如圖3所示,。

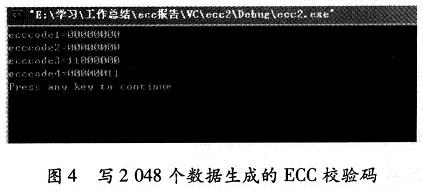

按前面的ECC校驗(yàn)碼生成規(guī)則,2 048個(gè)數(shù)據(jù)應(yīng)該生成4個(gè)校驗(yàn)碼,,生成的校驗(yàn)碼,,如圖4所示,其中ecccode1,,ecccode2,,ecccode3,ecccode4是生成的4個(gè)校驗(yàn)碼,。

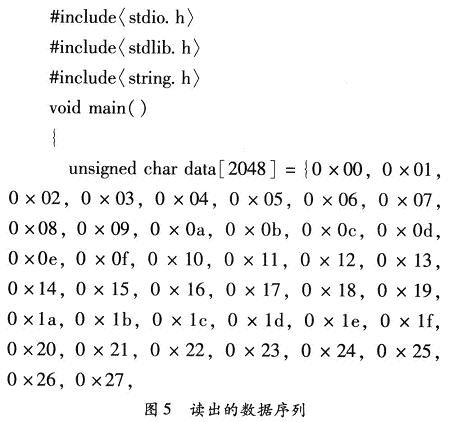

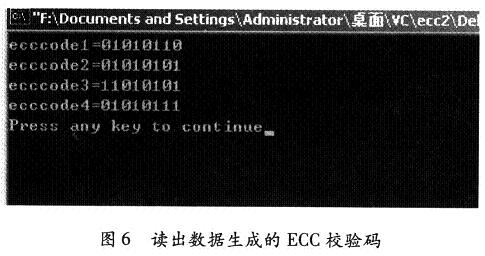

現(xiàn)在假設(shè)讀出的數(shù)據(jù)中有一位數(shù)據(jù)發(fā)生了翻轉(zhuǎn),,出現(xiàn)了一位數(shù)據(jù)錯(cuò)誤的情況,即假設(shè)數(shù)據(jù)的第2 bit的最低位發(fā)生了翻轉(zhuǎn),,0×0l變成了O×00,,此時(shí)讀出的數(shù)據(jù)序列,如圖5所示,。

3.2 利用VHDL語言實(shí)現(xiàn)EGG算法

文中以0x00~OxFF循環(huán)8次產(chǎn)生2 048個(gè)數(shù)據(jù),,利用VHDL語言編程,在QuartusII7.2下進(jìn)行了仿真,,得到了如圖7所示的校驗(yàn)碼,。其中ecccodel =00000000,ecccode2=00000000,,ecccode3=11000000,,ecccode4=000000ll是生成的4個(gè)校驗(yàn)碼,從圖中可以看到利用VHDL語言得到的校驗(yàn)碼和用C語言得到的ECC校驗(yàn)碼是相同的,。

4 結(jié)束語

文中介紹了ECC算法的一種實(shí)現(xiàn)方法,,說明了ECC的校驗(yàn)流程,最后用兩種方法實(shí)現(xiàn)ECC校驗(yàn)算法,。ECC校驗(yàn)算法簡(jiǎn)單,,軟硬件均能實(shí)現(xiàn),它能夠檢測(cè)并糾正單比特錯(cuò)誤和檢測(cè)雙比特錯(cuò)誤,,所以可以為數(shù)據(jù)存儲(chǔ)和通信系統(tǒng)提供一種強(qiáng)有力的差錯(cuò)檢測(cè)手段,。