0 引言

傳統(tǒng)數(shù)據(jù)采集卡多采用PCI或ISA總線接口,這種方式安裝麻煩、價(jià)格昂貴,且受計(jì)算機(jī)插槽數(shù)量、地址、中斷資源限制,有擴(kuò)展性差等缺點(diǎn)。而USB通用串行總線則具有安裝方便、高帶寬、易擴(kuò)展等優(yōu)點(diǎn),其中USB2.0標(biāo)準(zhǔn)具有480Mbps的最高數(shù)據(jù)傳輸率,這使USB成為本系統(tǒng)所選接口的主要類型。控制方面,傳統(tǒng)數(shù)據(jù)采集通常使用單片機(jī)或DSP作CPU來進(jìn)行控制和數(shù)據(jù)處理。其中單片機(jī)的時(shí)鐘頻率低,無法適應(yīng)高速數(shù)據(jù)采集;DSP雖能滿足速度要求,但在速度提高的同時(shí),也提高了成本。而用FPGA實(shí)現(xiàn)的SOPC則具有時(shí)鐘頻率高、內(nèi)部延時(shí)小和配置靈活等優(yōu)勢。數(shù)據(jù)顯示方面,采用虛擬儀器不但可按要求設(shè)計(jì)且變換靈活,還能執(zhí)行傳統(tǒng)儀器無法實(shí)現(xiàn)的許多功能。為此,本系統(tǒng)使用FPGA實(shí)現(xiàn)SOPC數(shù)據(jù)采集系統(tǒng),并利用Labview實(shí)現(xiàn)系統(tǒng)的顯示與控制。

1數(shù)據(jù)采集系統(tǒng)總體設(shè)計(jì)

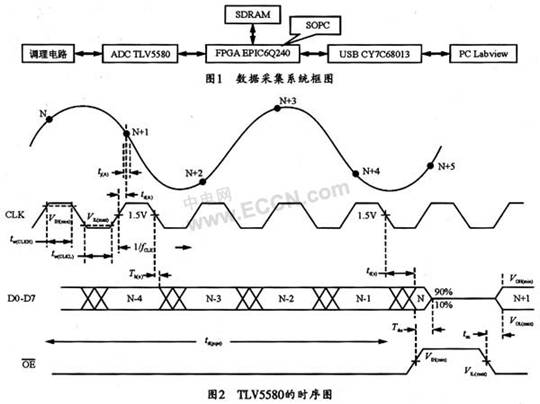

基于SOPC的高速數(shù)據(jù)采集系統(tǒng)總體框圖如圖1所示。圖中,ADC(Analog t0 Digital Converter)模數(shù)轉(zhuǎn)換器采用的是8位高速模數(shù)轉(zhuǎn)換器TLV5580。調(diào)理電路用于實(shí)現(xiàn)對(duì)輸入信號(hào)的限幅、限壓、濾波,并用增加輸入阻抗的措施來獲取預(yù)期有效信號(hào),同時(shí)保護(hù)后端AD轉(zhuǎn)換芯片。FPGA采用ALTERA公司的EPIC6Q240芯片來實(shí)現(xiàn)ADC控制及FIFO數(shù)據(jù)緩存;基于FPGA芯片的控制系統(tǒng)可直接用邏輯實(shí)現(xiàn),也可在其基礎(chǔ)上實(shí)現(xiàn)SOPC對(duì)數(shù)據(jù)的采集、傳輸?shù)目刂啤SB采用CYPRESS公司可支持USB2.0協(xié)議的高速芯片CY7C68013。FPGA可控制TLV5580的連續(xù)采樣,并將數(shù)據(jù)送到FIFO數(shù)據(jù)緩存。當(dāng)采集到一定量的數(shù)據(jù)后,CY7C68013便采用slave fifo方式將數(shù)據(jù)送給PC端,并由PC端軟件Labview實(shí)現(xiàn)的虛擬儀器進(jìn)行顯示和控制等處理。

|

2數(shù)據(jù)采集系統(tǒng)硬件設(shè)計(jì)

2.1 模數(shù)轉(zhuǎn)換器TLV5580及其控制

TLV5580是一款高速8位模擬/數(shù)字轉(zhuǎn)換器,它具有80 Msps采樣速率,是一款3.3 V工作電壓的低功耗6級(jí)流水線結(jié)構(gòu)高速A/D芯片。它的采樣信號(hào)每1個(gè)時(shí)鐘周期可通過一個(gè)STAGE,完成連續(xù)轉(zhuǎn)換到數(shù)據(jù)輸出共需6個(gè)時(shí)鐘周期。此流水線結(jié)構(gòu)由6個(gè)ADC/DAC級(jí)和一個(gè)終極快閃ADC構(gòu)成。采用A/D-D/A兩次變化以及糾錯(cuò)邏輯的目的在于進(jìn)行差錯(cuò)校正,以保證流水線上各個(gè)階段在滿操作溫度范圍下,ADC的偏移量能夠得到補(bǔ)償且不丟失代碼。TLV5580的時(shí)序圖如圖2所示。可以看出,該A/D轉(zhuǎn)換器時(shí)序簡單,容易控制。當(dāng)輸出使能(OE)為低電平時(shí),一旦數(shù)據(jù)流水線滿,其數(shù)據(jù)將在每一個(gè)時(shí)鐘周期的上升沿輸出。

2.2 USB芯片CY7C68013(FX2)

為了滿足對(duì)USB傳輸速度較高的需要,本設(shè)計(jì)選擇了Cypress公司內(nèi)置USB接口的微控制器芯片EZUSBFX2。FX2系列芯片獨(dú)特的結(jié)構(gòu)使其數(shù)據(jù)傳輸速度最高可達(dá)56Mbps,故可最大限度地滿足USB2.0的帶寬。此外,CY7C68013提供有一個(gè)串行接口引擎(SIE),可負(fù)責(zé)大部分USB2.0協(xié)議的處理工作,從而大大減輕USB協(xié)議處理的工作量,并可提供4KB的FIFO,以保證數(shù)據(jù)高速傳輸?shù)男枰Y7C68013可配置成三種不同的接口模式:Ports、GPIF Master和Slave FIFO。本項(xiàng)目采用Slave FIFO模式。在該模式下,外部邏輯或外部處理器直接連接到FX2的端點(diǎn)FIFO,因?yàn)橥獠窟壿嬁梢灾苯涌刂艶IFO,所以,F(xiàn)IFO的基本控制信號(hào)(標(biāo)志、片選、使能)均由FX2的引腳引出。其外部控制可以是同步,也可以是異步,可以使用內(nèi)部時(shí)鐘,也可以使用外部時(shí)鐘。

2.3 FPGA器件EPIC60240C6

FPGA (Field Programmable Gate Array)即現(xiàn)場可編程門陣列。本設(shè)計(jì)選用的是ALTERA公司的EPIC60240芯片,該芯片的工作電壓為1.5 V,存儲(chǔ)器密度可達(dá)5980個(gè)邏輯單元,它包含20個(gè)128x36位RAM塊,總的RAM空間達(dá)92160位,此外還內(nèi)嵌了2個(gè)鎖相環(huán)電路和一個(gè)用于連接SDRAM的特定雙數(shù)據(jù)率接口,故可支持多種不同的I/O標(biāo)準(zhǔn)。事實(shí)上,這里的FPGA除了可以直接編程以進(jìn)行邏輯控制外,也可在此基礎(chǔ)上構(gòu)建SOPC系統(tǒng),以便使用軟、硬件協(xié)同方法,與SDRAM構(gòu)成一個(gè)大容量的FIFO來對(duì)SDRAM以及MD轉(zhuǎn)換器進(jìn)行控制,同時(shí)完成與USB器件的協(xié)同工作。

2.4 SOPC及其設(shè)計(jì)

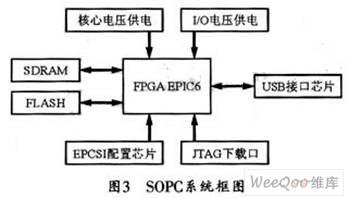

SOPC (System on a Programmable Chip)即可編程片上系統(tǒng)。它可以由單個(gè)芯片完成整個(gè)系統(tǒng)的主要邏輯功能;這種可編程系統(tǒng)具有靈活的設(shè)計(jì)方式,而且可裁減、可擴(kuò)充、可升級(jí)。本設(shè)計(jì)采用ALTERA公司率先推出的SOPC解決方案,來將處理器、存儲(chǔ)、I/O口等系統(tǒng)所需集成到一個(gè)FPGA器件上,并對(duì)其進(jìn)行軟、硬件配置,從而實(shí)現(xiàn)對(duì)數(shù)據(jù)的采集、傳輸、顯示控制。圖3所示是其SOPC系統(tǒng)框圖。

3數(shù)據(jù)采集系統(tǒng)軟件設(shè)計(jì)

本系統(tǒng)軟件包括SOPC系統(tǒng)程序、USB固件程序、驅(qū)動(dòng)程序和應(yīng)用程序等4個(gè)方面的設(shè)計(jì)。其中SOPC系統(tǒng)程序和USB固件程序是整個(gè)程序設(shè)計(jì)的核心。

3.1 SOPC系統(tǒng)程序設(shè)計(jì)

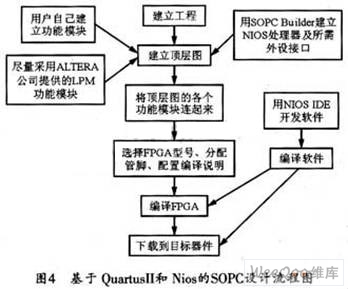

基于QuartusII和Nios的SOPC設(shè)計(jì)流程如圖4所示。

本系統(tǒng)中的SOPC系統(tǒng)軟件設(shè)計(jì)是指在FPGA中配置ALTERA公司NiosII嵌入式處理器的硬件環(huán)境。其中NiosII處理器的配置可基于QuartusII,它是ALTERA公司的大規(guī)模FPGA/CPLD開發(fā)工具。為了進(jìn)行Nios處理器的開發(fā),通常要在Quartus里裝入NiosII的軟硬件開發(fā)工具,同時(shí)在提供的開發(fā)包中使用軟件SOPC Builder開發(fā)工具加載NiosII核和外圍接口,并定義相應(yīng)的指令,然后對(duì)系統(tǒng)進(jìn)行綜合后,再下載到FPGA中,就可以完成特定功能的處理器設(shè)計(jì)。

3.2 USB固件程序設(shè)計(jì)

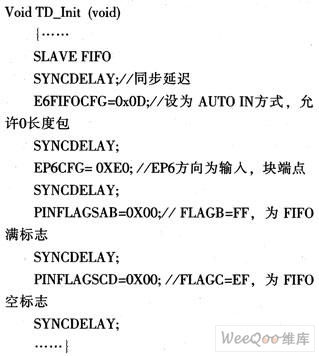

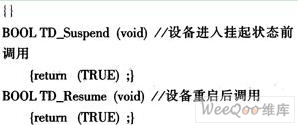

CY68013芯片的固件程序主要負(fù)責(zé)處理PC機(jī)發(fā)來的各種USB設(shè)備請(qǐng)求,并與外圍電路進(jìn)行數(shù)據(jù)傳輸。CYPRESS公司提供的固件程序框架中的兩個(gè)程序分別是FW.C和PERIPH.C。其中FW.C是固件運(yùn)行的主程序文件,負(fù)責(zé)處理各種USB設(shè)備請(qǐng)求,包含程序框架的MAIN函數(shù),它可管理整個(gè)51內(nèi)核的運(yùn)行。而對(duì)于PERIPH.C,則必須將PERIPH.C實(shí)例化,以實(shí)現(xiàn)所需的功能。固件程序中最重要的是TD_init()和TD_poll()兩個(gè)函數(shù)。TD_Init函數(shù)負(fù)責(zé)對(duì)CY7C68013的初始化,它一般在固件運(yùn)行開始時(shí)調(diào)用;TD_poll函數(shù)是數(shù)據(jù)采集的執(zhí)行子程序,它首先判斷內(nèi)部端點(diǎn)6的緩沖區(qū)和外部FIFO緩沖器是否非空,如滿足條件,則啟動(dòng)A/D轉(zhuǎn)換,并根據(jù)USB設(shè)備工作在高速和全速的不同來設(shè)置不同的傳輸計(jì)數(shù)。本設(shè)計(jì)中將接收數(shù)據(jù)端點(diǎn)6設(shè)為SLAVE FIFO模式,并使用AUTO IN模式來接收FPGA發(fā)來的數(shù)據(jù),數(shù)據(jù)流由外部FIFO控制器控制,并直接傳人端點(diǎn)6的FIFO,以等待主機(jī)提取。這里,CY7C68013僅作為數(shù)據(jù)通道,CPU不參與此過程。因此,只需在固件的初始化程序中配置好端點(diǎn)6的SLAVE FIFO接口模式,剩下的傳輸控制和其它的工作則可由FPGA來完成。以下是針對(duì)本設(shè)計(jì)的部分固件程序:

Void TD_Poll(void)//在設(shè)備運(yùn)行時(shí)反復(fù)被調(diào)用,主要完成外部FIFO狀態(tài)檢測和數(shù)據(jù)傳輸

3.3 USB驅(qū)動(dòng)程序設(shè)計(jì)

Windows下的USB驅(qū)動(dòng)程序通常由3部分組成:USB設(shè)備驅(qū)動(dòng)程序、USB總線驅(qū)動(dòng)程序和USB主控制器驅(qū)動(dòng)程序。其中,Windows操作系統(tǒng)已經(jīng)提供了處于驅(qū)動(dòng)程序棧底的USB總線驅(qū)動(dòng)程序和USB主控制器驅(qū)動(dòng)程序。而USB設(shè)備驅(qū)動(dòng)程序則要由設(shè)備開發(fā)者編寫。它應(yīng)能通過向USB總線驅(qū)動(dòng)程序發(fā)送包含URB(USB Request Block)的IRP(I/O Request Packet)來實(shí)現(xiàn)USB外設(shè)之間的信息交換。本設(shè)計(jì)采用Jungo公司的Win Driver進(jìn)行驅(qū)動(dòng)程序開發(fā),并根據(jù)Win Driver提供的驅(qū)動(dòng)向?qū)Ш陀脩粜枰瑏碜詣?dòng)生成代碼框架,從而簡化驅(qū)動(dòng)程序的開發(fā)。

3.4應(yīng)用程序設(shè)計(jì)

本設(shè)計(jì)采用NI公司的虛擬儀器(VI)開發(fā)平臺(tái)Labview來進(jìn)行應(yīng)用程序的設(shè)計(jì)。VI包括三部分:前面板、框圖程序和圖標(biāo)/連接器。其中前面板用于設(shè)置輸入數(shù)值和觀察輸出量。每一個(gè)前面板都對(duì)應(yīng)著一段框圖程序。框圖程序可用Labview圖形編程語言—G語言來編寫。圖標(biāo)/連接器是子VI可被其它Ⅵ調(diào)用的接口。圖標(biāo)是子VI在其它程序框圖中被調(diào)用的節(jié)點(diǎn)表現(xiàn)形式;而連接器則是節(jié)點(diǎn)數(shù)據(jù)的輸入/輸出口。連接器端口與前面板的控制和顯示一一對(duì)應(yīng)。

4結(jié)束語

本文介紹了一種基于SOPC和USB2.0接口的高速數(shù)據(jù)采集系統(tǒng)及其虛擬儀器的設(shè)計(jì)方法。實(shí)驗(yàn)表明,基于本設(shè)計(jì)的高速數(shù)據(jù)采集系統(tǒng)具有抗干擾、可靠性高、失碼率低等優(yōu)點(diǎn)。