摘 要: 一種針對大規(guī)模SoC設(shè)計(jì)的高效FPGA驗(yàn)證流程,分析了該流程所涉及的關(guān)鍵技術(shù):通用硬件平臺(tái)" title="硬件平臺(tái)">硬件平臺(tái)設(shè)計(jì)、FPGA軟件環(huán)境設(shè)計(jì)和軟硬件協(xié)同驗(yàn)證等。采用這些技術(shù),F(xiàn)PGA平臺(tái)可以快速且真實(shí)地模擬芯片應(yīng)用平臺(tái),從而實(shí)現(xiàn)軟硬件并行設(shè)計(jì)和協(xié)同驗(yàn)證。該驗(yàn)證流程已靈活應(yīng)用于大規(guī)模SoC項(xiàng)目設(shè)計(jì)中,大大提高了SoC產(chǎn)品的研發(fā)效率。

關(guān)鍵詞: SoC FPGA驗(yàn)證 軟硬件協(xié)同驗(yàn)證

隨著SoC(System on Chip)設(shè)計(jì)的規(guī)模不斷擴(kuò)大以及市場競爭日趨激烈,如何更快速設(shè)計(jì)出更高性能的SoC產(chǎn)品已經(jīng)成為IC設(shè)計(jì)公司能否成功的關(guān)鍵。這其中,驗(yàn)證的工作量平均占據(jù)總設(shè)計(jì)工作量的80%甚至更多,對于一個(gè)大規(guī)模SoC系統(tǒng),驗(yàn)證的效率和可靠性往往決定了項(xiàng)目的成敗。

最常用的驗(yàn)證方法是通過軟件仿真驗(yàn)證設(shè)計(jì)的功能,但由于軟件仿真速度和仿真模型" title="仿真模型">仿真模型的局限性,驗(yàn)證往往難以達(dá)到令人滿意的要求。而FPGA驗(yàn)證憑借速度和真實(shí)性的優(yōu)勢,已經(jīng)成為VLSI設(shè)計(jì)中非常重要的環(huán)節(jié)。

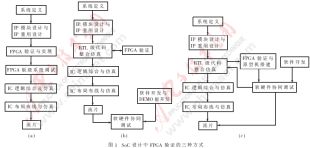

對于IC設(shè)計(jì),一般來說有三種FPGA驗(yàn)證方式,如圖1所示。

流程(a)只適用于結(jié)構(gòu)簡單且對設(shè)計(jì)周期要求不高的應(yīng)用。IC設(shè)計(jì)經(jīng)過簡單的仿真即可嘗試在FPGA上運(yùn)行,若實(shí)現(xiàn)結(jié)果真實(shí)可靠,再進(jìn)行IC后端設(shè)計(jì),然后流片。但當(dāng)芯片比較復(fù)雜時(shí),在FPGA開發(fā)板上的調(diào)試將花費(fèi)大量時(shí)間,且由于FPGA本身的局限性,并不能完美地驗(yàn)證SoC設(shè)計(jì)中的某些特殊任務(wù),如低功耗設(shè)計(jì)、多時(shí)鐘域交互、數(shù)模混和等。

對于大規(guī)模且有特殊設(shè)計(jì)要求的IC設(shè)計(jì)可采用流程(b),它要求建立一個(gè)完善的SoC軟件仿真環(huán)境,IC設(shè)計(jì)的主要功能都可以在軟件虛擬平臺(tái)上得到比較全面的驗(yàn)證。之后再把SoC設(shè)計(jì)在FPGA平臺(tái)上實(shí)現(xiàn),憑借FPGA速度快和結(jié)果真實(shí)的優(yōu)勢,可在FPGA平臺(tái)上運(yùn)行大量的測試程序,以提高驗(yàn)證的完備性。但該流程要求花費(fèi)很多經(jīng)費(fèi)和時(shí)間構(gòu)建硬件平臺(tái),并且在驗(yàn)證過程中,研究如何產(chǎn)生激勵(lì)和分析FPGA運(yùn)行情況也將花費(fèi)非常多的時(shí)間。考慮到項(xiàng)目周期和經(jīng)費(fèi)等因素,這種FPGA驗(yàn)證流程很難對SoC設(shè)計(jì)進(jìn)行徹底的驗(yàn)證。同時(shí),軟件人員必須在流片后才能在真實(shí)的環(huán)境下調(diào)試應(yīng)用程序,這也就增加了項(xiàng)目風(fēng)險(xiǎn)和研發(fā)周期。

隨著市場競爭日趨激烈,SoC設(shè)計(jì)公司越來越需要找到一種更加完備的設(shè)計(jì)與驗(yàn)證方法來提高SoC設(shè)計(jì)的效率和可靠性,驗(yàn)證流程(c)則是最好的選擇。它是一個(gè)可適應(yīng)于各種項(xiàng)目的通用的FPGA硬件驗(yàn)證平臺(tái),不必經(jīng)常重新設(shè)計(jì)硬件平臺(tái)。該平臺(tái)具有強(qiáng)大驗(yàn)證能力,可以非常真實(shí)地模擬各種SoC設(shè)計(jì)的功能和應(yīng)用平臺(tái),從而可以對其進(jìn)行全面的驗(yàn)證。該流程要求建立一個(gè)完善的FPGA綜合與仿真環(huán)境,與IC設(shè)計(jì)的環(huán)境統(tǒng)一起來,使得任何一個(gè)仿真的激勵(lì)都可以類比地在IC設(shè)計(jì)前端仿真、在IC后端仿真和在FPGA后端仿真。通過比較它們的結(jié)果,很容易地找到設(shè)計(jì)中的缺陷。這樣,整個(gè)驗(yàn)證工作都將變得輕松而且透明。

在成功建立FPGA軟硬件設(shè)計(jì)環(huán)境后,軟件研發(fā)人員就可以并行的在該平臺(tái)上開發(fā)和調(diào)試應(yīng)用軟件,并及時(shí)把系統(tǒng)級調(diào)試結(jié)果反饋到IC設(shè)計(jì)前端,這大大提高了研發(fā)效率,也非常全面地驗(yàn)證了整個(gè)IC設(shè)計(jì)。同時(shí),還可以在FPGA中加入某些監(jiān)測分析模塊,真實(shí)地反饋芯片內(nèi)部的運(yùn)行數(shù)據(jù),如處理器執(zhí)行效率、總線利用率、帶寬等,這些對SoC項(xiàng)目的決策都是至關(guān)重要的。

下面將詳細(xì)闡述通用硬件平臺(tái)建設(shè)、軟件環(huán)境建設(shè)和軟硬件協(xié)同驗(yàn)證等相關(guān)技術(shù)。

1 FPGA硬件平臺(tái)建設(shè)

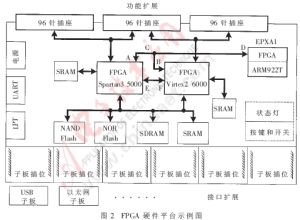

對于不同項(xiàng)目情況,F(xiàn)PGA硬件平臺(tái)建設(shè)有所不同,但主要應(yīng)考慮FPGA邏輯資源、應(yīng)用資源、擴(kuò)展能力、PCB信號質(zhì)量、易于調(diào)試、組態(tài)和成本等方面因素。下面結(jié)合項(xiàng)目實(shí)例(圖2)進(jìn)行介紹。

1.1 FPGA邏輯資源

該硬件平臺(tái)采用Xilinx公司FPGA芯片 virtex2 6000(X2V6000)和spartan3 5000(X3S5000)各一片,它們分別具有600萬門和500萬門的邏輯資源。virtex2 6000面向于高端應(yīng)用,時(shí)鐘和存儲(chǔ)資源更多、速度更快,主要用于實(shí)現(xiàn)對性能要求較高的DSP內(nèi)核;spartan3 5000具有更低的成本,用于實(shí)現(xiàn)對性能要求稍低的片上IP應(yīng)用模塊。該平臺(tái)還包含一片Altera公司的FPGA芯片EPXA1,該芯片包含ARM922T硬核,它將保證該FPGA硬件平臺(tái)能驗(yàn)證ARM+DSP等多核的SoC項(xiàng)目,也方便了驗(yàn)證和調(diào)試。

1.2 應(yīng)用資源

為了能更廣泛地適應(yīng)SoC應(yīng)用方案,兩片大容量FPGA都各自與SRAM相連,以彌補(bǔ)片內(nèi)RAM資源的不足。該硬件平臺(tái)還包含一個(gè)公共存儲(chǔ)器總線,用于連接常用的RAM和FLASH資源。這樣硬件平臺(tái)基本滿足了SoC應(yīng)用方案對存儲(chǔ)資源的需求。

1.3 擴(kuò)展能力

一個(gè)SoC的應(yīng)用方案可能用到各種特殊的資源,通用的FPGA硬件平臺(tái)應(yīng)該能承載這些資源。示例中采用了兩種擴(kuò)展方式:一種是功能擴(kuò)展,由三個(gè)96針的插座構(gòu)成,它們與FPGA的距離近、延遲小、連接FPGA的I/O" title="I/O">I/O數(shù)量多,可用于連接功能擴(kuò)展板,也可以通過該插座使兩塊FPGA板互連,使FPGA資源加倍,從而驗(yàn)證更大規(guī)模的SoC設(shè)計(jì)。另一種是接口擴(kuò)展,用于擴(kuò)展SoC的外設(shè)資源,如SoC中常用到的USB總線收發(fā)器、以太網(wǎng)控制器等,都可以單獨(dú)作為子板來擴(kuò)充,這些子板尺寸相同、引腳排列相似、且大多可采用兩層板實(shí)現(xiàn),即靈活又降低了風(fēng)險(xiǎn)和成本。

1.4 PCB信號質(zhì)量

由于FPGA具有非常多的I/O資源,使得保證PCB信號質(zhì)量成為難點(diǎn)。該硬件平臺(tái)設(shè)計(jì)為14層板,采用Cadence公司的軟件Allegro進(jìn)行PCB設(shè)計(jì),采用sigXplore進(jìn)行信號完整性分析。對各種拓?fù)淝闆r下的信號質(zhì)量仿真表明,由于FPGA自帶數(shù)控匹配電阻,兩點(diǎn)互連線可以得到較好的信號質(zhì)量,加大布線間距后,串?dāng)_也可以小到令人滿意的水平,但連接多個(gè)器件的信號反射比較嚴(yán)重。對于公共存儲(chǔ)器總線,布局時(shí)應(yīng)盡量拉近芯片間的距離,并設(shè)置最大線長約束。當(dāng)線長足夠短時(shí),經(jīng)仿真,信號質(zhì)量可以達(dá)到要求。對于三個(gè)FPGA間的互連線,由于線數(shù)非常多,很難全部縮短它們的長度,這時(shí)應(yīng)設(shè)置布線約束,如圖2,使AC與BC的距離相等,從而使A點(diǎn)和B點(diǎn)對C點(diǎn)的反射貢獻(xiàn)相同,AD或BD可以得到較好的通信質(zhì)量。然而AB間的通信質(zhì)量卻由于D點(diǎn)的反射而變得很差,但這兩塊FPGA間可以通過EF點(diǎn)來通信。這樣,三片F(xiàn)PGA間的通信就都可獲得較好的信號質(zhì)量。

綜上所述,F(xiàn)PGA硬件驗(yàn)證平臺(tái)的搭建應(yīng)根據(jù)項(xiàng)目情況有所不同,但所考慮的因素大體上可以分為以上四類,本文所提出的開發(fā)平臺(tái)示例已經(jīng)針對這四個(gè)方面提出了較好的解決方案,該硬件平臺(tái)已成功應(yīng)用于FPGA驗(yàn)證項(xiàng)目中。

2 FPGA軟件環(huán)境建設(shè)

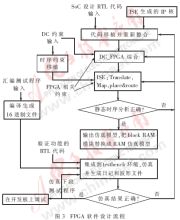

FPGA軟件環(huán)境部分的工作,不僅包括對特殊的RTL代碼及相關(guān)約束的修改,如門控" title="門控">門控時(shí)鐘處理、硬IP核替換等,還要根據(jù)特定的硬件平臺(tái),增加FPGA相關(guān)的約束,并搭建一個(gè)能夠自動(dòng)仿真和驗(yàn)證的環(huán)境。因?yàn)樵谶@一過程中RTL代碼和約束要經(jīng)過多次版本的變化,靠手工進(jìn)行維護(hù)非常容易出錯(cuò),這些錯(cuò)誤很難檢驗(yàn),甚至可能損壞開發(fā)板。所以必須建立一個(gè)足夠完善的軟件環(huán)境,能夠在人的稍微干預(yù)下,自動(dòng)完成以上處理,并易于定位錯(cuò)誤。圖3所示是FPGA軟件環(huán)境設(shè)計(jì)流程圖,下面將分類介紹搭建軟件環(huán)境的幾個(gè)重要環(huán)節(jié)。

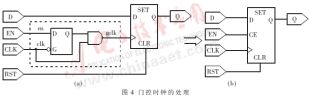

2.1 門控時(shí)鐘的處理

在SoC的設(shè)計(jì)中,經(jīng)常會(huì)用到門控時(shí)鐘。如圖4(a)所示,當(dāng)en為‘1’時(shí),時(shí)鐘clk可傳送到gclk;當(dāng)en為‘0’時(shí),gclk恒為‘0’。為了防止真實(shí)芯片中en和clk延遲差異可能造成的毛刺,該電路還需要一個(gè)latch鎖住en的狀態(tài)。對于SoC設(shè)計(jì),使用者可以根據(jù)芯片使用情況把一些不用的模塊的時(shí)鐘關(guān)閉,這大大降低了芯片的功耗。

由于FPGA芯片特定的結(jié)構(gòu),它的全局時(shí)鐘線數(shù)非常有限,并且經(jīng)過與門輸出的信號傳輸?shù)饺謺r(shí)鐘需要很大的額外延時(shí),這使得圖4(a)電路很難在FPGA中實(shí)現(xiàn)。通常的辦法是,在FPGA中采用如圖4(b)所示的電路來代替門控時(shí)鐘的功能,該電路把源時(shí)鐘clk和en信號分別接到每個(gè)觸發(fā)器端。當(dāng)en信號為‘0’時(shí),clk信號雖不停止,但觸發(fā)器并不觸發(fā),這使得該電路的功能與4(a)相同。該方法把芯片內(nèi)的時(shí)鐘線數(shù)大大縮小,使之可以采用全局時(shí)鐘線布線,這充分利用了FPGA中全局時(shí)鐘0偏斜的特點(diǎn),避免了由于時(shí)鐘線的延時(shí)所產(chǎn)生的時(shí)序問題,提高了系統(tǒng)的性能。目前,DC_FPGA綜合工具可以支持門控時(shí)鐘的自動(dòng)處理,它要求把RTL代碼中門控時(shí)鐘單元改寫成特定的風(fēng)格,并增加幾條約束語句,即可自動(dòng)實(shí)現(xiàn)如圖3所示的處理。該方法使時(shí)鐘樹非常復(fù)雜的SoC設(shè)計(jì)的FPGA驗(yàn)證變得簡單,在實(shí)用中取得了非常好的效果。

2.2 硬IP核替換與RTL重新整合

在SoC設(shè)計(jì)中,經(jīng)常會(huì)使用一些硬IP核,如PLL、SRAM、ADC、USB transceiver等,這些電路大部分屬于模擬電路,無法在FPGA中實(shí)現(xiàn)。對于PLL、SRAM等模塊,一般采用FPGA內(nèi)部的時(shí)鐘管理資源和存儲(chǔ)資源來實(shí)現(xiàn),只要在RTL調(diào)用關(guān)系上作些調(diào)整即可。對于其他硬IP核,需要在開發(fā)板上選用同樣功能的芯片,與FPGA共同實(shí)現(xiàn)它們的功能。在RTL級,首先要取消對硬IP核的調(diào)用,然后在ISE軟件約束中,把原先連接IP的信號綁定" title="綁定">綁定到FPGA的I/O上,并與功能芯片的特定信號相接。由于用于替換硬IP的資源很難做到在引腳和功能上完全一致,還需要根據(jù)具體情況對RTL代碼稍作修改。

對于多FPGA驗(yàn)證,需要把SoC設(shè)計(jì)分成幾個(gè)部分,分別在不同的FPGA上實(shí)現(xiàn)。這時(shí)主要應(yīng)考慮FPGA資源的合理利用以及功能的完整性,讓各個(gè)FPGA完成相對獨(dú)立的功能,這將簡化RTL代碼的分割,也使調(diào)試工作變得相對容易。

2.3 約束的移植

在IC的后端設(shè)計(jì)中,需要加入很多時(shí)序、功能等約束,如最大時(shí)鐘周期、false path、重命名等。這些約束在FPGA實(shí)現(xiàn)過程中也要求有效,但因FPGA工具軟件約束語法不同,需要進(jìn)行約束的移植。在漢芯的FPGA驗(yàn)證項(xiàng)目中,綜合工具DC_FPGA與DC的約束語法兼容,可以直接采用DC的約束語句。DC_FPGA綜合生成EDIF文件,在ISE下進(jìn)行布局與布線操作,這時(shí)應(yīng)采用perl語言把DC中的時(shí)序相關(guān)約束轉(zhuǎn)換成ISE的約束,這種做法減少了人為錯(cuò)誤,提高了執(zhí)行效率。

另外,還要加入FPGA的相關(guān)約束,主要包括FPGA后端布局布線策略的設(shè)置、存儲(chǔ)器初始化和I/O的綁定等約束。對于前兩種,可根據(jù)項(xiàng)目的要求和ISE的語法加入適當(dāng)約束即可。但對于I/O非常多的FPGA,I/O綁定約束靠手工維護(hù)很容易出錯(cuò),而且如果綁定到錯(cuò)誤的位置,有可能造成比較大的故障,甚至損壞硬件。這里建議在RTL級為每塊FPGA寫一個(gè)通用的頂層模塊,信號的命名與原理圖中一致,并在約束文件中綁定到正確位置,再由該頂層文件調(diào)用實(shí)際的SoC設(shè)計(jì)代碼,這種做法將會(huì)大大降低版本變更中人為出錯(cuò)的可能。

2.4 自動(dòng)仿真環(huán)境搭建

FPGA后端仿真對于檢驗(yàn)FPGA操作流程中各個(gè)步驟的正確性是至關(guān)重要的一步,沒有一個(gè)比較完善的后端仿真,SoC設(shè)計(jì)就很難成功地在FPGA平臺(tái)上實(shí)現(xiàn)。在漢芯的項(xiàng)目中,RTL代碼的前端仿真環(huán)境已經(jīng)實(shí)現(xiàn)了激勵(lì)的自動(dòng)生成與結(jié)果的自動(dòng)比對功能。如圖3所示,驗(yàn)證人員把測試各個(gè)模塊的匯編程序和RTL代碼輸入,仿真環(huán)境會(huì)自動(dòng)編譯程序并把生成的指令和數(shù)據(jù)初始化到RAM中,并開始仿真。在仿真過程中會(huì)自動(dòng)把所要求的寄存器或RAM中的內(nèi)容與正確的值相比較,并給出正確與否的結(jié)論,同時(shí)也會(huì)生成相應(yīng)的波形和日記文件以供分析。對于FPGA后端仿真環(huán)境,應(yīng)該具備前端仿真環(huán)境的驗(yàn)證功能,并且與前端仿真環(huán)境保持一致,這保證了同一個(gè)激勵(lì)程序分別在前后端的環(huán)境下仿真,可以得到相同的結(jié)果。當(dāng)出現(xiàn)不一致時(shí),比較生成的波形就很容易定位FPGA后端操作中的問題。

基于上述分析,建立FPGA后端仿真環(huán)境首先要求在FPGA后端工作的每個(gè)步驟中,從層次結(jié)構(gòu)、命名規(guī)則等方面都要與前端RTL代碼保持一致,這可以通過工具軟件中相應(yīng)的約束來實(shí)現(xiàn)。另外,仿真中要求能把匯編程序下載到片內(nèi)RAM中,而ISE軟件生成的仿真模型中,片內(nèi)RAM已經(jīng)變成了由很多塊block RAM拼成,對它們的初始化會(huì)很復(fù)雜。一個(gè)好的解決方案是在后端靜態(tài)時(shí)序分析都正確的前提下,把ISE軟件生成的仿真模型文件中的RAM替換成與前端仿真模型中的RAM相一致,這即保證了與前端一致,也方便了對其初始化和檢測內(nèi)容。

3 軟硬件協(xié)同驗(yàn)證

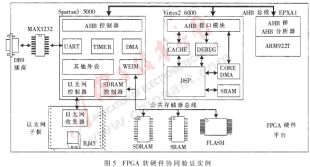

下面將結(jié)合項(xiàng)目實(shí)例介紹軟硬件協(xié)同驗(yàn)證技術(shù),如圖5所示。該項(xiàng)目采用具有10級流水線的低功耗高性能DSP核,與ARM922T構(gòu)成雙核的SoC,面向移動(dòng)平臺(tái)應(yīng)用。由于在仿真環(huán)境中難以對整個(gè)系統(tǒng)進(jìn)行充分的分析和驗(yàn)證,故將該SoC在FPGA平臺(tái)上實(shí)現(xiàn)。該平臺(tái)通過以太網(wǎng)采用DMA方式把圖像數(shù)據(jù)傳給DSP,由DSP程序?qū)崿F(xiàn)各種圖像處理的算法,并把處理結(jié)果從以太網(wǎng)傳回PC機(jī),同時(shí)通過UART報(bào)告處理進(jìn)度。利用該驗(yàn)證平臺(tái)可實(shí)現(xiàn)如下任務(wù)。

3.1 系統(tǒng)驗(yàn)證

進(jìn)一步驗(yàn)證在真實(shí)應(yīng)用情況下整個(gè)SoC設(shè)計(jì)的功能的正確性。由于ARM具有一套完善的開發(fā)工具,可以非常容易地控制它產(chǎn)生激勵(lì)并監(jiān)測DSP和外圍模塊的運(yùn)行情況。首先,通過ARM實(shí)現(xiàn)調(diào)試DSP的功能,在DSP內(nèi)部加入DEBUG模塊后,就可以通過它對DSP進(jìn)行程序下載、單步、斷點(diǎn)等功能調(diào)試。另外,還可以在ARM上運(yùn)行測試程序,把系統(tǒng)運(yùn)行到特定時(shí)間和步驟的執(zhí)行結(jié)果提取出來并自動(dòng)比較是否正確,然后把這些信息通過UART傳到PC機(jī),這將使整個(gè)系統(tǒng)的運(yùn)行完全透明。

3.2 架構(gòu)分析

對于一個(gè)SoC設(shè)計(jì),架構(gòu)的設(shè)計(jì)是至關(guān)重要的,它要求根據(jù)SoC具體應(yīng)用情況對芯片的功耗、帶寬、成本等多方面因素進(jìn)行折中,超過實(shí)際需要的性能或帶寬將會(huì)帶來成本和功耗的增加,這些都將影響產(chǎn)品的市場競爭力。通過加入一些特定的分析監(jiān)測模塊,就可以在FPGA平臺(tái)上更加容易地分析系統(tǒng)架構(gòu)的性能。如圖5所示,AHB分析器可以把AHB總線上的主從設(shè)備的切換頻率和效率、最大總線利用率等細(xì)節(jié)情況真實(shí)地反饋到PC機(jī),為SoC架構(gòu)的分析提供非常真實(shí)的資料。

3.3 軟件優(yōu)化與分析

對于一個(gè)SoC平臺(tái)系統(tǒng),軟件的設(shè)計(jì)與優(yōu)化也是非常重要的。在FPGA平臺(tái)上有上述提到的多種手段監(jiān)控和分析軟件運(yùn)行情況,這樣可以更好地優(yōu)化軟件,發(fā)揮SOC平臺(tái)的最大潛力。還可以通過分析不同功能的應(yīng)用軟件對系統(tǒng)帶寬和處理能力的真實(shí)需求,研究增加硬件協(xié)處理功能的可行性和必要性,做到真正的軟硬件協(xié)同設(shè)計(jì)與驗(yàn)證。

上述SoC項(xiàng)目實(shí)例已在FPGA開發(fā)板上實(shí)現(xiàn),成功地運(yùn)行了小目標(biāo)檢測等多個(gè)圖像處理程序,并實(shí)時(shí)反饋了DSP指令流水中斷、DMA數(shù)據(jù)搬移、AHB總線競爭等許多芯片運(yùn)行情況的信息。其中,基于對AHB總線競爭信息的分析,優(yōu)化了軟件的數(shù)據(jù)調(diào)度機(jī)制,同時(shí)改進(jìn)了總線仲裁機(jī)制,切實(shí)地提高了AHB總線的數(shù)據(jù)吞吐率。

參考文獻(xiàn)

1 Hauck S, Borriello G.Pin Assignment for Multi FPGA Sys-tems.IEEE Transactions on Computer-aided Design of Integ-rated Circuit and Systems, 1997;16(9)

2 Gschwind M. FPGA Prototyping of a RISC Processor Core for Embedded Applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2001;9(2)

3 Synopsys. Design Compiler FPGA user guide. CA: Synopsys Inc., Mar., 2004

4 Synopsys. VCS user guide. CA: Synopsys Inc., Sep., 2003