“軟”控制器是一個在FPGA的可編程結(jié)構(gòu)中實(shí)現(xiàn)的處理器、存儲器和外設(shè)的平臺。過去,現(xiàn)成的微控制器的價格大大低于軟處理器的價格。如今隨著90納米或采用更小工藝的最新低成本現(xiàn)場可編程門陣列(FPGA)的出現(xiàn),它們的整體成本已具有可比性。設(shè)計(jì)人員可以對軟微控制器進(jìn)行調(diào)整,以便符合目標(biāo)應(yīng)用所需的功能和性能。有些通用微控制器附加了一些不必要的功能,與這些通用微控制器相比較,使用軟微控制器可能會導(dǎo)致更低的成本。因此,對成本敏感的應(yīng)用,如那些針對消費(fèi)產(chǎn)品的設(shè)計(jì),現(xiàn)在用軟微控制器是一個可行的辦法。已經(jīng)證明,低成本FPGA是一種節(jié)省成本的解決方案,因?yàn)樗鼈兛梢匀〈罅康钠骷H绻O(shè)計(jì)中已使用了FPGA ,微控制器可集成到這個FPGA之中,節(jié)省了使用分立元件或一個額外FPGA 的成本。

LatticeMico32微控制器

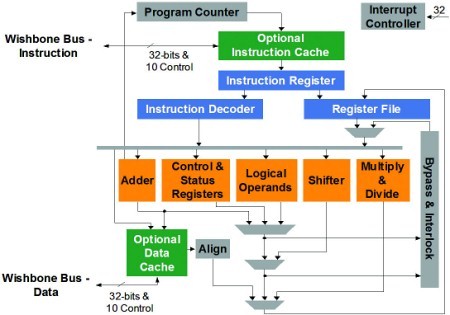

萊迪思的軟微控制器的核是LatticeMico32處理器。LatticeMico32是采用哈佛存儲器架構(gòu)的RISC設(shè)計(jì)。哈佛架構(gòu)允許執(zhí)行單周期指令,因?yàn)樵试S同時訪問獨(dú)立的32位指令和數(shù)據(jù)總線。LatticeMico32有32個通用寄存器,可處理多達(dá)32個外部中斷。有兩個可選方法來改善吞吐量,以避免Wishbone總線訪問指令和數(shù)據(jù)存儲器。第一種方法是使用高速緩存(圖1 ) 。第二種方法是使用“內(nèi)聯(lián)”存儲器(圖中未顯示) 。內(nèi)聯(lián)存儲器是直接與指令和/或數(shù)據(jù)流水線相連的存儲器,而不是通過WISHBONE 來訪問。這兩種方法可在一起使用。圖1中突出展示了這些特點(diǎn),并展示了一些其它元件。

|

|

圖1 LatticeMico32的結(jié)構(gòu)圖 |

為了加快微控制器平臺的開發(fā),幾個外圍元件可與LatticeMico32微處理器一起使用。通過Wishbone總線接口把這些元件連接到處理器,這是一個由OpenCores組織制定的免費(fèi)開放協(xié)議。通過使用這個開放源總線接口,用戶可以把自己的WISHBONE元件放入其嵌入式設(shè)計(jì)。

除了外設(shè)可用Wishbone總線之外, 還可以構(gòu)建一個總線互連結(jié)構(gòu), 這樣不但能使元件之間能夠互相通信, 而且還可以進(jìn)行調(diào)整,從而滿足了系統(tǒng)的吞吐量需求。

設(shè)計(jì)流程

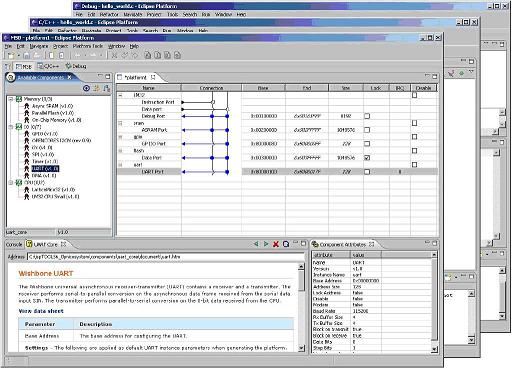

LatticeMico32 System軟件開發(fā)工具提供了一個快速簡便的方法來實(shí)現(xiàn)微控制器設(shè)計(jì)。包括從微控制器的定義到軟件的開發(fā)和調(diào)試。該工具基于Eclipse C / C + +開發(fā)工具( CDT )環(huán)境,這是一個業(yè)界標(biāo)準(zhǔn)的開放源代碼軟件開發(fā)架構(gòu)(圖2 )。

圖2 易于使用的圖形用戶界面開發(fā)工具

LatticeMico32 System有3個集成工具:

MicoSystem Builder (MSB)

MSB生成微控制器的結(jié)構(gòu),以及針對硬件實(shí)現(xiàn)的相關(guān)硬件描述語言(HDL)代碼。設(shè)計(jì)者可以選擇外圍元件,把它們連接到微處理器,并指定它們之間的連接。其它工具要使用微控制器的結(jié)構(gòu)信息,以便使代碼完全針對微控制器。例如,UART可移入微控制器的存儲器空間(從而更新微控制器的結(jié)構(gòu)) ,針對這一更新微控制器的軟件將通過新的空間來訪問UART。MSB還能構(gòu)建處理器(和其它主元件,如DMA )和從外設(shè)之間的互連,從外設(shè)用來調(diào)整吞吐量的需求。例如,當(dāng)多個主元件與不同的外設(shè)通信時,多個主元件可以共享一個總線來訪問所有的外設(shè)。或者每個主元件可以直接以非共享的形式訪問任何一個外設(shè),該外設(shè)只與那個主元件通信。這需要用更多互連的總線,但允許兩個主元件同時訪問不同的外圍設(shè)備。最合適的總線互連將取決于該系統(tǒng)的通信模式和吞吐量的需求。

C/C++軟件項(xiàng)目環(huán)境(SPE)

C / C + + SPE是一個集成的軟件開發(fā)環(huán)境。它包括一個制作系統(tǒng),針對用MSB構(gòu)建的某一微控制器、調(diào)用編譯器、匯編器和創(chuàng)建代碼的連接器。

調(diào)試器

C / C + +源代碼級調(diào)試器提供了軟件調(diào)試功能,調(diào)試可以是源代碼級或匯編級,這些代碼在軟微控制器/ FPGA中運(yùn)行。支持標(biāo)準(zhǔn)的調(diào)試任務(wù),如設(shè)置斷點(diǎn)、步進(jìn),并允許用戶觀察處理器中的寄存器和存儲器的狀態(tài)。

Reveal硬件調(diào)試器

Reveal硬件調(diào)試器是一個片上調(diào)試器,它有別于LatticeMico32軟件調(diào)試器。然而,LatticeMico32調(diào)試器能深入觀察微控制器的狀態(tài)(如寄存器,存儲器的內(nèi)容) ,而Reveal則能夠深入觀察硬件。有了Reveal,用戶可以“跟蹤”任何一組設(shè)計(jì)信號。當(dāng)啟動和停止跟蹤時,可設(shè)定復(fù)雜跟蹤觸發(fā)條件來加以控制。調(diào)試一個含有軟微控制器的系統(tǒng)時,可將Reveal和LatticeMico32調(diào)試器一起使用,這樣就有了高度的可見性和可用性。

支持Windows和Linux的工具鏈提供以下幾個方面的支持:

- 小型的C庫

- 自動和用戶定義制作

- 應(yīng)用到非易失性存儲器(如SPI閃存 )

操作系統(tǒng)

LatticeMico32支持以下操作系統(tǒng):

- 源于奧地利Theobroma Systems的uClinux 和U-Boot

- 源于Micriμm的µC/OS-II RTOS

- TOPPERS/JSP的µITRON RTOS

資源利用率和性能

LatticeMico32具有很高的性能并占用最小的資源。對那些關(guān)心資源的設(shè)計(jì)者來說,基本配置不使用指令或數(shù)據(jù)高速緩存、單周期移位器,也沒有乘法器。對于那些更加關(guān)心性能的設(shè)計(jì)人員而言,全面配置使用8K字節(jié)指令高速緩存、8K字節(jié)的數(shù)據(jù)高速緩存、3個周期的移位器和乘法器。對需要考慮折衷方案的用戶,標(biāo)準(zhǔn)配置類似于全面配置,但沒有8K字節(jié)的數(shù)據(jù)高速緩存。

開放源代碼方法

在各種軟件領(lǐng)域,開放源代碼越來越受歡迎了,并已被臺式機(jī)/服務(wù)器軟件所接受。采用開放源代碼IP的好處包括更多的可見性、更大的靈活性,以及提高可移植性。

開放源代碼能夠觀察微處理器的細(xì)節(jié)。通過訪問源代碼,設(shè)計(jì)人員對這個核的細(xì)節(jié)會有一個全面的了解。此外,開放源碼對這個IP提供了更大的靈活性,并且對每個人都開放,因此設(shè)計(jì)人員可以對它進(jìn)行核查,并對此IP作出改進(jìn)。這種采用開放源代碼的方法使整個用戶群體幫助查明問題所在,并制定解決方案。這意味著,不僅允許用戶修改源代碼,還鼓勵他們這樣做。這種用戶群體相互促進(jìn)導(dǎo)致開放源代碼的IP往往比傳統(tǒng)的專有IP更加穩(wěn)健和可靠。最終,開放源碼提供了改進(jìn)的可移植性。用戶贊賞獨(dú)立的架構(gòu),因?yàn)橐粋€開放源代碼的IP核可用于任何FPGA ,甚至可以遷移到一個更高批量,成熟設(shè)計(jì)的ASIC中。獨(dú)立的架構(gòu)是很有價值的,因?yàn)樗軌虼_保在最后一分鐘對器件做出修改的情況。應(yīng)該認(rèn)識到,開放源代碼IP最常見的好處是:它是免費(fèi)的。