引言

隨著集成電路的發(fā)展,利用大規(guī)模集成電路來(lái)完成各種高速、高精度電子儀器的設(shè)計(jì)已經(jīng)成為一種行之有效的方法。采用這種技術(shù)制成的電子儀器電路結(jié)構(gòu)簡(jiǎn)單、性能可靠、測(cè)量精確且易于調(diào)試。本文采用Altera CycloneII系列FPGA器件EP2C5,設(shè)計(jì)了高精度相位測(cè)量?jī)x。測(cè)量相位差所需的信號(hào)源在FPGA內(nèi)部運(yùn)用DDS原理生成,然后通過(guò)高速時(shí)鐘脈沖計(jì)算兩路正弦波過(guò)零點(diǎn)之間的距離,最后通過(guò)一定的運(yùn)算電路得到最終相位值,測(cè)相精度為1°。

系統(tǒng)硬件設(shè)計(jì)

該基于FPGA的相位測(cè)量?jī)x,硬件組成包括FPGA、高速DAC以及電壓比較器等部分。其系統(tǒng)硬件結(jié)構(gòu)如圖1所示。

圖1 相位測(cè)量?jī)x硬件結(jié)構(gòu)圖

該測(cè)量?jī)x由按鍵來(lái)預(yù)置正弦波的頻率及相位。通過(guò)FPGA內(nèi)部的控制模塊來(lái)計(jì)算并產(chǎn)生正弦波所需的頻率控制字和相位控制字,然后將控制字輸入DDS模塊以產(chǎn)生波形數(shù)據(jù)輸出,經(jīng)10位高速DAC THS5651輸出兩路正弦波。在測(cè)相位差時(shí),將圖1中移相正弦波輸出分為兩路,其中一路直接經(jīng)電壓比較器LM311整形后輸入測(cè)相模塊;另外一路先通過(guò)被測(cè)電路,然后再經(jīng)電壓比較器整形后輸入測(cè)相模塊,從而得到正弦波經(jīng)被測(cè)電路后產(chǎn)生的相移。

基于FPGA的硬件電路設(shè)計(jì)

DDS移相信號(hào)源設(shè)計(jì)

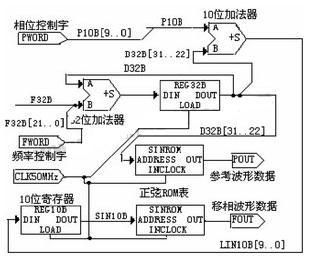

DDS的基本原理是利用采樣定理,通過(guò)查表法產(chǎn)生波形,本系統(tǒng)的移相信號(hào)發(fā)生模塊如圖2所示。

圖2 基于DDS的數(shù)字移相信號(hào)發(fā)生模塊框圖

圖2中,加法器與寄存器級(jí)聯(lián)構(gòu)成相位累加器。通過(guò)時(shí)鐘脈沖觸發(fā)相位累加器,從而將頻率控制字不斷累加。相位累加器產(chǎn)生一次溢出,就完成一次周期性的動(dòng)作,這個(gè)周期就是DDS合成信號(hào)的一個(gè)頻率周期。

用相位累加器輸出的數(shù)據(jù)作為波形存儲(chǔ)器的相位取樣地址,把存儲(chǔ)在波形存儲(chǔ)器內(nèi)的波形抽樣值經(jīng)查找表查出,從而完成相位到幅值的轉(zhuǎn)換。然后將波形存儲(chǔ)器的輸出送到DAC,通過(guò)DAC將數(shù)字量形式的波形幅值轉(zhuǎn)換成合成頻率的模擬波形。

圖2中FWORD是10位頻率控制字;PWORD是10位相移控制字,用來(lái)控制正弦信號(hào)輸出的相移量;SINROM用來(lái)存放正弦波數(shù)據(jù),有10位數(shù)據(jù)線和10位地址線。其中數(shù)據(jù)文件是MIF文件(數(shù)據(jù)深度1024,數(shù)據(jù)類型為10進(jìn)制數(shù)),可由Matlab生成,存放數(shù)據(jù)的單元采用定制ROM的方法生成;POUT和FOUT都為10位輸出,分別和兩個(gè)高速DAC THS5651相連。

控制模塊的生成

在產(chǎn)生波形的過(guò)程中,DDS模塊所需的頻率和相位控制字由在FPGA內(nèi)部編寫的控制模塊來(lái)給定。控制模塊的頂層原理框圖如圖3所示。

& nbsp; 圖3 控制模塊頂層原理框圖

圖3中,B1、C10、D100、P1K分別為頻率步進(jìn)輸入端;Re為復(fù)位端;PW1、PW10分別為1 10南轡徊澆淙搿F渲衒bcout為頻率控制字計(jì)算模塊,完成由頻率步進(jìn)值到二進(jìn)制頻率控制字的轉(zhuǎn)換。

cout360為相位輸入計(jì)算模塊,由相位輸入端的脈沖輸入計(jì)算出實(shí)際的移相值(0麀359 )。add_data_rom是存放相位控制字的ROM,其數(shù)據(jù)文件是MIF文件,內(nèi)部360個(gè)地址值分別對(duì)應(yīng)0麀359南轡 ,每個(gè)地址中的數(shù)據(jù)為每個(gè)相位值對(duì)應(yīng)的正弦波ROM的地址值。由于正弦波ROM將一個(gè)波形分成了1024個(gè)點(diǎn),則0麀359南轡恢刀雜α薙INROM中的360個(gè)點(diǎn)。考慮到1024/360=2.84非整,為了減小移相誤差,提高移相精度,本設(shè)計(jì)中采用分段處理的方法,將360個(gè)地址分成60組。第15、30、45、60組的6個(gè)地址中點(diǎn)與點(diǎn)之間的距離都為3;其余各組前5點(diǎn)之間的點(diǎn)距為3,第5點(diǎn)與第6點(diǎn)之間的點(diǎn)距為2。

相位測(cè)量模塊設(shè)計(jì)原理

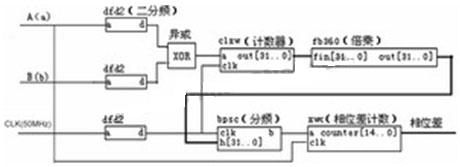

本系統(tǒng)的相位測(cè)量采用由高速時(shí)鐘脈沖測(cè)量?jī)陕凡ㄐ芜^(guò)零點(diǎn)之間距離的方法。相位測(cè)量模塊原理框圖如圖4所示。

圖4 相位測(cè)量模塊原理框圖

圖4中,A、B為兩路方波輸入,CLK為50MHz時(shí)鐘輸入,dfd2塊為下降沿觸發(fā)的2分頻模塊。A、B經(jīng)2分頻的目的是使測(cè)相范圍由0麀180┐蟮 0麀360OR為異或門,其輸出信號(hào)的脈寬為(b-a)。clxw為一高速計(jì)數(shù)器,通過(guò)25MHz的高頻時(shí)鐘來(lái)計(jì)算(b-a)的長(zhǎng)度。fb360模塊為倍乘模塊,主要完成(b-a)×360的運(yùn)算。bpsc模塊為分頻模塊,將25MHz的時(shí)鐘信號(hào)進(jìn)行(b-a)×360倍的分頻,使其輸出信號(hào)脈寬為Tclk×(b-a)×360(Tclk為25MHz的時(shí)鐘周期)。xwc為相位差計(jì)數(shù)模塊,通過(guò)A相輸入脈沖,計(jì)算Tclk×(b-a) ×360的長(zhǎng)度,然后完成(b-a)×360/a的計(jì)算,進(jìn)而得出相位差值輸出,同時(shí)該模塊還將測(cè)得的相位差值送到數(shù)碼管顯示。

在對(duì)該模塊進(jìn)行仿真時(shí),人為設(shè)定了頻率為10KHz,相位差為72。

系統(tǒng)驗(yàn)證調(diào)試

在整個(gè)系統(tǒng)的驗(yàn)證中,由外部按鍵通過(guò)控制模塊來(lái)設(shè)定波形的頻率和相位值,并通過(guò)將DDS模塊的輸出端FOUT和POUT外接10位DAC THS5651來(lái)產(chǎn)生波形。通過(guò)在示波器觀察兩路波形發(fā)現(xiàn),波形比較穩(wěn)定,頻率與設(shè)定值一致。此外,為了測(cè)量DDS模塊產(chǎn)生的移相是否正確,還人為的通過(guò)相位輸入端設(shè)定相移值,并將參考波形輸出端和移相輸出端輸出的波形經(jīng)整形后,用測(cè)相模塊測(cè)量?jī)陕凡ㄐ蔚南辔徊睿ㄟ^(guò)硬件調(diào)試發(fā)現(xiàn)測(cè)得的相位差與設(shè)定的相位差完全一致,從而證明了該系統(tǒng)是精確、穩(wěn)定的。

結(jié)語(yǔ)

本系統(tǒng)選用Altera公司的quartusII4.1作為硬件開發(fā)平臺(tái),并采用VHDL語(yǔ)言進(jìn)行電路設(shè)計(jì)。在設(shè)計(jì)中按功能劃分模塊,方便了調(diào)試與修改,且易于升級(jí)。同時(shí),系統(tǒng)設(shè)計(jì)中還較多采用了同步時(shí)序電路來(lái)實(shí)現(xiàn)各個(gè)進(jìn)程模塊的功能,從而有效避免了電路毛刺現(xiàn)象。此外,在相位測(cè)量模塊中,相位差計(jì)數(shù)塊還帶有鎖存功能,從而有利于輸出的相位差值顯示穩(wěn)定。