摘 要:借助EDA工具軟件設(shè)計了一個邏輯控制部件,解決了CPU尋址空間不足、接口功能不全等問題。此基于CPLD的可重構(gòu)硬件數(shù)字平臺具有可移植性,使CPU對外接器件近似透明,在更換其他類型CPU后,僅做少量軟件和硬件修改即可升級成為新系統(tǒng)。

關(guān)鍵詞:CPLD 可重構(gòu) 地址擴展" title="地址擴展">地址擴展 串并轉(zhuǎn)換

現(xiàn)代電子儀器系統(tǒng)的多功能化、智能化程度不斷增加,并且隨著實際應(yīng)用場合的改變,隨時都有可能要求對系統(tǒng)功能進行升級,因此在硬件設(shè)計上越來越要依靠EDA輔助設(shè)計手段。本文主要討論了基于CPLD的電子秤" title="電子秤">電子秤邏輯控制電路設(shè)計,重點介紹CPU地址空間擴展問題,解決了熱敏打印機驅(qū)動設(shè)計及其他接口設(shè)計問題。

1 系統(tǒng)組成及設(shè)計指標

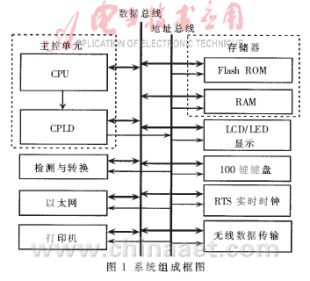

本文所設(shè)計的電子秤系統(tǒng)包括主控單元、存儲器、鍵盤顯示、檢測與轉(zhuǎn)換、數(shù)據(jù)傳輸與通信、打印以及系統(tǒng)時鐘等硬件模塊,圖1所示為系統(tǒng)組成框圖。由于采用了CPU和CPLD協(xié)同控制的設(shè)計方案,硬件模塊間的關(guān)聯(lián)性高,電路元器件數(shù)量少,對系統(tǒng)EMC有明顯改善,更為重要的是符合嵌入式軟件的設(shè)計理念,對系統(tǒng)實時操作系統(tǒng)的移植、管理大有裨益。它除了計量、打印等一般功能外,還具備良好的用戶/客戶LCD中文圖形人機接口界面、以太網(wǎng)遠程控制與數(shù)據(jù)傳輸、C-S無線數(shù)據(jù)傳輸?shù)裙δ埽僮骱唵沃庇^,擴展、升級更新迅速方便,在不改變控制系統(tǒng)的前提下,更改CPU方案也很方便,如改成DSP/ARM方案。

系統(tǒng)功能與設(shè)計指標為:最小稱重5g;2MB Flash存儲器,128KB帶電電池保護RAM;128×64點陣LCD顯示界面,100鍵鍵盤,46位客戶LED;10MHz以太網(wǎng)通信接口;905MHz智能信道掃描無線通信接口;精工高速熱敏打印機等。

2 主控單元

主控單元的功能是控制整個電子秤系統(tǒng)的運行狀態(tài)、協(xié)調(diào)各個功能模塊的關(guān)系以及處理過程信息等,主要包括改進型51核單片機" title="單片機">單片機和CPLD兩部分。

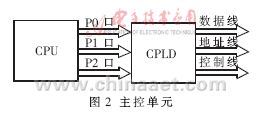

采用單片機作為主控CPU主要是從產(chǎn)品成本考慮的。很多新型MSC51核單片機不但軟件、硬件與傳統(tǒng)的MCS51系列單片機完全兼容,并且在速度、抗干擾性能、穩(wěn)定性以及性價比等方面較后者具有明顯優(yōu)勢。圖2中CPU采用SST89E58,它與8位標準51系列單片機完全兼容,工作頻率0~40MHz,工作電壓范圍2.7V~5.5V,其Super Flash存儲結(jié)構(gòu)等先進特性可以為用戶提供極高的可靠性和極低的成本。該單片機與CPLD結(jié)合,可以建立功能強大的商用電子秤操作、控制平臺。

商用電子秤的性能要求決定了硬件設(shè)計的復雜性。本文用CPLD搭建了可重構(gòu)數(shù)字平臺作為邏輯控制部件,所有時序控制、地址分配全部交給CPLD完成,用來代替?zhèn)鹘y(tǒng)的低密度AISC器件,充分發(fā)揮CPLD的優(yōu)勢,使CPU對外接器件近似透明,從而可以專注于過程信息的處理,不過多參與硬件控制。圖2中CPLD采用1片Altera公司MAX7000系列CPLD EPM7256AET144-7,該芯片有144個引腳,能夠解決包括存儲器訪問、鍵盤掃描、顯示等功能模塊的控制和驅(qū)動問題,用單片器件實現(xiàn)了CPU與所有外圍設(shè)備的邏輯接口,使得整個操作控制系統(tǒng)的主板面積大為縮減,整體性能穩(wěn)定性大為提高。在CPLD中實現(xiàn)的功能模塊有:地址譯碼、打印機驅(qū)動、PWM調(diào)制轉(zhuǎn)換等部分。為提高開發(fā)效率,減少調(diào)試中的不可預測問題,采用分級、分步驟設(shè)計方法,設(shè)計一部分,調(diào)試一部分。

3 接口邏輯與地址分配

商用電子秤的應(yīng)用環(huán)境決定了它所需要的外擴端口資源多、存儲器容量較大,因此在邏輯設(shè)計中,地址分配與管理問題就顯得特別重要。

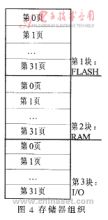

首先,由于單片機64KB的尋址范圍無法覆蓋2MB存儲空間,本文采用了分塊-分頁的方法管理存儲器:將P1與P2/P0口一起作為地址線使用,使總的地址線達到24條,CPU的有效尋址空間高達16MB單元。同時,這16MB空間被進一步平均劃分成8個塊,每塊分32頁,每頁64KB。其中P1.5-P1.7線作為塊尋址線,分別供Flash、RAM、I/O" title="I/O">I/O口使用;P1.0-1.4線作為頁尋址線,剛好生成32個有效頁地址;P2/P0作為單片機默認的地址總線,用來尋址每頁內(nèi)連續(xù)的64KB存儲單元。尋址實現(xiàn)方法:每尋址一個單元,單片機分兩次送出地址號,第1次從P1口送出塊/頁地址號,第2次從P2/P0口送出頁內(nèi)地址號。塊地址不能直接送給目標器件,而是經(jīng)過CPLD譯碼后送給對應(yīng)器件,如圖3所示。顯然,P0口仍舊復用為數(shù)據(jù)總線和低8位地址總線,P0口數(shù)據(jù)經(jīng)過CPLD鎖存后作為低8位地址給存儲器使用,而P0口直接引出的數(shù)據(jù)線并接到所有器件的數(shù)據(jù)線上。CPU工作于40MHz時鐘頻率,中和每次尋址送兩次地址對速度帶來的影響。

其次,由于單片機的P1口已被擴展為地址線,而P3口又只能用其第二功能,故已再無其他端口線可以用作通用I/O控制線。為此,本文采用I/O口統(tǒng)一尋址方式,除了存儲器以外的器件全部安排在I/O尋址空間,所有數(shù)據(jù)(包括串行通信中的串-并轉(zhuǎn)換結(jié)果)都經(jīng)過CPLD緩存之后再送入CPU中,所有存儲器及外部I/O端口統(tǒng)一分配地址:第1塊A00000H~BFFFFH地址分配給FLASH使用,第2塊C00000H~C1FFFFH地址分配給RAM使用,第3塊分配給其他并接在I/O總線上的所有端口使用。存儲器組織結(jié)構(gòu)如圖4所示。

4 打印機驅(qū)動設(shè)計

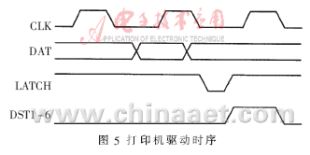

打印機是商用電子秤不可或缺的部件之一。熱敏打印的原理是在控制邏輯的驅(qū)動下,通過控制打印頭上排成方陣或條形式的微型發(fā)熱器加熱熱敏紙使之產(chǎn)生一個與加熱元素相同的圖元,同時還控制進紙,以便印出整個圖形(如銷售商品條形碼)。本文選用精工熱敏打印機LTP1245,每一行384個加熱點,最寬打印48mm寬帶紙,打印加熱電壓范圍4.2~8.5V,電源設(shè)計方便。為了減少打印電流,將每行分成六段,每段64點,分六次打印,其工作時序見圖5。CLK是移位時鐘信號,DAT是打印位數(shù)據(jù),LATCH是數(shù)據(jù)鎖存信號,DST是段控制信號。

打印數(shù)據(jù)在CLK時鐘控制下從串行數(shù)據(jù)線DAT腳逐位輸入打印機內(nèi),而后在LATCH鎖存信號控制下保存在打印存儲器中。數(shù)據(jù)全部鎖存到數(shù)據(jù)存儲器之后,在DST1-DST6信號的控制下分6次加熱打印。當某路DST信號有效時,對應(yīng)段被加熱打印。384個數(shù)據(jù)位恰好對應(yīng)384個加熱點,當該位為0時不加熱,打印紙上對應(yīng)位置顯白色,反之紙顯黑色。打印加熱時間由DST的持續(xù)時間控制,持續(xù)時間可以控制打印圖形對比深度。根據(jù)圖5中時序,結(jié)合上述設(shè)計思想,在CPLD中抽象出功能圖如圖6,Buffer1緩存步進電機驅(qū)動信號,驅(qū)動打印頭四相精密步進電機,Buffer2緩沖打印頭過熱和缺紙傳感信息。Buffer1的數(shù)據(jù)從P0口寫入,Buffer2的數(shù)據(jù)被P0口讀入。DECODER是譯碼器,譯出6位打印機段加熱控制信號,COUNTER實際上是串并轉(zhuǎn)換" title="串并轉(zhuǎn)換">串并轉(zhuǎn)換器,將并行打印數(shù)據(jù)轉(zhuǎn)換成串行數(shù)據(jù)以及移位時鐘和鎖存信號。

5 仿真驗證

首先,使用硬件描述語言將每個獨立的單元模塊抽象出硬件實體,在EDA工具軟件中調(diào)試通過并生成符號模型,然后再生成包含地址分配模塊和接口部件的頂層文件,仿真出波形,完成整個設(shè)計。

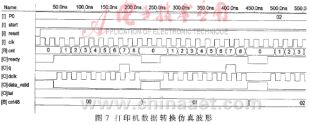

圖7為將CPU輸入的并行數(shù)據(jù)轉(zhuǎn)換成串行數(shù)據(jù)的打印機數(shù)據(jù)并-串轉(zhuǎn)換仿真波形圖,在圖5的時序驅(qū)動下將串行數(shù)據(jù)輸入到打印機。在MAXPLUS II中選定CPLD器件,對這一部分電路做timing analyzer分析,得到理論移位時鐘的最高頻率可以達到111MHz。這一結(jié)果的重要意義在于:假設(shè)一個并行數(shù)據(jù)需經(jīng)過8個時鐘后被移入打印機中,當CPU工作在40MHz時,若其發(fā)送一個并行數(shù)據(jù)到CPLD需要4個指令周期,每個指令周期需用12個機器周期,則CPU每發(fā)送一個并行數(shù)據(jù)的無間隔時間大約為(1/40)×4×2即1.2μs。可見,只要CPLD的并-串轉(zhuǎn)換模塊移位時間小于1.2μs即工作頻率大于0.83MHz,即可實現(xiàn)單片機與打印機之間的零等待時間數(shù)據(jù)傳輸,這對于提高打印機打印速度非常有幫助。圖5顯示了將一個并行數(shù)據(jù)2移位的例子,最低位(LSB)最先從右邊移出。

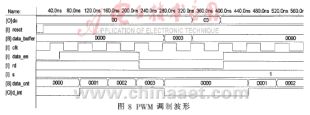

圖8是PWM調(diào)制轉(zhuǎn)換仿真驗證波形圖。PWM(Pulse Wide Moudulation)脈寬調(diào)制電路,實現(xiàn)將模擬信號轉(zhuǎn)換成數(shù)字信號,是一種低成本高性能A/D采樣方法。圖中data_cnt計數(shù)器在data_en高電平信號作用下開始對clk脈沖計數(shù),當data_en為低電平時停止計數(shù),如果此時剛好rd也為低電平,則data_cnt被讀出do數(shù)據(jù)線。很顯然,這實際上是對data_en脈沖寬度計數(shù)。需要說明的一點是data_cnt為16位計數(shù)器,而CPU是8位,CPU在s控制信號的作用下分兩次讀出data_cnt數(shù)值。

本文論述了基于單片機和CPLD協(xié)同控制的商用電子秤設(shè)計方案,從應(yīng)用角度著重研究了典型單片機應(yīng)用系統(tǒng)中以CPLD作為邏輯控制部件的設(shè)計理念和實現(xiàn)方法,仿真驗證了設(shè)計的正確性。其中面向存儲器擴展、打印機驅(qū)動等問題的CPLD設(shè)計方法對CPU是透明的,其意義不僅在于可以提高系統(tǒng)的穩(wěn)定性、減少CPU負荷、縮短調(diào)試周期和降低生產(chǎn)成本,而且可以泛化到DSP或其他類型CPU的應(yīng)用系統(tǒng)中,因此具有推廣價值。

參考文獻

[1] 求是科技.CPLD/FPGA應(yīng)用開發(fā)技術(shù)與工程實踐[M].北京:人民郵電出版社,2005.

[2] Atmel Corp. EPM7128’s datasheet.

[3] 張會生.基于77E58的高速行式熱敏打印機控制板的研制[J] .電子技術(shù)應(yīng)用,2004,30(1):37-39.

[4] Seiko Instruments Inc.LTP1245’ usage manual.