0 引言

近幾年,隨著電子消費(fèi)產(chǎn)品需求的日益增長,功率MOSFET的需求也越來越大。其中,TMOS由于溝道是垂直方向,在相同面積下,單位元胞的集成度較高,因此導(dǎo)通電阻較低,同時又具有較低的柵-漏電荷密度、較大的電流容量,從而具備了較低的開關(guān)損耗及較快的開關(guān)速度,被廣泛地應(yīng)用在低壓功率領(lǐng)域。

低壓TMOS的導(dǎo)通電阻主要是由溝道電阻和外延層電阻所組成,為了降低導(dǎo)通電阻,同時不降低器件其他性能,如漏源擊穿電壓,最直接的辦法是減少相鄰元胞的間距,在相同的面積下,增加元胞的集成度。基于此,本文借助了溝槽式接觸概念以及突起式多晶硅結(jié)構(gòu)來克服由尺寸縮小引發(fā)的溝道穿通效應(yīng)。最終通過試驗(yàn),成功開發(fā)出柵極電壓為4.5 V、工作電流5 A時,Rdson·A為9.5 mΩ·mm2、漏源擊穿電壓大于20 V、開啟電壓0.7 V、元胞間距1.4μm的n型TMOS。

1 器件仿真與工藝實(shí)現(xiàn)

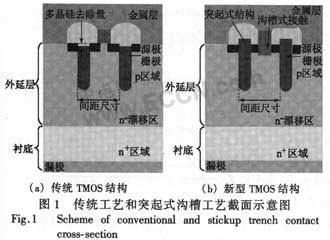

通過圖1中傳統(tǒng)TMOS的截面圖和突起式溝槽工藝截面圖的比較,可以看到傳統(tǒng)的工藝是利用光刻工藝以掩模版形成器件源區(qū)(n+),但是當(dāng)尺寸不斷縮小以后,源區(qū)掩模版形成的光刻膠尺寸隨之變小,在后續(xù)的離子注入工藝中,增加了光刻膠脫落的風(fēng)險,這就意味著單位元胞中本該被光刻膠掩蔽的有源區(qū)會被注入As+離子,從而產(chǎn)生寄生的npn三極管,導(dǎo)致器件工作時漏電增加,嚴(yán)重情況下會導(dǎo)致器件完全失效。本文采用溝槽式接觸這一概念,當(dāng)源區(qū)注入時,有源區(qū)不保留光刻膠,As+離子完全注入,之后利用接觸孔掩模版直接刻蝕掉多余的As+離子注入?yún)^(qū)域,完全避免了傳統(tǒng)工藝下產(chǎn)生寄生npn三極管的風(fēng)險,如圖1(b)中新型TMOS結(jié)構(gòu)所示。

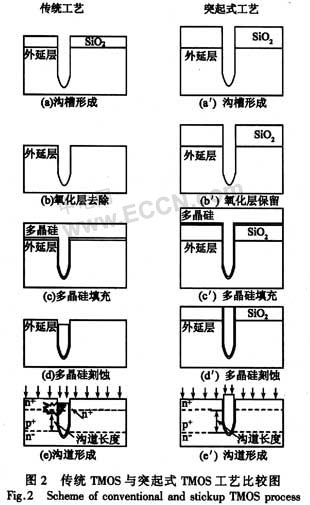

當(dāng)單位元胞相鄰間距為1.4 μm工藝時,由于設(shè)計(jì)的溝道長度大約為0.5μm,源區(qū)結(jié)深大致為0.3μm,不得不考慮到傳統(tǒng)工藝下源區(qū)注入時,多晶硅刻蝕工藝波動所帶來的器件性能下降的風(fēng)險。在傳統(tǒng)工藝中,當(dāng)多晶硅淀積完成后,須通過刻蝕來形成柵極區(qū)域,但是多晶硅去除量難以精準(zhǔn)控制,同時考慮到刻蝕工藝面內(nèi)均勻性的特點(diǎn),Si片內(nèi)中心與邊緣的去除量無法保證相同,從而為隨后的源區(qū)注人工藝留下了潛在的風(fēng)險。如圖2傳統(tǒng)TMOS與突起式TMOS工藝比較圖2(e)所示,當(dāng)源區(qū)注入時,如果柵極多晶硅刻蝕量過多,會導(dǎo)致源區(qū)高濃度的As+離子從柵極邊緣注入到溝道中,間接地減少了溝道長度,從而降低了閾值開啟電壓(Vth),尤其當(dāng)溝道長度較短時,甚至?xí)?dǎo)致器件在正常工作狀態(tài)時發(fā)生漏源間穿通效應(yīng),最終導(dǎo)致器件失效。本文采用K·Shenai的突起式結(jié)構(gòu),在形成溝槽之后,先保留之前所生長的氧化層,然后直接生長柵極氧化膜和多晶硅,在柵極多晶硅形成后,才將先前生長的氧化層去掉,由此便形成了突起式多晶硅結(jié)構(gòu),從而可以保證在隨后的源區(qū)As+離子注入時,As+離子無法從溝槽側(cè)壁注入到溝道中,從根本上避免了發(fā)生源漏極之間穿通的可能性,降低了器件對刻蝕工藝的依賴程度。這點(diǎn)在器件柵極氧化膜厚度較薄的情況下尤其明顯,此時如果采用傳統(tǒng)工藝,源區(qū)離子注入時,As+離子更容易從側(cè)壁注入到溝道中,從而影響溝道長度。

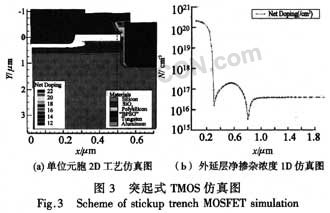

本文通過綜合運(yùn)用溝槽式接觸以及突起式結(jié)構(gòu)這兩個技術(shù),得到了漏源間擊穿電壓大于20 V、閾值開啟電壓0.7 V、柵極擊穿電壓大于12 V以及在柵極電壓4.5 v、工作電流5 A時導(dǎo)通電阻Rdson·A為9.5 mΩ·mm2的n型TMOS。圖3是運(yùn)用SILVACO公司的Athena工藝仿真軟件所模擬出來的器件結(jié)深示意圖以及外延層中的凈摻雜離子濃度曲線,可以看出,溝道長度大致0.5μm,源區(qū)結(jié)深為0.3μm。

2結(jié)果與討論

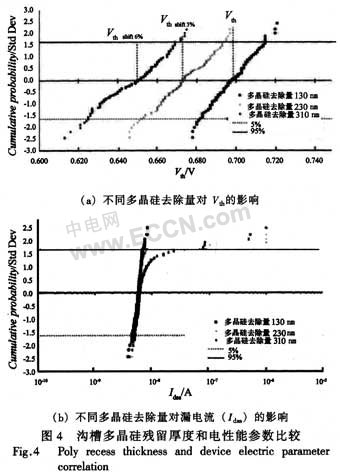

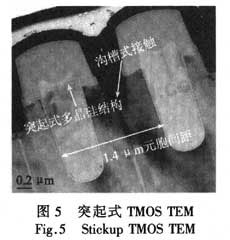

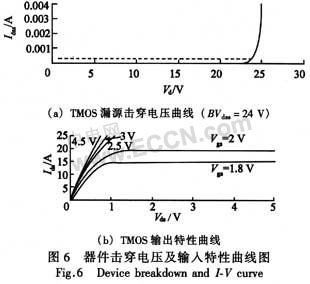

為了驗(yàn)證這一理論,特別設(shè)計(jì)了在傳統(tǒng)工藝下,柵極頂部到外延層表面的多晶硅去除量(130 nm/230 nm/310 nm)的試驗(yàn)。通過器件的電性能參數(shù)比較,如圖4(a)所示,可以看到,隨著多晶硅去除量的增加,閾值開啟電壓隨之降低,說明了器件溝道有效長度變短,源區(qū)離子通過側(cè)壁注入到溝道中,源區(qū)結(jié)深在溝道表面變深。同時由圖4(b)可知,漏源間漏電流也有明顯的區(qū)別,當(dāng)多晶硅去除量在310 nm時,從累積概率圖中可以看到有部分區(qū)域漏電流增大,這一現(xiàn)象隨著多晶硅去除量的減少而逐步消失,從而驗(yàn)證了溝道有效長度與多晶硅去除量有很強(qiáng)的相關(guān)性。由此可見,為了減少器件性能與刻蝕工藝的相關(guān)性,采用突起式多晶硅技術(shù)是非常必要的。圖5是采用透射電子顯微鏡所得到的突起式TMOS實(shí)際截面圖。可以看到在該圖中的突起式多晶硅結(jié)構(gòu)以及溝槽式接觸,單位元胞相鄰間距為1.4μm的n型TMOS,單個芯片有源區(qū)面積為0.4 nm2,并采用TSOP6封裝。圖6(a)、(b)分別是器件擊穿電壓曲線以及輸出特性曲線。由圖6(a)可以看到,當(dāng)漏端漏電流為250μA時,擊穿電壓為24 V,滿足大于20 V的設(shè)計(jì)需要,由圖6(b)可以看到,當(dāng)柵極開啟電壓為4.5 v、工作電流為5 A時,對應(yīng)的導(dǎo)通電阻大致為23.75 mΩ。由于芯片有源區(qū)設(shè)計(jì)尺寸為0.4 mm2,最終Rdson·A為9.5 mΩ·mm2

3 結(jié)語

當(dāng)相鄰單位元胞尺寸不斷縮小后,尤其在設(shè)計(jì)柵極氧化膜較薄的器件時,在傳統(tǒng)的TMOS工藝中,源區(qū)注入會穿透柵極側(cè)壁影響器件性能。采用突起式結(jié)構(gòu)可以有效地避免刻蝕工藝及源區(qū)注入對較短溝道器件的間接影響,消除了器件穿通的風(fēng)險,保證了器件的穩(wěn)定性能和可重復(fù)性。