1 引言

在現(xiàn)代信號(hào)處理系統(tǒng)中,,多通道數(shù)據(jù)采集存儲(chǔ)系統(tǒng)廣泛應(yīng)用于各種商用以及工業(yè)領(lǐng)域中,特別是在艦上系統(tǒng),、彈上設(shè)備及艦上部分系統(tǒng)中,,往往產(chǎn)生寬帶信號(hào)或上升沿下降沿較陡的模擬信號(hào)。對這樣的模擬信號(hào)往往需要將其數(shù)字化后傳輸至計(jì)算機(jī)進(jìn)行數(shù)值和頻譜分析,,并給出具體的分析報(bào)告,。同時(shí),這些信號(hào)往往要對一些相關(guān)信號(hào)同時(shí)測量,,相關(guān)分析得到信號(hào)間的相關(guān)信息,,這就需要同步采集多通道信號(hào),并能準(zhǔn)確無誤存儲(chǔ)?,F(xiàn)在絕大多數(shù)采集系統(tǒng),,只能循環(huán)采集多路信號(hào),不能實(shí)時(shí)同步采集多通道的同一個(gè)采樣點(diǎn),。這樣不能滿足對多通道信號(hào)進(jìn)行相關(guān)信息的分析,,而多通道同步數(shù)據(jù)采集存儲(chǔ)系統(tǒng)的實(shí)現(xiàn)恰恰彌補(bǔ)了傳通采集系統(tǒng)的不足之處。

2 系統(tǒng)設(shè)計(jì)方案及硬件設(shè)計(jì)

2.1 系統(tǒng)設(shè)計(jì)方案

該系統(tǒng)設(shè)計(jì)主要實(shí)現(xiàn)多通道同步數(shù)據(jù)的采集存儲(chǔ),。系統(tǒng)上電后,,FPGA主控模塊控制采集模塊同步采集多通道數(shù)據(jù),,把采集到的數(shù)據(jù)寫到外部FIFO中。FIFO半滿后,,F(xiàn)PGA讀取FIFO中的數(shù)據(jù)寫入Flash存儲(chǔ)器中。該設(shè)計(jì)方案選用FPGA作為主模塊,,主要是考慮FPGA現(xiàn)場可編程特性,,使用靈活方便,能夠降低硬件電路設(shè)計(jì)難度,。

2.2 系統(tǒng)硬件設(shè)計(jì)

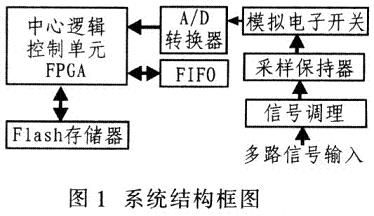

多通道同步數(shù)據(jù)采集存儲(chǔ)系統(tǒng)結(jié)構(gòu)框圖如圖1所示,,主要包括以下部分:

(1)多通道同步數(shù)據(jù)采集模塊 選用AD781采樣保持器完成多通道數(shù)據(jù)采樣保持,滿足系統(tǒng)要求,。A/D轉(zhuǎn)換器選用16位的ADS8401,,可提高采樣精度,有利于分析采集數(shù)據(jù),。

(2)大容量存儲(chǔ)模塊 采用SUMSUNG公司的K9K8G08U0M型Flash作為存儲(chǔ)器,,使用IDT7206作為采集數(shù)據(jù)緩存。

(3)外圍電路 主要包括晶振,、電壓轉(zhuǎn)換器TPS70358及輸入輸出接口等,。

其中,系統(tǒng)采集的重點(diǎn)是實(shí)現(xiàn)多通道數(shù)據(jù)的同步實(shí)時(shí)采集,,其主要邏輯由FPGA主控模塊控制,。存儲(chǔ)模塊中所采用的壞塊檢測技術(shù),可提高Flash存儲(chǔ)的可靠性,。

3 多通道同步數(shù)據(jù)的采集

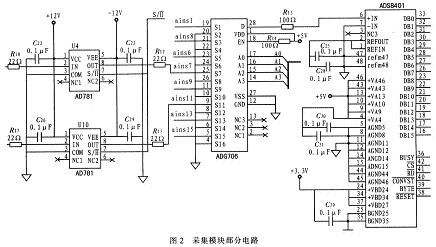

在執(zhí)行多通道同步數(shù)據(jù)采集時(shí),,其電路如圖2所示。其主要工作流程:多路模擬信號(hào)經(jīng)運(yùn)放調(diào)理電路后進(jìn)入采樣保持器,。在每個(gè)周期的開始,,F(xiàn)PGA通過編程輸出脈沖至采樣保持器(AD781)和模擬電子開關(guān)(ADG706),也就是使用采樣保持器的S/H控制信號(hào)進(jìn)行多路同步采樣(S/H=1)和保持(S/H=0),,同時(shí)控制模擬開關(guān)的A0~A3 4個(gè)選通信號(hào),,來選通相應(yīng)通道。選通后的信號(hào)同時(shí)由FPGA的控制進(jìn)入A/D轉(zhuǎn)換器(ADS8401)采集單路16 bit量化,,最后將采集到的數(shù)據(jù)寫到外部FIFO緩存器中,。也就是說,F(xiàn)PGA通過編程定時(shí)邏輯送出脈沖至采樣保持器對模擬輸入采樣,,然后選擇一個(gè)通道的模擬輸入,,完成A/D轉(zhuǎn)換??傊瓼PGA提供采樣保持,、多路選通和A/D轉(zhuǎn)換電路模塊所需的各種狀態(tài)和控制時(shí)序邏輯,。

多通道同步數(shù)據(jù)采集模塊的程序主要采用Verilog HDL語言,Verilog HDL是用于邏輯設(shè)計(jì)的硬件描述語言,,并且已成為IEEE標(biāo)準(zhǔn),。FPGA重點(diǎn)控制Verilog HDL程序算法的實(shí)現(xiàn)。程序主要包括采樣率計(jì)數(shù)循環(huán)控制,、各路模擬開關(guān)選通的設(shè)計(jì),,幀計(jì)數(shù)以及幀標(biāo)志的循環(huán)控制。采樣保持器采樣保持一次,,經(jīng)模擬開關(guān)計(jì)數(shù)循環(huán)控制,,模擬開關(guān)依次選通。選通后的單路信號(hào)進(jìn)行A/D轉(zhuǎn)換,,轉(zhuǎn)換后的數(shù)據(jù)寫入外部FIFO中,。考慮到事后數(shù)據(jù)處理等問題,,所采集的數(shù)據(jù)以一定的幀格式寫入FIFO中,,每一幀數(shù)據(jù)有幀計(jì)數(shù)和幀標(biāo)志。每一幀的長度以及幀標(biāo)志的選擇,,可以根據(jù)需要靈活選定,。

4 多通道同步數(shù)據(jù)的存儲(chǔ)

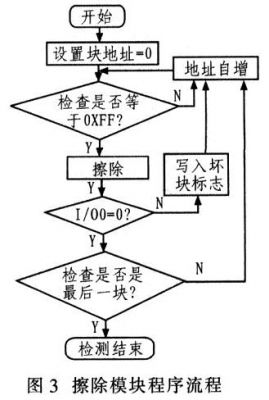

根據(jù)系統(tǒng)要求,需采用SUMSUNG公司的K9K8G08U0M型Flash作為存儲(chǔ)器,。由于1 G的Flash出廠時(shí)帶有一些初始化無效塊(包含一個(gè)或多個(gè)壞位的存儲(chǔ)塊),,它被定義為包含一個(gè)或多個(gè)無效位的存儲(chǔ)塊,制造商不能保證這些無效塊具有可靠性,。由于NAND型Flash存儲(chǔ)容量較大,,難免在使用過程中出現(xiàn)存儲(chǔ)單元的損壞。為保證寫入數(shù)據(jù)的可靠性,,為系統(tǒng)提供真實(shí)準(zhǔn)確的參數(shù),,該系統(tǒng)存儲(chǔ)模塊采用的關(guān)鍵技術(shù)是Flash的壞塊檢測技術(shù)。系統(tǒng)上電后,,F(xiàn)PGA主控模塊首先對Flash進(jìn)行擦除操作,。在擦除過程中,對每塊壞塊標(biāo)志位進(jìn)行檢測,,對使用過程中又出現(xiàn)的壞塊進(jìn)行標(biāo)識(shí),,以便以后使用。擦除模塊具體程序流程如圖3所示,。

多通道同步數(shù)據(jù)采集后,,數(shù)據(jù)以一定的幀格式寫入Flash。在Flash執(zhí)行寫操作時(shí),,首先檢測每塊的壞塊標(biāo)志,。如果壞塊標(biāo)志是非0XFF時(shí),,該塊是壞塊則跳過,繼續(xù)檢測下一塊:如果壞塊標(biāo)志是0XFF時(shí),,則讀取FIFO中的數(shù)據(jù),,寫入Flash中。在對Flash執(zhí)行寫操作時(shí),,嚴(yán)格按照Flash的時(shí)序控制要求,,以保證數(shù)據(jù)的準(zhǔn)確寫入。

系統(tǒng)中在擦除過程中對壞塊進(jìn)行檢測或標(biāo)識(shí),,在數(shù)據(jù)寫入時(shí)再讀取標(biāo)志進(jìn)行寫操作,這樣能夠滿足系統(tǒng)采集速度要求,。如果使用的Flash容量更大并且要求速度較快,,這樣的操作有可能不能滿足系統(tǒng)要求。這時(shí)可以在擦除過程中,,對壞塊的位置進(jìn)行標(biāo)識(shí)并建立壞塊表并隨時(shí)更新,。在對Flash進(jìn)行寫操作時(shí),無需先讀取壞塊位置的標(biāo)識(shí),。只需對壞塊表使用算法進(jìn)行遍歷即可,,這樣可節(jié)約對Flash進(jìn)行讀操作的時(shí)間,提高系統(tǒng)存儲(chǔ)速度,。

5 結(jié)論

詳細(xì)介紹系統(tǒng)組成,,其創(chuàng)新點(diǎn)在于采集模塊的多通道同步性以及存儲(chǔ)模塊Flash的壞塊檢測技術(shù)。該系統(tǒng)已成功用于作戰(zhàn)戰(zhàn)場聲目標(biāo)識(shí)別系統(tǒng)中,,對于其他方面的應(yīng)用,,此設(shè)計(jì)思想具有較強(qiáng)的借鑒意義。