可編程邏輯器件FPGA以其開(kāi)發(fā)周期短、成本低、功耗低、可靠性高等優(yōu)勢(shì),廣泛應(yīng)用于通信、航空、醫(yī)療等領(lǐng)域,近年來(lái)在消費(fèi)電子領(lǐng)域中的應(yīng)用也日漸增加。為進(jìn)一步挖掘FPGA在家庭娛樂(lè)如游戲機(jī)開(kāi)發(fā)與應(yīng)用中的巨大商機(jī),介紹了一款以Altera公司FP-GA芯片為控制核心,附加少量外圍電路組成的乒乓球比賽游戲機(jī)。整個(gè)系統(tǒng)設(shè)計(jì)模塊劃分清晰:包括裁判端、選手端、控制端、顯示端及模擬乒乓球臺(tái);功能齊全:包括發(fā)球權(quán)控制、犯規(guī)提示、局?jǐn)?shù)比分顯示等,模擬實(shí)際乒乓球比賽相似程度高。采用了VHDL語(yǔ)言編程實(shí)現(xiàn),在QuartusⅡ8.1集成環(huán)境下進(jìn)行了模擬仿真,結(jié)果表明在設(shè)定的比賽規(guī)則下,游戲機(jī)運(yùn)行正常,通過(guò)進(jìn)一步優(yōu)化可將其商品化,推入市場(chǎng)。

1 系統(tǒng)組成

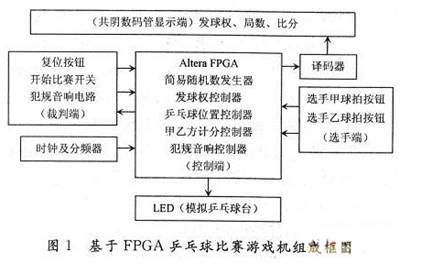

乒乓球比賽游戲機(jī)的組成如圖1所示。比賽規(guī)則約定:五局三勝;11分一局;裁判發(fā)出比賽開(kāi)始信號(hào),觸發(fā)FPGA內(nèi)部隨機(jī)數(shù)發(fā)生器模塊產(chǎn)生首次發(fā)球權(quán)方;比賽進(jìn)行中,選手連續(xù)兩次獲得發(fā)球權(quán)后,發(fā)球權(quán)交予對(duì)方,如未獲發(fā)球權(quán)方發(fā)球,裁判端犯規(guī)音響電路鳴響;13個(gè)LED排列成行模擬乒乓球臺(tái);點(diǎn)亮的LED模擬乒乓球,受FPGA控制從左到右或從右到左移動(dòng);比賽選手通過(guò)按鈕輸入模擬擊球信號(hào),實(shí)現(xiàn)LED移位方向的控制;若發(fā)亮的LED運(yùn)動(dòng)在球臺(tái)中點(diǎn)至對(duì)方終點(diǎn)之間時(shí),對(duì)方未能及時(shí)按下?lián)羟虬粹o使其向相反方向移動(dòng),即失去一分。

2 功能模塊設(shè)計(jì)

圖1中,基于FPGA設(shè)計(jì)的控制端為整個(gè)系統(tǒng)的核心,其內(nèi)部主要由簡(jiǎn)易隨機(jī)數(shù)發(fā)生器、發(fā)球權(quán)控制器、乒乓球位置控制器、甲乙方計(jì)分控制器、犯規(guī)音響控制器等模塊組成。整個(gè)控制端采用模塊化設(shè)計(jì),先用VHDL語(yǔ)言編寫功能模塊,然后用頂層原理圖將各功能模塊連接起來(lái)。設(shè)計(jì)的難點(diǎn)在于協(xié)調(diào)各模塊工作,嚴(yán)格遵守各信號(hào)間時(shí)序關(guān)系。本系統(tǒng)采用1 kHz系統(tǒng)時(shí)鐘。

2.1 簡(jiǎn)易隨機(jī)數(shù)發(fā)生器

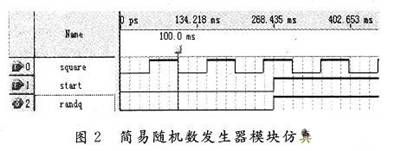

比賽首次發(fā)球權(quán)由隨機(jī)數(shù)發(fā)生器產(chǎn)生的數(shù)據(jù)決定,其隨機(jī)性要求不嚴(yán),因此,采用非常簡(jiǎn)單的模式產(chǎn)生,即一旦FPGA上電,系統(tǒng)時(shí)鐘百分頻產(chǎn)生一方波信號(hào)square,當(dāng)裁判閉合開(kāi)始比賽開(kāi)關(guān)產(chǎn)生start信號(hào)上升沿時(shí),讀取此時(shí)square信號(hào)值作為隨機(jī)數(shù)發(fā)生器輸出randq。模塊仿真如圖2所示,結(jié)果滿足設(shè)計(jì)要求。此模塊設(shè)計(jì)時(shí)保證了square信號(hào)周期應(yīng)遠(yuǎn)大于start信號(hào)上升沿建立時(shí)間,保證隨機(jī)數(shù)據(jù)的正確讀取。

2.2 發(fā)球權(quán)控制器

發(fā)球權(quán)控制器的控制過(guò)程為:如果按下復(fù)位按鈕,發(fā)球權(quán)數(shù)碼管顯示8,否則,開(kāi)始比賽開(kāi)關(guān)閉合時(shí),顯示隨機(jī)數(shù)發(fā)生器的值(0或1,0代表甲方、1代表乙方)。而在比賽中,為遵守發(fā)球權(quán)交換規(guī)則,設(shè)計(jì)甲乙雙方計(jì)分器總和信號(hào)sum_sc是不為0的偶數(shù)時(shí)(即計(jì)分總和最低位sum_sc0下降沿到來(lái)時(shí)),發(fā)球權(quán)數(shù)碼管顯示由0變?yōu)?或由1變?yōu)?。

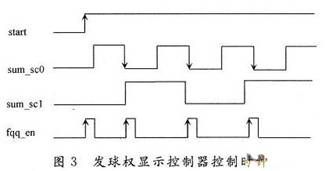

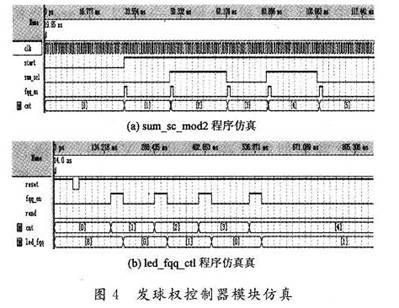

此模塊設(shè)計(jì)中,發(fā)球權(quán)數(shù)碼管的信號(hào)控制受多個(gè)時(shí)鐘的控制,即開(kāi)始比賽開(kāi)關(guān)start和計(jì)分值sum_sc0信號(hào),這在VHDL編程語(yǔ)言中無(wú)法用一個(gè)進(jìn)程實(shí)現(xiàn),必須將兩個(gè)信號(hào)組合成一個(gè)時(shí)鐘信號(hào),并統(tǒng)一兩個(gè)時(shí)鐘的觸發(fā)沿。因此最佳時(shí)鐘觸發(fā)方式如圖3所示的fqq_en信號(hào)。為滿足這種時(shí)序要求,借助計(jì)分總和次低位sum_sc1信號(hào)設(shè)計(jì)entity sum_sc_mod2,由于start和sum_sc1的頻率都遠(yuǎn)低于系統(tǒng)時(shí)鐘信號(hào)clk頻率,則可借助clk高頻信號(hào)捕捉其邊沿產(chǎn)生新的時(shí)鐘信號(hào)fqq_en,并產(chǎn)生其計(jì)數(shù)值,仿真波形如圖4(a)所示。為保證發(fā)球權(quán)數(shù)碼管顯示正確,設(shè)計(jì)entitv led_fqq_ctl在fqq_en下降沿時(shí),根據(jù)其計(jì)數(shù)值產(chǎn)生相應(yīng)的數(shù)碼管輸出信號(hào)led_fqq,仿真波形如圖4(b)所示。

發(fā)球權(quán)控制器的VHDL核心程序如下:

2.3 乒乓球位置控制、甲乙計(jì)分、犯規(guī)音響控制

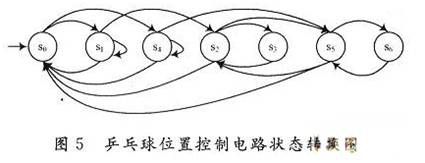

乒乓球位置控制電路為FPGA控制端的核心,依據(jù)比賽規(guī)則,采用了Mealy型狀態(tài)機(jī)來(lái)實(shí)現(xiàn),大大降低了設(shè)計(jì)難度。狀態(tài)機(jī)共定義了7個(gè)狀態(tài),各狀態(tài)定義如表1所示,狀態(tài)轉(zhuǎn)換如圖5所示,轉(zhuǎn)換條件如表2所示,具體程序如下。

3 頂層模塊仿真測(cè)試

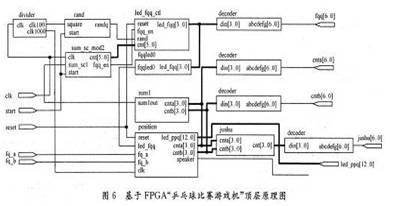

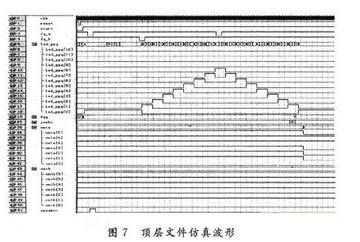

由于篇幅限制,本系統(tǒng)中的分頻器、譯碼器等常用模塊的設(shè)計(jì)就不再此贅述,最終頂層原理圖設(shè)計(jì)如圖6所示,仿真波形如圖7所示,分析波形可知,圖中開(kāi)始比賽信號(hào)產(chǎn)生后,首次發(fā)球權(quán)方為乙方,甲方發(fā)球造成犯規(guī)音響電路鳴響,即speaker信號(hào)為高電平,然后乙方發(fā)球,乒乓球依次移位,甲方接球成功后乙方未接球成功,甲方得分,cnta信號(hào)為“0110000”,注意,此處輸出為驅(qū)動(dòng)數(shù)碼管輸出信號(hào),代表數(shù)字“1”。通過(guò)仿真可知,該系統(tǒng)設(shè)計(jì)滿足游戲機(jī)比賽規(guī)則要求。

4 結(jié)語(yǔ)

采用VHDL語(yǔ)言編程,基于FPGA成功設(shè)計(jì)了一款乒乓球比賽游戲機(jī),通過(guò)仿真驗(yàn)證可知,結(jié)果滿足設(shè)計(jì)需求,系統(tǒng)具有發(fā)球權(quán)控制、自動(dòng)計(jì)分、犯規(guī)提示等多種功能,能有效模擬實(shí)際乒乓球比賽。該系統(tǒng)進(jìn)一步改進(jìn)思路為:改用人體感應(yīng)傳感器來(lái)采集擊球信號(hào),采用FPGA產(chǎn)生視頻信號(hào)傳送到電視機(jī)或監(jiān)視器,更直觀地展示乒乓球運(yùn)動(dòng)軌跡,從而真正實(shí)現(xiàn)人機(jī)互動(dòng),優(yōu)化虛擬效果。