0 引 言

可編程邏輯器件PLD(Programmable Logic De-vice)是一種數(shù)字電路,它可以由用戶來進行編程和進行配置,利用它可以解決不同的邏輯設(shè)計問題。PLD由基本邏輯門電路、觸發(fā)器以及內(nèi)部連接電路構(gòu)成,利用軟件和硬件(編程器)可以對其進行編程,從而實現(xiàn)特定的邏輯功能。可編程邏輯器件自20世紀70年代初期以來經(jīng)歷了從PROM,PLA,PAL,GAL到CPLD和FPGA的發(fā)展過程,在結(jié)構(gòu)、工藝、集成度、功能、速度和靈活性方面都有很大的改進和提高。

隨著數(shù)字集成電路的不斷更新和換代,特別是可編程邏輯器件的出現(xiàn),使得傳統(tǒng)的數(shù)字系統(tǒng)設(shè)計方法發(fā)生了根本的改變。可編程邏輯器件的靈活性使得硬件系統(tǒng)設(shè)計師在實驗室里用一臺計算機、一套相應(yīng)的EDA軟件和可編程邏輯芯片就可以完成數(shù)字系統(tǒng)設(shè)計與生產(chǎn)。

1 Max+plusⅡ簡介

Max+plusⅡ是一種與結(jié)構(gòu)無關(guān)的全集成化設(shè)計環(huán)境,使設(shè)計者能對Altera的各種CPLD系列方便地進行設(shè)計輸入、快速處理和器件編程。Max+plusⅡ開發(fā)系統(tǒng)具有強大的處理能力和高度的靈活性,其主要優(yōu)點:與結(jié)構(gòu)無關(guān)、多平臺、豐富的設(shè)計庫、開放的界面、全集成化、支持多種硬件描述語言(HDL)等。

數(shù)字系統(tǒng)的設(shè)計采用自頂向下、由粗到細,逐步分解的設(shè)計方法,最頂層電路是指系統(tǒng)的整體要求,最下層是具體的邏輯電路的實現(xiàn)。自頂向下的設(shè)計方法將一個復(fù)雜的系統(tǒng)逐漸分解成若干功能模塊,從而進行設(shè)計描述,并且應(yīng)用EDA軟件平臺自動完成各功能模塊的邏輯綜合與優(yōu)化,門級電路的布局,再下載到硬件中實現(xiàn)設(shè)計,具體設(shè)計過程如下。

1.1 設(shè)計輸入

Max+plusⅡ支持多種設(shè)計輸入方式,如原理圖輸入、波形輸入、文本輸入和它們的混合輸入。

1.2 設(shè)計處理

設(shè)計輸入完后,用Max+plusⅡ的編譯器編譯、查錯、修改直到設(shè)計輸入正確,同時將對輸入文件進行邏輯簡化、優(yōu)化,最后生成一個編程文件,這是設(shè)計的核心環(huán)節(jié)。

1.3 設(shè)計檢查

Max+plusⅡ為設(shè)計者提供完善的檢查方法設(shè)計仿真和定時分析,其目的是檢驗電路的邏輯功能是否正確,同時測試目標器件在最差情況下的時延,這一查錯過程對于檢驗組合邏輯電路的競爭冒險和時序邏輯電路的時序、時延等至關(guān)重要。

1.4 器件編程

當(dāng)電路設(shè)計、校驗之后,Max+plusⅡ的Program-mer將編譯器所生成的編譯文件下載到具體的CPLD器件中,即實現(xiàn)目標器件的物理編程。

2 以計數(shù)器為例介紹具體的設(shè)計方法

計數(shù)器是非常常用的時序邏輯電路。計數(shù)器類型有多種,實現(xiàn)計數(shù)器的方法也有很多。可以買到大部分類型的中規(guī)模集成的計數(shù)器直接使用,也可以用觸發(fā)器搭建符合要求的計數(shù)器。但是采用以上方法實現(xiàn)的計數(shù)器靈活性不夠,不能隨時進行修改,通用性差。這里介紹基于可編程邏輯器件的實現(xiàn)方法。

2.1 設(shè)計輸入

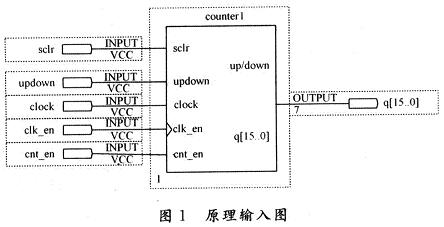

采用原理-圖輸入的思維方式比較適合一直采用傳統(tǒng)設(shè)計方法人的使用。原理圖輸入如圖1所示。

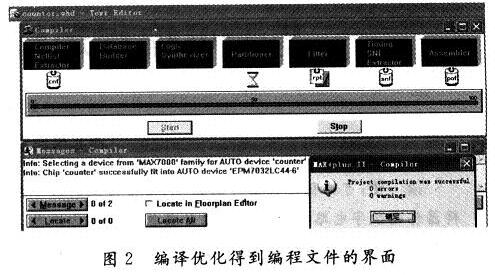

采用硬件描述語言輸入的方法對于沒有傳統(tǒng)設(shè)計方法經(jīng)驗的人更容易入門,修改起來也更方便。給出了一個可逆計數(shù)器的實現(xiàn)實例,程序的核心部分如下:

2.2 設(shè)計處理

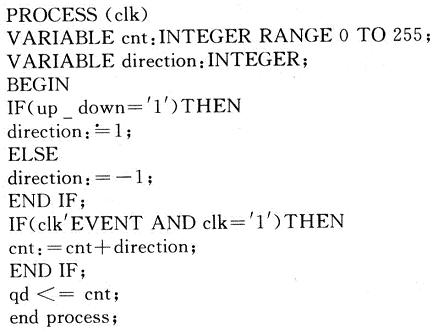

原理圖或程序完成之后,選擇好器件并進行引腳定義,然后編譯優(yōu)化得到編程文件的界面如圖2所示。

2.3 設(shè)計檢查

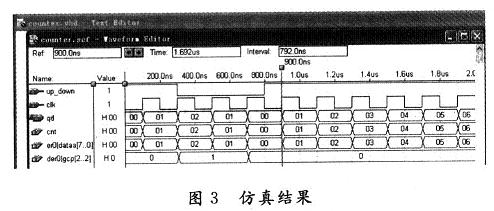

編譯結(jié)束后,建立波形文件進行仿真,注意波形文件需要先保存,保存文件名和源文件一致才能進行仿真。結(jié)果如圖3所示。

仿真結(jié)果達到設(shè)計目的,符合設(shè)計要求。這時可以把編譯生成的*.pof文件下載到選定的器件使用。用以上方法實現(xiàn)的器件,修改起來非常方便,只需要修改程序重新編譯下載即可,任何類型的計數(shù)器都可以在可編程邏輯器件實現(xiàn)。

3 結(jié) 語

隨著電子技術(shù)的高速發(fā)展,CPLD和FPGA器件在集成度、功能和性能(速度及可靠性)方面已經(jīng)能夠滿足大多數(shù)場合的使用要求。用CPLD,F(xiàn)PGA等大規(guī)模可編程邏輯器件取代傳統(tǒng)的標準集成電路、接口電路和專用集成電路已成為技術(shù)發(fā)展的必然趨勢。可編程邏輯器件是邏輯器件家族中發(fā)展最快的一類器件,它出現(xiàn)使得產(chǎn)品開發(fā)周期縮短、現(xiàn)場靈活性好、開發(fā)風(fēng)險變小,隨著工藝、技術(shù)及市場的不斷發(fā)展,PLD產(chǎn)品的價格將越來越便宜、集成度越來越高、速度越來越快,再加上其設(shè)計開發(fā)采用符合國際標準的、功能強大的通用性EDA工具,可編程邏輯器件的應(yīng)用前景將愈來愈廣闊。