隨著工藝技術(shù)的越來越前沿化, FPGA器件擁有更多的邏輯、存儲(chǔ)器和特殊功能,如存儲(chǔ)器接口、 DSP塊和多種高速SERDES信道,這些發(fā)展不斷地對(duì)系統(tǒng)功率要求提出挑戰(zhàn)。由此,設(shè)計(jì)師也許會(huì)想要拖一座冰山到電路板上,但這樣一來IT人員就會(huì)面臨一團(tuán)亂麻的境地了。顯然冰山是一個(gè)不切實(shí)際的玩笑,以下是一種可行的方案:使用工具來精確計(jì)算功率要求。

功率計(jì)算的關(guān)鍵是兩方面:靜態(tài)和動(dòng)態(tài)功率。 盡管FPGA廠商承諾將提供切實(shí)可用的低功耗器件,但由于工藝技術(shù)從130納米縮小到90納米、65納米或更加小的線條,晶體管固有的漏電加劇了,靜態(tài)功耗也增加了。此外,使用FPGA時(shí)極高的系統(tǒng)性能要求使得動(dòng)態(tài)功耗上升,動(dòng)態(tài)功耗是頻率和開關(guān)節(jié)點(diǎn)的函數(shù)。那設(shè)計(jì)者如何才能準(zhǔn)確地確定器件的功耗,同時(shí)考慮與這個(gè)問題有關(guān)的所有重要因素,有效地作出必要的設(shè)計(jì)權(quán)衡,建立一個(gè)滿足所有性能要求的可靠系統(tǒng)呢?

功耗計(jì)算對(duì)于FPGA設(shè)計(jì)十分重要是基于兩點(diǎn)考慮:系統(tǒng)電源的大小和散熱。眾所周知,系統(tǒng)中的所有器件都需要一個(gè)良好、清潔、精確和可靠的電源,且能有效地運(yùn)作。精確地計(jì)算功耗就能有的放矢地確定電源大小,電源過大將增加成本。散熱裝置對(duì)系統(tǒng)可靠性至關(guān)重要。所有器件都已列出了其對(duì)器件結(jié)溫容忍度的界限。超過這些界限,將可能導(dǎo)致運(yùn)行效率低下,或者更糟糕的是導(dǎo)致系統(tǒng)永久地?fù)p壞。當(dāng)然,也可以采用一些技術(shù)來緩解散熱問題,如對(duì)系統(tǒng)增加散熱片或氣流,從而有效地降低運(yùn)行溫度。那么,在系統(tǒng)建立之前,設(shè)計(jì)師怎樣才能夠準(zhǔn)確地估計(jì)功耗和設(shè)備的熱耗?這相當(dāng)于在談?wù)撘粋€(gè)先有雞還是先有蛋的問題!幸運(yùn)的是,有一個(gè)專為這項(xiàng)任務(wù)而設(shè)計(jì)的功耗計(jì)算器。

準(zhǔn)確評(píng)估功耗去建立一個(gè)熱模型的一些基本要素如下:

1 。器件的各種要素: FPGA(使用的和未使用的部分) 、封裝、工作頻率、活動(dòng)因素和速度等級(jí)。

2 。環(huán)境因素:散熱片、氣流、電路板尺寸和環(huán)境溫度。

3 。可用性要素:設(shè)計(jì)過程中在任何時(shí)間的建模能力,導(dǎo)入實(shí)際的運(yùn)行數(shù)據(jù),方便地做“假設(shè)”的完整環(huán)境的評(píng)估。

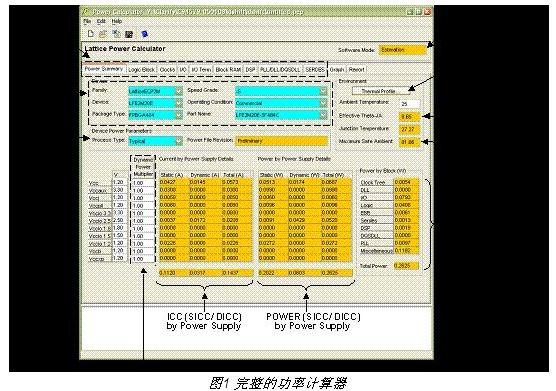

由于功率計(jì)算器必須在整個(gè)設(shè)計(jì)過程中都是可用的,能始終在這個(gè)工具中對(duì)器件作出選擇很重要,同樣,用戶對(duì)不同的封裝、器件、密度、速度等級(jí)和溫度范圍進(jìn)行選擇也是很重要的。熱特性還使用戶隨時(shí)了解他的設(shè)計(jì)是在一個(gè)明確、安全的運(yùn)行環(huán)境中進(jìn)行。

功率計(jì)算器還提供了非常明確的單獨(dú)工作區(qū)域,以按鈕的形式對(duì)器件的每個(gè)結(jié)構(gòu)、資源、可用的元件進(jìn)行操作。針對(duì)可用性的要求,該工具會(huì)顯示每個(gè)電源的電流和功率,以及每個(gè)元件和所有元件的功耗總和。這樣給出了每個(gè)元件對(duì)整體功耗影響的完整了解,并允許用戶決定如何將設(shè)計(jì)進(jìn)行最好的優(yōu)化,以減少總功耗。

表格的羅列展示是很有價(jià)值,圖形也相當(dāng)有用。圖2展示了一組由功率計(jì)算器自動(dòng)生成的圖形。圖表顯示了下列信息:

功率與電壓(或電壓―――典型和最壞的情況)

功率與環(huán)境溫度―――典型和最壞的情況

功率與頻率―――典型和最壞的情況

這些圖表為設(shè)計(jì)一個(gè)可靠系統(tǒng)提供了很有用的信息。

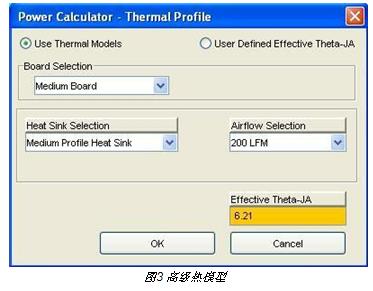

環(huán)境變量也必須是易于設(shè)置和修改的。圖3展示了高級(jí)的熱特性選擇屏幕,用戶可以輕松地為設(shè)計(jì)修改熱特性。由工具或自定模式提供的普通熱模型可用于計(jì)算,為任何設(shè)計(jì)環(huán)境提供靈活性和精確性也很重要。用戶還可以設(shè)置散熱片和氣流參數(shù),以及有效的用于計(jì)算的Theta-JA。為了能夠?qū)崿F(xiàn)所期望的性能和可靠的結(jié)果,所有這些因素對(duì)正確 分析實(shí)際系統(tǒng) 環(huán)境、作出必要的設(shè)計(jì)選擇來說至關(guān) 重要。

有一個(gè)完整的系統(tǒng)級(jí)理解和精確的功率模型將能使設(shè)計(jì)師作出必要的決擇,從而完成設(shè)計(jì)。然后,設(shè)計(jì)者可以集中精力于降低功耗,其中包括以下幾個(gè)方面:

降低設(shè)備的工作電壓

優(yōu)化時(shí)鐘頻率

減少設(shè)計(jì)中長(zhǎng)的布線

優(yōu)化編碼

優(yōu)化熱模型

依據(jù)設(shè)計(jì)中所用器件資源的全部數(shù)據(jù)、所有對(duì)建立熱模型至關(guān)重要的環(huán)境變量、以及在設(shè)計(jì)過程中自由地使用和修改各點(diǎn)參數(shù),就可以可靠地實(shí)現(xiàn)FPGA設(shè)計(jì),使其滿足系統(tǒng)性能指標(biāo)。

本文來源于與非網(wǎng) http://www.eefocus.com

原文地址:http://www.eefocus.com/article/08-11/4322423091125V883.html