引言

隨著無線通信的發(fā)展,出現(xiàn)了多種模式的通信體制,為了滿足互通性的問題,軟件無線電" title="軟件無線電">軟件無線電的思想被提出來。所謂軟件無線電,其中心思想是:構(gòu)造一個(gè)具有開放性、標(biāo)準(zhǔn)化、模塊化的通用硬件平臺,將通信的各種功能通過軟件來完成,并使寬帶A/D和D/A轉(zhuǎn)換器盡可能靠近天線,以研制出具有高度靈活性、開放性的新一代無線通信系統(tǒng)。由于軟件無線電可以通過增加軟件模塊來增加新的功能,而且硬件也可以隨著器件的發(fā)展而不斷地升級,所以這一概念一經(jīng)提出就受到了廣泛的關(guān)注。

OFDM" title="OFDM">OFDM(orthogonal frequency division multiplexing,正交頻分復(fù)用)是一種具有多種優(yōu)點(diǎn)的傳輸系統(tǒng),目前已經(jīng)有很多應(yīng)用,而且隨著第四代(4G" title="4G">4G)無線通信系統(tǒng)的研究進(jìn)入實(shí)質(zhì)性階段,OFDM極有可能成為4G中的傳輸方案。本文在此背景下,設(shè)計(jì)了一種基于軟件無線電的平臺,并在此平臺上實(shí)現(xiàn)了OFDM傳輸系統(tǒng),

系統(tǒng)結(jié)構(gòu)設(shè)計(jì)

目前受器件的限制,軟件無線電一般都采用中頻采樣的結(jié)構(gòu),這樣做既兼顧了軟件無線電的思想,又能在目前的器件水平下搭建實(shí)際可應(yīng)用的系統(tǒng)。本文的軟件無線電平臺也采用了這一結(jié)構(gòu)。隨著無線通信系統(tǒng)的發(fā)展都在朝著高速率、可移動(dòng)性方向發(fā)展,因此本平臺的設(shè)計(jì)也必然要適應(yīng)寬帶無線通信系統(tǒng)的要求。

平臺結(jié)構(gòu)

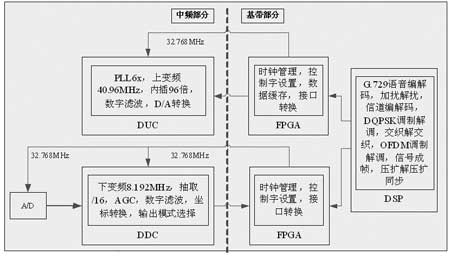

平臺主要針對系統(tǒng)物理層中的中頻和基帶處理單元而設(shè)計(jì)。系統(tǒng)的結(jié)構(gòu)如圖1所示。平臺由一個(gè)DSP(TMS320C6414T" title="TMS320C6414T">TMS320C6414T)、兩片F(xiàn)PGA(Cyclone EP1C6Q240C8" title="EP1C6Q240C8">EP1C6Q240C8)、上變頻芯片DUC(AD9857)、下變頻芯片DDC(HSP50214B)等構(gòu)成。

圖1 平臺結(jié)構(gòu)圖

根據(jù)信號處理模塊和各芯片數(shù)據(jù)處理的特點(diǎn),我們將各通信模塊分配到不同的器件中來完成。DSP的主頻很高,而且內(nèi)部資源豐富,支持高級語言的編程,適合于串行的算法,用來完成協(xié)議和基帶處理;FPGA配置靈活多變,雖然主頻不太高,但是鑒于其并行處理能力突出,用于完成時(shí)鐘分配、芯片設(shè)置、接口轉(zhuǎn)換等;AD9857和HSP50214B是用于上下變頻的ASIC,集成程度高,參數(shù)設(shè)置靈活,可以滿足多模式的數(shù)字上下變頻,數(shù)據(jù)速率變換和濾波。下面簡要介紹一下平臺上器件的性能。

器件介紹

● DSP

平臺選用的DSP芯片是TI公司的TMS320C6416T芯片。該處理器屬于32位定點(diǎn)處理器,主頻1GHz,內(nèi)部集成豐富的外設(shè)和接口。在指令結(jié)構(gòu)上,擴(kuò)展了尋址指令、位域指令、打包解包、控制轉(zhuǎn)移等指令,增強(qiáng)了芯片的處理能力。在計(jì)算2048點(diǎn)的復(fù)數(shù)FFT運(yùn)算時(shí),可以在大約26 000個(gè)時(shí)鐘周期內(nèi)完成。

6416T主要包含的模塊有:1)兩個(gè)通用寄存器組,64個(gè)32位通用寄存器;2)8個(gè)功能單元,6個(gè)ALU(32/40b),兩個(gè)乘法器(16×16);3)一共8.256Mb的兩級緩存內(nèi)部存儲(chǔ);此外,還有圖1中沒有列出的Viterbi編解碼協(xié)處理器(VCP)和Turbo碼編解碼協(xié)處理器(TCP)。VCP支持500路7.95Kb/s AMR,TCP可以處理6路2Mb/s 3GPP。

接口方面包括:1)多通道EDMA控制器;2)多通道緩沖串口(MCBSP);3)高性能外部存儲(chǔ)器接口(EMIF);4)可訪問DSP的整個(gè)存儲(chǔ)空間的主機(jī)口(HPI);這里不在一一列舉。

● 上變頻芯片AD9857

AD9857是一款高性能的數(shù)字上變頻器,最高時(shí)鐘為200MHz,根據(jù)外時(shí)鐘的范圍,可以選擇0~80MHz的任意中頻輸出;芯片還具有兩級內(nèi)插功能,可以實(shí)現(xiàn)4倍固定內(nèi)插和2~64倍可選內(nèi)插倍數(shù),便于多數(shù)據(jù)速率變換;14b的DAC。

● A/D變換器AD9051

ADC選用ADI公司的AD9051,最高采樣速率達(dá)到60MSPS,10b輸出,對于中心頻率較低的中頻信號可以進(jìn)行直接采樣,中頻值較高的則運(yùn)用帶通采樣方式。

●下變頻芯片HSP50214B

HSP50214B是專用數(shù)字下變頻芯片中綜合性能最好的,除數(shù)字下變頻外還具有最高255階可編程FIR濾波器,0~96dB動(dòng)態(tài)范圍的 AGC自動(dòng)增益控制,數(shù)據(jù)速率變換包括4~32倍CIC抽取和5級HB抽取,以及FIR1-16倍抽取,坐標(biāo)轉(zhuǎn)換,鑒頻等功能,而且具有四種輸出形式,接口靈活。

● FPGA

由于平臺上的中頻處理由ASIC完成,所以FPGA選用了CycloneⅡ EP1C6Q240C8,這是一款低端的FPGA芯片,邏輯單元只有6000門,主要用來完成時(shí)鐘分配,接口轉(zhuǎn)換,ASIC控制字配置,以及作為DSP的協(xié)處理器的補(bǔ)充。

該平臺較好的整合了DSP、ASIC和FPGA,兼顧了系統(tǒng)的通用性和復(fù)雜度,ASIC的應(yīng)用減少了系統(tǒng)配制時(shí)的軟件設(shè)計(jì)復(fù)雜度。

OFDM收發(fā)信機(jī)的實(shí)現(xiàn)

OFDM技術(shù)是當(dāng)前的熱門技術(shù)之一,與傳統(tǒng)的傳輸技術(shù)相比,OFDM具有:1)降低了子載波的數(shù)據(jù)速率,減小了無線信道引起的ISI,有效的降低了多徑干擾;2)采用若干相互正交的子載波,頻譜有重疊,最大限度地提高頻譜效率;3)采用IFFT和FFT進(jìn)行調(diào)制和解調(diào),硬件實(shí)現(xiàn)簡單;所以,盡管存在峰均比較高以及對頻偏敏感等問題,OFDM仍然不失為一種性能優(yōu)良的傳輸方式。目前采用了OFDM的標(biāo)準(zhǔn)主要有數(shù)字音頻廣播(DAB)、數(shù)字視頻廣播(DVB)、歐洲無線局域網(wǎng)Magic WAND、802.11、非對稱數(shù)字用戶線(ADSL)等。為此,我們在本平臺上實(shí)現(xiàn)了OFDM的收發(fā)信機(jī)。

本OFDM系統(tǒng)采用了如下的基帶和中頻結(jié)構(gòu),如圖2所示。圖2中,音頻編碼采用了G.729標(biāo)準(zhǔn),加擾采用了9位的反饋移位寄存器產(chǎn)生的偽隨機(jī)序列,壓擴(kuò)部分為μ律壓擴(kuò)變換,其中μ=3。另外,系統(tǒng)子載波個(gè)數(shù)為2048,載波間隔1kHz,中頻40.96MHz。圖中的結(jié)構(gòu)幾乎包括了所有 OFDM系統(tǒng)應(yīng)有的處理單元,具有一定的代表性,在此基礎(chǔ)上經(jīng)過必要的參數(shù)修改,可以演變出絕大多數(shù)標(biāo)準(zhǔn)的系統(tǒng)。為了便于接收端的同步處理,在幀結(jié)構(gòu)上采用了類似DAB的結(jié)構(gòu),每幀76個(gè)符號,其中第一個(gè)符號為空符號,第二個(gè)符號為固定的相位參考符號。

圖2 OFDM系統(tǒng)框圖

通過對各模塊功能的分析,并結(jié)合本平臺上各器件的特點(diǎn),對各模塊的實(shí)現(xiàn)在平臺上進(jìn)行分配。圖3顯示了這種分配方式。

圖3 OFDM系統(tǒng)處理流程

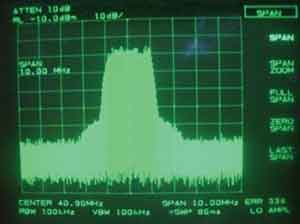

數(shù)據(jù)接口方面,發(fā)射端DSP將經(jīng)過基帶處理以后成幀的信號通過EMIF接口發(fā)送到FPGA的FIFO中緩存,然后數(shù)據(jù)進(jìn)入數(shù)字上變頻器,進(jìn)行40.96MHz的上變頻,上變頻后的數(shù)據(jù)經(jīng)過4倍固定內(nèi)插和CIC的24倍內(nèi)插后經(jīng)過D/A輸出,形成OFDM中頻信號。如圖4所示。

圖4 OFDM中頻信號頻譜儀截圖

接收端對中頻信號以32.768MHz進(jìn)行帶通采樣,數(shù)字下變頻器對采樣后8.192MHz的鏡像頻率進(jìn)行數(shù)字下變頻,之后對信號進(jìn)行16 倍的抽取,使信號速率下降到2M,HSP50214采用并行直接輸出的模式,分兩路分別輸出16b的IQ兩路數(shù)據(jù),F(xiàn)PGA通過并串轉(zhuǎn)換,將數(shù)據(jù)通過 MCBSP送入DSP進(jìn)行同步處理和基帶處理,得到原發(fā)送信息。

結(jié)論

本文提出了一種基于DSP、FPGA以及ASIC的軟件無線電平臺,并在該試驗(yàn)平臺上完成了OFDM系統(tǒng)的基帶和中頻設(shè)計(jì),并且經(jīng)過了實(shí)際的驗(yàn)證,系統(tǒng)運(yùn)行情況良好,有效地支持多種通信模式,是一種應(yīng)用廣泛的軟件無線電平臺。目前正在對功率放大器的基帶預(yù)失真技術(shù)進(jìn)行研究,以進(jìn)一步的改善系統(tǒng)性能。