??? 摘 要: 選用內(nèi)部時(shí)鐘為400MHz的高性能直接數(shù)字合成頻率源DDS芯片AD9951作為核心器件設(shè)計(jì)頻率合成器" title="頻率合成器">頻率合成器,采用DDS+DSP的設(shè)計(jì)方案。利用鎖相環(huán)ADF4113為AD9951提供參考時(shí)鐘。闡述了AD9951芯片的主要性能及其在快速頻率合成器設(shè)計(jì)中的應(yīng)用方法。

??? 關(guān)鍵詞: AD9951芯片;直接數(shù)字合成頻率源;頻率控制字

?

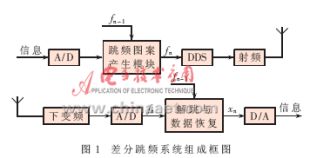

??? 短波通信因其技術(shù)成熟、通信距離遠(yuǎn)、體積小、不易摧毀的特點(diǎn),幾十年來(lái)一直是實(shí)現(xiàn)遠(yuǎn)程通信和戰(zhàn)術(shù)通信的主要手段,如何保證短波電臺(tái)在敵方干擾下通信可靠有效,成為一個(gè)重要的研究課題。由于近十年來(lái)在數(shù)字信號(hào)處理技術(shù)(DSP)、超大規(guī)模集成電路和軟件方面的新技術(shù)、新成果不斷涌現(xiàn),使得現(xiàn)代通信技術(shù)及短波通信技術(shù)得到飛速發(fā)展,尤其是跳頻" title="跳頻">跳頻技術(shù)在短波通信中得到越來(lái)越重要的應(yīng)用。差分" title="差分">差分跳頻技術(shù)是一種新型的跳頻通信技術(shù),它利用跳變載波之間的相關(guān)性來(lái)傳送信息。差分跳頻技術(shù)應(yīng)用于短波通信,可以在短波波段內(nèi)實(shí)現(xiàn)寬頻帶、高速率的跳頻,極大地提高了短波通信的數(shù)據(jù)速率及抗干擾、抗多徑衰落能力,這種新型短波跳頻系統(tǒng)將成為短波通信領(lǐng)域今后發(fā)展方向之一。圖1是典型的差分跳頻系統(tǒng)的組成框圖。本文將針對(duì)短波差分跳頻系統(tǒng)的特點(diǎn),利用AD9951作為核心器件設(shè)計(jì)出適合于該系統(tǒng)的快速DDS頻率合成器。

?????????????????????????

1 快速頻率合成器特點(diǎn)及指標(biāo)要求

??? 短波差分快速跳頻系統(tǒng)跳頻速度達(dá)5000跳/秒,跳頻帶寬達(dá)2.56MHz,數(shù)據(jù)傳輸速率最高可達(dá)19.2Kb/s,對(duì)雜散、相位噪聲等指標(biāo)要求高,因此,系統(tǒng)對(duì)頻率合成器相應(yīng)提出較高的要求。本文設(shè)計(jì)的頻率合成器的指標(biāo)要求如下:

??? · 頻率范圍:1.6MHz~80MHz

??? · 頻率轉(zhuǎn)換" title="頻率轉(zhuǎn)換">頻率轉(zhuǎn)換時(shí)間≤10μs

??? · 頻率間隔:10Hz

??? · 相位噪聲:≤-100dBc/Hz@1kHz

??? · 雜散抑制:≤-60dB

??? 從上述指標(biāo)可以看出本頻率合成器具有頻率覆蓋范圍相對(duì)較寬、頻率轉(zhuǎn)換速度快、頻譜純度高的特點(diǎn),因此設(shè)計(jì)上具有較高的難度。

2 頻率合成方案

??? 為了滿足快速頻率轉(zhuǎn)換的要求,設(shè)計(jì)采用了DDS+DSP頻率合成方案。通過(guò)設(shè)計(jì)良好的頻率基準(zhǔn)源和窄帶跟蹤式濾波器,提高頻譜純度,以達(dá)到差分跳頻系統(tǒng)對(duì)頻率合成器的要求。頻率合成器的設(shè)計(jì)框圖如圖2所示。DDS選用ADI公司生產(chǎn)的高性能AD9951芯片,DSP選用TI公司的TMS320C6418。

2.1 AD9951波形發(fā)生單元

??? AD9951是ADI公司生產(chǎn)的高度集成化芯片,采用了先進(jìn)的DDS技術(shù),結(jié)合內(nèi)部高速、高性能D/A轉(zhuǎn)換器,形成可編程、可靈活使用的頻率合成功能。AD9951的主要特點(diǎn)如下:400MHz內(nèi)部時(shí)鐘;集成化14位D/A輸出;32位頻率轉(zhuǎn)換字;良好的動(dòng)態(tài)性能,在160MHz輸出時(shí),具有大于80dB的SFDR;4~20倍可編程參考時(shí)鐘倍乘器;串行I/O控制;工作電壓1.8V,最大功耗僅為200mW。在設(shè)計(jì)時(shí)時(shí)鐘頻率" title="時(shí)鐘頻率">時(shí)鐘頻率選擇為400MHz,則頻率分辨率fmin=FTW/2n=400×106/232≈0.09Hz,因此滿足步進(jìn)為10Hz的指標(biāo)要求。

??? AD9951采用二線控制方式,將片選CSB低電平有效,數(shù)據(jù)線采用雙向SDIO,數(shù)據(jù)在時(shí)鐘SCLK上升沿寫(xiě)入,首先存于輸入緩沖器中,采用外部頻率更新方式,頻率更新信號(hào)FUD的上升沿有效。頻率合成器加電第一次送數(shù)時(shí),所有寄存器送相應(yīng)數(shù),以后改變頻率時(shí)只送頻率字寄存器04h,控制時(shí)序如圖3所示。可見(jiàn)要傳達(dá)32位的頻率控制字需要傳輸8位指令信息和32位數(shù)據(jù)信息,需要40個(gè)時(shí)鐘周期。

??? 控制芯片選擇TI公司生產(chǎn)的TMS320C6418。該芯片是32位的定點(diǎn)DSP,芯片內(nèi)部集成了1.5Mbit的片內(nèi)SRAM,具有豐富的外部接口;它使用了超長(zhǎng)指令字結(jié)構(gòu)(VLIW)體系結(jié)構(gòu),一個(gè)時(shí)鐘周期可同時(shí)處理8條相互獨(dú)立的指令,再加上流水線技術(shù),大大提高了并行處理能力和運(yùn)算能力。TMS320C6418參考時(shí)鐘為50MHz,內(nèi)部工作時(shí)鐘經(jīng)倍頻后達(dá)400MHz。通過(guò)SPI總線控制對(duì)AD9951進(jìn)行控制,采用20MHz的時(shí)鐘傳輸頻率,2μs即可完成頻率控制字的更新。

2.2 AD9951時(shí)鐘電路設(shè)計(jì)

??? DDS輸出信號(hào)的質(zhì)量取決于工作時(shí)鐘信號(hào)的頻譜質(zhì)量,DDS輸出信號(hào)的最高頻率受到時(shí)鐘頻率的限制(最高輸出頻率小于時(shí)鐘頻率的40%),并且DDS輸出信號(hào)頻率越接近上限,性能指標(biāo)越差。從提高頻率合成器的性能指標(biāo)來(lái)講,應(yīng)選擇400MHz低相位噪聲的時(shí)鐘做AD9951的頻率源,但市場(chǎng)上這種頻率源不但價(jià)格昂貴,而且性能指標(biāo)達(dá)不到要求。因此,在設(shè)計(jì)時(shí)選用了目前性能優(yōu)良、時(shí)鐘頻率不太高的晶體作為參考頻率的基準(zhǔn)源,采用低相位噪聲的鑒相器和窄帶壓控振蕩器作為鎖相環(huán),用于產(chǎn)生1600MHz的時(shí)鐘頻率。由于只作為點(diǎn)頻,因此在環(huán)路濾波器的參數(shù)選擇上主要考慮如何使輸出信號(hào)頻譜特性最優(yōu)。最后由分頻器進(jìn)行4分頻或5分頻,即輸出400MHz或320MHz時(shí)鐘信號(hào),設(shè)計(jì)匹配網(wǎng)絡(luò)將信號(hào)轉(zhuǎn)換為差分輸入,供AD9951作為時(shí)鐘頻率,能夠有效減少共模干擾。由于DDS雜散分布具有一定的規(guī)律性,通過(guò)不同的參考時(shí)鐘將這種規(guī)律性破壞,能夠有效抑制某些頻段的雜散電平信號(hào)。

2.3 濾波器設(shè)計(jì)

??? 由于DDS采用數(shù)字化技術(shù),最終合成信號(hào)是經(jīng)D/A轉(zhuǎn)換后得到的,其頻譜含有豐富的高次頻譜分量,必須將它們?yōu)V除,才能得到頻譜純凈的正弦波輸出,因此對(duì)濾波器的要求很高。在設(shè)計(jì)濾波器時(shí),由于發(fā)射信號(hào)為短波波段的1.6MHz~30MHz,頻率較低,因此頻譜質(zhì)量較好,在設(shè)計(jì)時(shí)只采用了七階橢圓濾波器,截止頻率為80MHz,后端通過(guò)隔離放大后輸出。收頻率輸出信號(hào)進(jìn)行了上變頻,其頻率為50MHz,因此實(shí)際輸出頻率達(dá)51.6MHz~80MHz,頻率相對(duì)較高,因此在七階橢圓濾波器的后端再接一個(gè)數(shù)字式跳頻調(diào)諧濾波器,該濾波器由數(shù)量較多的二進(jìn)制電容、電感組成,通過(guò)電子開(kāi)關(guān)連接所需電容、電感構(gòu)成濾波網(wǎng)絡(luò),通過(guò)DSP對(duì)其進(jìn)行控制。調(diào)諧頻率與輸出頻率保持一致,過(guò)濾帶非常窄,因此能夠達(dá)到比較理想的濾波效果。收、發(fā)頻率通過(guò)七階橢圓濾波后端的電子開(kāi)關(guān)進(jìn)行選擇,并由DSP進(jìn)行控制。收發(fā)進(jìn)行隔離,防止信號(hào)相互干擾。

3 電磁兼容性設(shè)計(jì)

??? 由于該頻率合成器是用于快速跳頻系統(tǒng),電臺(tái)的數(shù)據(jù)傳輸速度最高可達(dá)19.2Kb/s,對(duì)雜散和噪聲的抑制要求高,由于是高速數(shù)模混合電路,所以在設(shè)計(jì)時(shí)應(yīng)對(duì)電磁兼容性進(jìn)行充分考慮。PCB板設(shè)計(jì)為4層板。其中第2層為地平面,并將地平面在AD9951芯片下面分為數(shù)字地和模擬地。第3層為電源平面,分成AVDD、DVDD、1.8 V、3.3 V四部分,分別為AD9951的模擬部分、數(shù)字部分電路供電。其余外圍電路的電源單獨(dú)通過(guò)穩(wěn)壓塊提供。同時(shí)使用濾波器組件對(duì)全部頻段進(jìn)行電源濾波。PCB板的1、4、2層走信號(hào)線,走線盡可能短,防止在信號(hào)線上出現(xiàn)不必要的過(guò)孔以免損害信號(hào)電氣特性完整性。信號(hào)線間距D與線寬W之間滿足D≥3W以避免信號(hào)竄擾。按照傳輸線理論設(shè)計(jì)好帶線和微帶線,避免信號(hào)線連接處阻抗不匹配,防止反射。為了減少時(shí)鐘泄漏對(duì)其他信號(hào)的干擾,在屏蔽盒內(nèi)做出一個(gè)腔體把時(shí)鐘源與系統(tǒng)的其他部分進(jìn)行隔離。在PCB布線時(shí),盡量讓時(shí)鐘線遠(yuǎn)離其他信號(hào),同時(shí)在時(shí)鐘線的兩邊加地線屏蔽。

4 測(cè)試結(jié)果

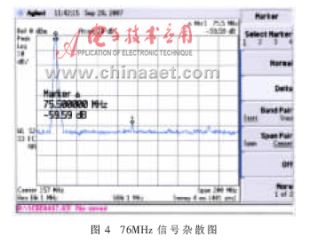

??? 通過(guò)圖4、圖5可以看出,該頻率合成器在76MHz處的雜散抑制和相位噪聲分別達(dá)到了-65dB和-113dBc/Hz@1KHz,諧波分量達(dá)到-59.6dB,完全滿足指標(biāo)要求。頻率轉(zhuǎn)換時(shí)間通過(guò)采用安捷倫公司生產(chǎn)5372A調(diào)制域分析儀進(jìn)行測(cè)量,實(shí)際頻率轉(zhuǎn)換時(shí)間僅為2μs。

?

??? 在基于AD9951的差分快速跳頻系統(tǒng)頻率合成器的研制過(guò)程中,為了降低相位噪聲、提高雜散抑制度和頻率轉(zhuǎn)換速度,在電磁兼容、電路布局以及PCB設(shè)計(jì)等方面進(jìn)行了精心的考慮,達(dá)到了較為理想的性能指標(biāo)。

?

參考文獻(xiàn)

[1] 費(fèi)元春,蘇廣川,米紅,等.寬帶雷達(dá)信號(hào)產(chǎn)生技術(shù).北京:國(guó)防工業(yè)出版社,2002.

[2] 謝仁宏,是湘全.基于DDS的低相噪頻率綜合源設(shè)計(jì).現(xiàn)代雷達(dá),2003,25(12):41-43.

[3] 夏永祥,郭德淳,余軍,等.基于AD9858的快速捷變頻頻率合成器的設(shè)計(jì).現(xiàn)代雷達(dá),2005,27(7).

[4] 李明,戚仁華,朱紅琛.短波寬帶快速跳頻通信技術(shù)研究.通信技術(shù),2000,110(3).