摘 要: 介紹了鎖相環(huán)的組成結(jié)構(gòu),詳細(xì)分析了鎖相環(huán)系統(tǒng)各部分產(chǎn)生的相位噪聲,結(jié)合分析結(jié)果給出了一種以雙鎖相環(huán)集成芯片LMK04031為核心實(shí)現(xiàn)125 MHz時(shí)鐘源的頻率合成器的設(shè)計(jì)方法,并給出關(guān)鍵電路的設(shè)計(jì)。通過(guò)調(diào)試,產(chǎn)生高性能的頻率源,為鎖相頻率合成的工程應(yīng)用提供參考。

關(guān)鍵詞: LMK04031;鎖相環(huán);頻率合成器;相位噪聲

0 引言

頻率合成器為現(xiàn)代電子通信系統(tǒng)提供高穩(wěn)定高性能的頻率源,其好壞直接影響通信系統(tǒng)的質(zhì)量。產(chǎn)生頻率源的頻率合成技術(shù)包括直接頻率合成、直接數(shù)字頻率合成、鎖相環(huán)頻率合成和混合頻率合成。本文介紹鎖相環(huán)系統(tǒng),對(duì)其進(jìn)行線性相位噪聲分析,給出某系統(tǒng)中采用級(jí)聯(lián)鎖相環(huán)芯片LMK04031產(chǎn)生125 MHz時(shí)鐘源的設(shè)計(jì)方法及測(cè)試結(jié)果。

1 鎖相環(huán)介紹

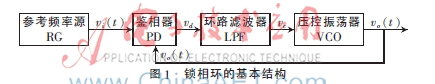

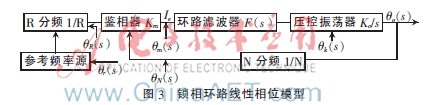

鎖相環(huán)(PLL)是一個(gè)閉環(huán)控制系統(tǒng)。主要包括參考頻率(RG)、鑒相器(PD)、環(huán)路濾波器(LPF)和壓控振蕩器(VCO)幾個(gè)部分,如圖1所示。通過(guò)將參考頻率源產(chǎn)生的信號(hào)vi(t)與壓控振蕩器輸出反饋回來(lái)的信號(hào)vo(t)在鑒相器中進(jìn)行相位比較,產(chǎn)生一個(gè)相關(guān)的電壓信號(hào)vd,經(jīng)過(guò)環(huán)路濾波濾除毛刺和噪聲后變?yōu)関c,控制壓控振蕩器輸出頻率的變化,形成一個(gè)負(fù)反饋過(guò)程。設(shè)參考頻率為i,輸出頻率為o,在環(huán)路鎖定時(shí),進(jìn)入鑒相器中的兩個(gè)信號(hào)頻率相等。一般的鎖相環(huán)電路中,為了得到更高的輸出頻率,將參考頻率R分頻,輸出頻率N分頻后送入鑒相器中進(jìn)行相位比較,則有:

即輸出頻率為參考頻率的N/R倍。當(dāng)今市場(chǎng)上的鎖相環(huán)芯片通常集成N分頻器、R分頻器、鑒相器和VCO等部分。通過(guò)選擇合適的參考頻率、控制N和R的值便可以得到所需要的輸出頻率。為了獲得較高性能的頻率源,也可以采用分立的鑒相器、VCO和分頻器等器件。

鎖相環(huán)可以分為模擬鎖相環(huán)、數(shù)字鎖相環(huán)和數(shù)模混合鎖相環(huán)。數(shù)模鎖相環(huán)又稱電荷泵鎖相環(huán),與模擬鎖相環(huán)相比具有跟蹤范圍廣、捕獲時(shí)間短和成本低的優(yōu)點(diǎn),現(xiàn)今集成鎖相環(huán)芯片通常采用電荷泵鎖相環(huán)。通常內(nèi)部集成鑒相器、分頻器和壓控振蕩器。

2 相位噪聲分析

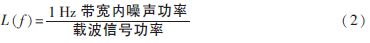

在偏離載波foffset處相位噪聲定義為在該頻率處1 Hz帶寬內(nèi)的信號(hào)功率與載波信號(hào)的功率比值,可以用式(2)表示:

如圖2所示,載波信號(hào)功率為Ps(dBm),偏移載波foffset處1 Hz內(nèi)信號(hào)功率為Pn(dBc/Hz),那么根據(jù)式(2),相位噪聲可以表示為:

L(f)(dBc/Hz)=Pn(dBc/Hz)-Ps(dBm)(3)

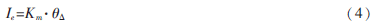

鎖相環(huán)的相位噪聲來(lái)源于各個(gè)組成部分,包括參考源、鑒相器、壓控振蕩器及其電路等。鎖定條件下,當(dāng)環(huán)路帶寬小于鑒相頻率的十分之一時(shí),鎖相環(huán)系統(tǒng)可以看成一個(gè)線性系統(tǒng)。對(duì)鎖相環(huán)路進(jìn)行線性分析,可以得到各部分對(duì)輸出相位噪聲的影響。鑒相器通過(guò)比較輸入信號(hào)與反饋信號(hào),產(chǎn)生一個(gè)相位差,與鑒相增益Km相乘,得到誤差電流Ie:

再經(jīng)過(guò)環(huán)路濾波器轉(zhuǎn)化為直流控制電壓Vc:

Vc=Ie·F(s)(5)

鎖相環(huán)路線性化模型如圖3所示。根據(jù)圖中各模塊的傳遞函數(shù),可以得到系統(tǒng)的前向增益:

反饋增益:

系統(tǒng)閉環(huán)傳遞函數(shù)可以寫(xiě)為:

![6BS0R0D68N})ZV@K]S][SML.png 6BS0R0D68N})ZV@K]S][SML.png](http://files.chinaaet.com/images/2016/01/29/6358969417429400003442975.png)

式(8)也可以表示參考頻率源部分的噪聲對(duì)輸出噪聲產(chǎn)生影響的傳遞函數(shù)。利用傳遞函數(shù)對(duì)系統(tǒng)進(jìn)行噪聲分析,可以得到R分頻、N分頻、鑒相器和VCO對(duì)系統(tǒng)輸出噪聲的影響。

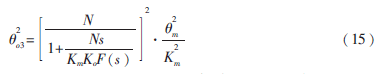

R分頻噪聲傳遞函數(shù):

N分頻噪聲傳遞函數(shù):

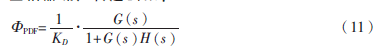

鑒相器噪聲傳遞函數(shù):

VCO噪聲傳遞函數(shù):

根據(jù)式(8),可以得到參考頻率源相位噪聲對(duì)系統(tǒng)輸出相位噪聲的影響:

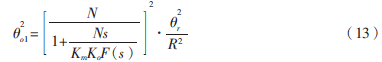

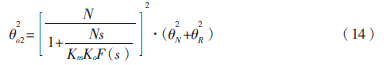

分頻器R和N產(chǎn)生的相位噪聲對(duì)系統(tǒng)的影響:

鑒相器產(chǎn)生的相位噪聲對(duì)系統(tǒng)的影響:

壓控振蕩器產(chǎn)生的相位噪聲對(duì)系統(tǒng)的影響:

系統(tǒng)各部分相位噪聲對(duì)輸出相噪的影響:

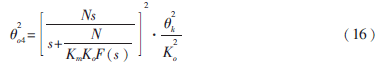

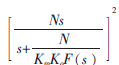

式(13)~(15)有一個(gè)公共因子![DDK$K0N(I7SB[C]~H[7B$%C.png DDK$K0N(I7SB[C]~H[7B$%C.png](http://files.chinaaet.com/images/2016/01/29/6358969426372900009116574.png) ,對(duì)于頻率響應(yīng)表現(xiàn)為低通特性,因此參考源、分頻器和鑒相器的相位噪聲主要表現(xiàn)在低頻中,而式(16)的因子

,對(duì)于頻率響應(yīng)表現(xiàn)為低通特性,因此參考源、分頻器和鑒相器的相位噪聲主要表現(xiàn)在低頻中,而式(16)的因子 表現(xiàn)為高通特性,因而VCO的相位噪聲在高頻時(shí)表現(xiàn)明顯。因此為達(dá)到最小的相位噪聲,系統(tǒng)的環(huán)路帶寬應(yīng)選為參考源噪聲功率曲線與VCO噪聲功率曲線相交處。

表現(xiàn)為高通特性,因而VCO的相位噪聲在高頻時(shí)表現(xiàn)明顯。因此為達(dá)到最小的相位噪聲,系統(tǒng)的環(huán)路帶寬應(yīng)選為參考源噪聲功率曲線與VCO噪聲功率曲線相交處。

公共因子對(duì)N的變化表現(xiàn)為隨N的增大而增大,因此分頻器N應(yīng)選擇較小的數(shù),等價(jià)于應(yīng)選擇較大的鑒相頻率。同樣,參數(shù)Km和Ko的增大都會(huì)導(dǎo)致輸出相噪的增大,因此應(yīng)選調(diào)諧系數(shù)較小的VCO。鑒相器通常用乘法器代替,選擇鑒相增益較小的器件會(huì)減小系統(tǒng)相位噪聲,通過(guò)環(huán)路濾波器抑制相位噪聲。一般地,環(huán)路濾波器的帶寬選為鑒相頻率的1/10~1/20。

3 鎖相環(huán)電路設(shè)計(jì)

頻率源的質(zhì)量直接影響通信系統(tǒng)的好壞。評(píng)價(jià)頻率源的指標(biāo)包括相位噪聲、雜散、穩(wěn)定度等。因此設(shè)計(jì)過(guò)程中應(yīng)從器件選型、環(huán)路濾波、電路布局、分頻器配置多個(gè)方面進(jìn)行考慮。項(xiàng)目要求獲得125 MHz高穩(wěn)定、低噪聲、低雜散的信號(hào)。鎖相環(huán)芯片選擇TI公司的LMK04031,參考頻率源選擇項(xiàng)目中GPS高穩(wěn)定時(shí)鐘模塊輸出的10 MHz信號(hào)。

3.1 參考頻率源選擇

參考頻率源為鎖相環(huán)路提供一個(gè)標(biāo)準(zhǔn),因此它的好壞直接影響輸出頻率的準(zhǔn)確性、穩(wěn)定度等指標(biāo)。一般采用晶體振蕩器作為參考源。晶振可以分為普通晶振、溫補(bǔ)晶振(TCXO)、電壓控制晶振(VCXO)、恒溫晶振(OCXO)等幾種類型。普通晶振價(jià)格低、穩(wěn)定度較差;電壓控制晶振輸出頻率可以隨著電壓變化而微小變化,通過(guò)電壓調(diào)節(jié)輸出頻率的偏移,解決晶振輸出頻率隨時(shí)間而變化的問(wèn)題;溫補(bǔ)晶振和恒溫晶振都解決了晶振穩(wěn)定度隨溫度變化而產(chǎn)生變化的問(wèn)題,其中恒溫晶振輸出頻率隨溫度變化最小,穩(wěn)定度最高,價(jià)格也最昂貴。鎖相環(huán)頻率合成實(shí)質(zhì)上是對(duì)參考頻率進(jìn)行倍頻,倍頻過(guò)程會(huì)對(duì)相位噪聲產(chǎn)生影響,見(jiàn)式(13)。因此選擇高穩(wěn)定低相噪的參考源可以改善系統(tǒng)的輸出相位噪聲。應(yīng)根據(jù)工程指標(biāo)選擇合適的參考時(shí)鐘。結(jié)合成本與指標(biāo)考慮,本設(shè)計(jì)采用一款TCXO作為參考時(shí)鐘。

3.2 LMK04031介紹

LMK04031是TI公司生產(chǎn)的具有級(jí)聯(lián)PLL的低噪聲時(shí)鐘抖動(dòng)清潔器。它內(nèi)部集成兩個(gè)鎖相環(huán):鎖相環(huán)1通過(guò)接收外接參考頻率源的信號(hào),進(jìn)行R1分頻后,與反饋回鑒相器的外接VCO或VCXO的N1分頻信號(hào)進(jìn)行相位比較,鎖定后輸出的穩(wěn)定頻率信號(hào)進(jìn)入鎖相環(huán)2中作為參考,再進(jìn)行R2分頻,與內(nèi)部集成的VCO的N2分頻信號(hào)進(jìn)行相位比較。VCO可輸出五路差分信號(hào),并且可以進(jìn)行以2為步進(jìn)的2~510分頻,因而可以輸出5路不同頻率信號(hào),同時(shí)每個(gè)通道可以進(jìn)行以150為步進(jìn)的0~2 250 ps時(shí)延。芯片封裝采用48腳WQFN封裝,尺寸小,功耗低,使用方便。

寄存器的值可以通過(guò)TI公司軟件CODELOADER確定。在CODELOADER中輸入一系列需要設(shè)置的參數(shù),便可得到相應(yīng)的寄存器值。管腳PLL_MUX可以配置成不同的內(nèi)容來(lái)獲得芯片內(nèi)部的狀態(tài)。例如配置為PLL1鎖定高電平輸出,那么此管腳便在PLL1鎖定時(shí)輸出高電平,沒(méi)有鎖定時(shí)為低電平。也可以配置為PLL2鎖定指示、N分頻輸出、R分頻輸出等狀態(tài)。在調(diào)試的過(guò)程中通過(guò)配置此管腳來(lái)確定芯片是否處于正常工作狀態(tài)。本設(shè)計(jì)采用FPGA對(duì)寄存器進(jìn)行配置。

3.3 環(huán)路濾波器設(shè)計(jì)

為了獲得較好的相噪性能,環(huán)路濾波選擇無(wú)源環(huán)路濾波器,因?yàn)椴缓性雌骷虼艘氲脑肼曒^有源環(huán)路濾波少。鎖相環(huán)路1的參考頻率源為T(mén)CXO,噪聲較小,因此在鎖相環(huán)路1中采用較大的環(huán)路帶寬。而在鎖相環(huán)路2中,參考頻率源為VCXO的鎖定輸出,根據(jù)上述討論,各部分相位噪聲疊加對(duì)整體輸出有影響,因此環(huán)路2中的帶寬選擇較小一些。采用ADI公司的環(huán)路設(shè)計(jì)軟件ADISIMPLL進(jìn)行環(huán)路設(shè)計(jì),可以根據(jù)環(huán)路帶寬、鑒相頻率、相位裕度這三個(gè)參數(shù)確定環(huán)路濾波器。環(huán)路1中,參考頻率為10 MHz OCXO,R1分頻和N1分頻分別為20和50,輸出選擇25 MHz VCXO,鑒相頻率為 500 kHz,環(huán)路帶寬選為鑒相頻率的1/10。因此環(huán)路濾波器帶寬選定為50 kHz,設(shè)計(jì)電路圖見(jiàn)圖4。LMK04031內(nèi)部VCO頻率為1 430~1 570 MHz,將輸出設(shè)為1 500 MHz,經(jīng)過(guò)VCO DIVIDER進(jìn)行3分頻,再進(jìn)入多通道輸出進(jìn)行4分頻便可得到125 MHz輸出。環(huán)路2中的參考輸入為環(huán)路1中VCXO的25 MHz輸出,VCO輸出定1 500 MHz,R2分頻和N2分頻分別為200 Hz和4 000 Hz,鑒相頻率為125 kHz,環(huán)路濾波器2的帶寬為12.5 kHz,設(shè)計(jì)電路圖見(jiàn)圖5。

3.4 電路設(shè)計(jì)

鎖相環(huán)系統(tǒng)對(duì)噪聲十分敏感,因此對(duì)芯片的供電采用線性穩(wěn)壓電源芯片。電路的布局應(yīng)注意模擬部分與數(shù)字部分隔離開(kāi)來(lái),減小數(shù)字部分對(duì)模擬部分的影響。環(huán)路的布線應(yīng)盡可能短,高頻線要注意阻抗控制。

4 電路調(diào)試及結(jié)果

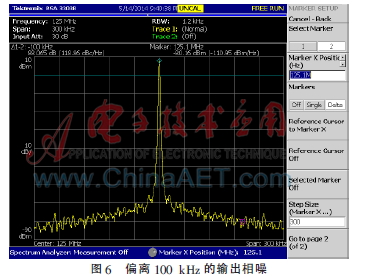

級(jí)聯(lián)鎖相環(huán)的調(diào)試可以分別進(jìn)行。測(cè)試中,通過(guò)更改不同寄存器的數(shù)據(jù),使得PLL_MUX引腳輸出R分頻或N分頻的結(jié)果,利用示波器測(cè)試輸出的頻率是否為設(shè)定的鑒相頻率,便可得知寄存器是否被正確賦值。通過(guò)PLL_MUX輸出鎖定指示狀態(tài)可以判斷環(huán)路是否鎖定。兩級(jí)鎖相環(huán)可分別調(diào)試。設(shè)計(jì)要求輸出125 MHz,在偏離100 kHz處測(cè)量其相位噪聲,為-110.95 dBc/Hz,如圖6所示,達(dá)到了設(shè)計(jì)的要求。

5 結(jié)束語(yǔ)

本文首先介紹了鎖相環(huán)的結(jié)構(gòu)組成,之后通過(guò)對(duì)系統(tǒng)各部分模塊噪聲的線性分析,得出鎖相環(huán)電路設(shè)計(jì)過(guò)程中減小相位噪聲的手段:選擇性能良好的參考源、選擇合適的環(huán)路帶寬和良好的電路布局布線,最后通過(guò)基于LMK04031芯片設(shè)計(jì)電路的實(shí)例給出了鎖相環(huán)設(shè)計(jì)的一般性方法。

參考文獻(xiàn)

[1] 張厥盛.鎖相與頻率合成技術(shù)[M].成都:電子科技大學(xué)出版社,1995.

[2] 莊卉,黃蘇華,袁國(guó)春.鎖相與頻率合成技術(shù)[M].北京:氣象出版社,1996.

[3] Texas Instruments Inc. LMK04000 family low-noise clock jitter cleaner with Cascaded PLLs, Technical Datasheet[Z].2011.

[4] 張濤.鎖相環(huán)頻率合成器建模、設(shè)計(jì)與實(shí)現(xiàn)[D].武漢:華中科技大學(xué),2006.

[5] CAST.鎖相環(huán)常見(jiàn)問(wèn)題解答[Z]. Analog Devices Inc, 2013.