DDR3存儲(chǔ)器系統(tǒng)可以大大提升各種數(shù)據(jù)處理應(yīng)用的性能。然而,和過去幾代(DDR和DDR2)器件相比,DDR3存儲(chǔ)器器件有了一些新的要求。為了充分利用和發(fā)揮DDR3存儲(chǔ)器的優(yōu)點(diǎn),使用一個(gè)高效且易于使用的DDR3存儲(chǔ)器接口控制器是非常重要的。視屏處理應(yīng)用就是一個(gè)很好的示例,說明了DDR3存儲(chǔ)器系統(tǒng)的主要需求以及在類似數(shù)據(jù)流處理系統(tǒng)中DDR3接口所需的特性。

視頻處理系統(tǒng)將對(duì)于數(shù)據(jù)帶寬的要求推高到了極致:系統(tǒng)可以處理越多的數(shù)據(jù),就具有越高的性價(jià)比。視頻聚合器和路由器可并行處理多個(gè)視頻流,因此對(duì)于匹配數(shù)據(jù)處理能力和視頻帶寬的需求就成為了設(shè)計(jì)的一大挑戰(zhàn)。FPGA可通過在單個(gè)FPGA中實(shí)現(xiàn)多個(gè)視頻處理器來提供強(qiáng)大的處理能力。那么現(xiàn)在的挑戰(zhàn)就變成了要使數(shù)據(jù)盡快且高效地從FPGA進(jìn)出。DDR3存儲(chǔ)器系統(tǒng)在大多數(shù)情況下可以為這些基于FPGA的系統(tǒng)提供足夠的帶寬。

視頻處理設(shè)計(jì)說明

我們的目標(biāo)視頻處理設(shè)計(jì)將同時(shí)處理四個(gè)視頻源,將視頻數(shù)據(jù)轉(zhuǎn)換和壓縮為一種可以通過PCI Express接口傳輸?shù)酱鎯?chǔ)器hub的格式。系統(tǒng)的主要功能塊如圖1所示。

圖1:視頻處理器框圖

FPGA獲取并緩存四個(gè)視頻源的數(shù)據(jù)流。這些FIFO緩沖器由DDR3存儲(chǔ)器控制器清空并保存在DDR3存儲(chǔ)器中。一旦一個(gè)完整的視頻數(shù)據(jù)包存儲(chǔ)完畢,視頻處理器會(huì)向DDR3存儲(chǔ)器控制器申請(qǐng)數(shù)據(jù),存儲(chǔ)器控制器讀取數(shù)據(jù)并將其傳到視頻處理器。視頻處理器對(duì)視頻數(shù)據(jù)進(jìn)行格式化和壓縮,并通過DDR3存儲(chǔ)器控制器寫回存儲(chǔ)器。當(dāng)一個(gè)視頻數(shù)據(jù)包全部處理完畢,并準(zhǔn)備通過PCI Express接口進(jìn)行傳輸,DDR3存儲(chǔ)器控制器從視頻處理器獲取數(shù)據(jù)并將其傳到PCI Express接口。

DDR3存儲(chǔ)器接口控制器概述

從零開始設(shè)計(jì)一個(gè)DDR3存儲(chǔ)器控制器是非常困難的。需要考慮許多特性之間的權(quán)衡和互相影響。使用一個(gè)經(jīng)驗(yàn)證的IP核可以省去了大量的開發(fā)、測(cè)試和調(diào)試時(shí)間,否則就需要花費(fèi)許多時(shí)間來進(jìn)行in-house設(shè)計(jì)開發(fā)。一個(gè)經(jīng)驗(yàn)證的IP核還可以減少后續(xù)支持的負(fù)擔(dān),因?yàn)檫@將由專門的開發(fā)人員來支持。最重要的是,使用一個(gè)經(jīng)驗(yàn)證的IP核可以使設(shè)計(jì)師將精力集中在其設(shè)計(jì)的獨(dú)特特性上,從而向最終客戶交付高價(jià)值的產(chǎn)品設(shè)計(jì)。例如,LatticeECP3 DDR3存儲(chǔ)器控制器IP核已經(jīng)通過了一個(gè)第三方驗(yàn)證套件的驗(yàn)證。該IP核使用LatticeECP3 I/O協(xié)議板來實(shí)現(xiàn)并通過全部測(cè)試。

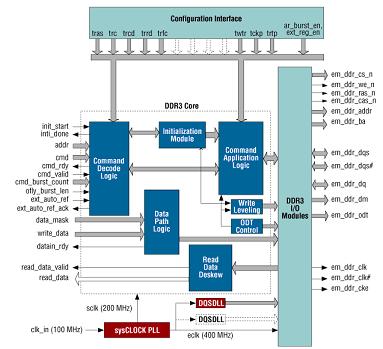

圖2展示了一個(gè)存儲(chǔ)器控制器的框圖。圖最上面的配置接口用于設(shè)置設(shè)計(jì)的各個(gè)選項(xiàng)。DDR3 I/O模塊使用I/O 基元來實(shí)現(xiàn)。指令譯碼模塊根據(jù)每個(gè)bank和每一行,對(duì)用戶指令進(jìn)行譯碼,產(chǎn)生內(nèi)部存儲(chǔ)器指令序列。指令應(yīng)用模塊將每條指令序列轉(zhuǎn)換為滿足目標(biāo)存儲(chǔ)器件功能和時(shí)序要求的存儲(chǔ)器指令。數(shù)據(jù)通路模塊與DDR3 I/O模塊連接,并且在讀操作時(shí)產(chǎn)生讀數(shù)據(jù)和讀取數(shù)據(jù)有效信號(hào)。讀數(shù)據(jù)偏移校正模塊對(duì)齊每一條8位數(shù)據(jù)線上的數(shù)據(jù),調(diào)整任何可能的時(shí)鐘偏移。這使得用戶端的讀數(shù)據(jù)總線與系統(tǒng)時(shí)鐘準(zhǔn)確校準(zhǔn)。寫調(diào)整模塊為了正確的捕獲數(shù)據(jù),調(diào)整了DQS對(duì)CK的關(guān)系。ODT塊通過為任意或所有DDR3 SDRAM器件提供單獨(dú)的終端阻抗控制,提高了存儲(chǔ)器通道的信號(hào)完整性。

圖2:DDR3存儲(chǔ)器控制器IP核框圖

DDR3存儲(chǔ)器控制器應(yīng)支持廣泛的存儲(chǔ)器速率和配置,以滿足各種應(yīng)用需求。例如,Lattice ECP3 DDR3存儲(chǔ)器控制器支持高達(dá)800Mb/s的DDR3器件速率,8至64位的存儲(chǔ)器數(shù)據(jù)通道(帶有x8或x16 DDR3器件),并且同時(shí)支持雙列直插式存儲(chǔ)器塊(Dual Inline Memory Modules,DIMM)和單個(gè)存儲(chǔ)器的器件。

DDR3存儲(chǔ)器控制器必須為各種存儲(chǔ)器訪問實(shí)現(xiàn)不同的時(shí)序要求。一些要求對(duì)于我們的目標(biāo)應(yīng)用來說非常重要,包括以下幾個(gè)方面:

DDR3存儲(chǔ)器使用“類似cache”的bank進(jìn)行組織,每個(gè)器件帶有8個(gè)bank。訪問最近工作(打開)的bank比訪問未工作的(關(guān)閉)的bank速度快。 可使用4位、8位或交叉存取方式進(jìn)行突發(fā)(burst)模式讀訪問。 根據(jù)存儲(chǔ)器速率和用戶設(shè)置,CAS和寫延遲都是可變的。從讀請(qǐng)求轉(zhuǎn)換為寫請(qǐng)求需要額外的延遲時(shí)間,因?yàn)殡p向的數(shù)據(jù)總線必須改變傳輸方向。

針對(duì)視頻處理的IP核實(shí)現(xiàn)

為了使存儲(chǔ)器數(shù)據(jù)帶寬和效率最大化,針對(duì)視頻處理設(shè)計(jì)的IP核實(shí)現(xiàn)需根據(jù)DDR3存儲(chǔ)器特性使用相匹配的算法。下面列出了一些重要的實(shí)現(xiàn)考慮。

使用突發(fā)(Burst)模式的數(shù)據(jù)訪問

DDR3存儲(chǔ)器可通過突發(fā)模式訪問,突發(fā)模式在數(shù)據(jù)以數(shù)據(jù)塊形式存放(如視頻處理應(yīng)用)的應(yīng)用中是非常有效的。同樣,通過將視頻數(shù)據(jù)以優(yōu)化的方式放入8個(gè)bank中,數(shù)據(jù)傳輸帶寬和之后的數(shù)據(jù)處理率可維持在一個(gè)高速的水平。在我們的示例中有4個(gè)視頻源,因此如果我們?yōu)槊總€(gè)視頻源使用2個(gè)bank(一個(gè)用作存儲(chǔ)緩沖器,另一個(gè)用作處理緩沖器),這將使DDR3保持高傳輸效率。高效的DDR3存儲(chǔ)器控制器應(yīng)當(dāng)基于每個(gè)bank的狀態(tài),使用最快的訪問時(shí)間處理突發(fā)讀和寫。此外,視頻處理器將事務(wù)分組,使總線換向時(shí)間最小化并進(jìn)一步提高存儲(chǔ)器帶寬。

更高帶寬的數(shù)據(jù)緩沖分配

來自視頻源1的數(shù)據(jù)可通過FIFO讀取并存儲(chǔ)到DDR3存儲(chǔ)器中的Bank 1。這將是一個(gè)只寫操作,可以使用突發(fā)模式來保持傳輸?shù)母咝АR坏┮粋€(gè)數(shù)據(jù)包保存到Bank 1,視頻處理器可從Bank 1讀出數(shù)據(jù),對(duì)其進(jìn)行操作并存入Bank 2。這些操作都可使用突發(fā)模式,因此總線換向的花銷僅占用存儲(chǔ)器帶寬的很小的百分比。一旦Bank 2中的數(shù)據(jù)經(jīng)過處理后可被讀出,還是使用突發(fā)模式,然后發(fā)送到PCI Express接口,再傳輸?shù)絟ub。盡可能地保持存儲(chǔ)器bank為打開狀態(tài)可使得控制器使用最短的存儲(chǔ)器訪問時(shí)間,從而提高了效率。

使用交叉存取的并行數(shù)據(jù)處理

數(shù)據(jù)讀可在bank之間切換或交叉存取,而無需大量延遲或總線換向時(shí)間。因此,只要處理硬件能夠支持,多個(gè)視頻流可通過視頻處理器同時(shí)處理。當(dāng)處理好的數(shù)據(jù)寫回DDR3存儲(chǔ)器時(shí),多個(gè)寫操作也可以通過交叉存取來提高帶寬。一個(gè)易于使用和可預(yù)測(cè)的存儲(chǔ)器控制器,如:ECP3 DDR3存儲(chǔ)器控制器,在用戶基于其對(duì)數(shù)據(jù)處理的基本算法的了解的情況下來分配存儲(chǔ)器緩沖區(qū)時(shí),可以最小的硬件和軟件開銷來實(shí)現(xiàn)最大的帶寬。

刷新和初始化

因?yàn)镈DR3存儲(chǔ)器中的數(shù)據(jù)必須定期進(jìn)行刷新,一些存儲(chǔ)器訪問必須分配給刷新操作。DDR3控制器應(yīng)支持自動(dòng)刷新指令隊(duì)列,它可能是深度為8的指令集,可以作為一個(gè)指令組來執(zhí)行,以使效率最大化。DDR3器件的初始化過程是非常繁復(fù)的并且很容易出錯(cuò),特別是在手動(dòng)執(zhí)行時(shí)。DDR3控制器的初始化模塊應(yīng)該通過與用戶邏輯的一次簡(jiǎn)單的握手,自動(dòng)初始化存儲(chǔ)器,從而極大地簡(jiǎn)化了接口設(shè)計(jì)。

流水線的指令處理

存儲(chǔ)器控制器應(yīng)當(dāng)使用指令流水線來提高吞吐率,在當(dāng)前指令出現(xiàn)在存儲(chǔ)器接口時(shí),譯碼隊(duì)列中的下一條指令。這種方法提供了高于雙周期存儲(chǔ)器控制器100%的吞吐量。

功耗管理

在一些DDR3應(yīng)用中,功耗管理可能是一個(gè)需要考慮問題。在一些設(shè)計(jì)中,使用Power Down指令是非常有用的。該指令在沒有數(shù)據(jù)訪問需求的時(shí)候,降低功耗。在power down狀態(tài)下,器件功耗的降低可達(dá)90%。萊迪思DDR3存儲(chǔ)器控制器支持該指令。此外,萊迪思ECP3為帶有SERDES和高速接口,如DDR3存儲(chǔ)器控制器的應(yīng)用提供最低功耗的可編程解決方案。

設(shè)計(jì)和驗(yàn)證流程

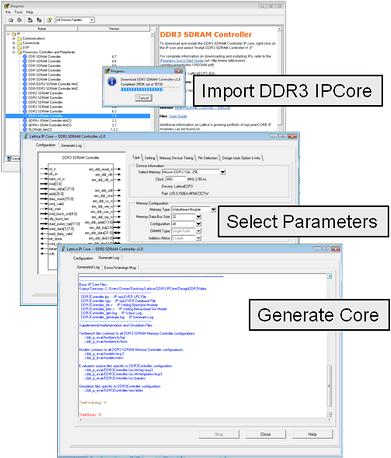

DDR3存儲(chǔ)器控制器IP核必須易于配置、生成并應(yīng)用到一個(gè)目標(biāo)設(shè)計(jì)中。使用圖形化用戶界面(GUI)來配置各種DDR3控制器參數(shù)是一種簡(jiǎn)便的方法,為目標(biāo)系統(tǒng)快速創(chuàng)建正確的控制器。所有的參數(shù)都需要確定,如:存儲(chǔ)器寬度、深度、速度和延遲。每一類配置參數(shù)都有其獨(dú)立的選項(xiàng)卡,有助于將設(shè)計(jì)任務(wù)分為一個(gè)個(gè)可管理的“任務(wù)塊”。一旦參數(shù)選定,生成代碼(用VHDL或Verilog)和生成相應(yīng)的測(cè)試基準(zhǔn)應(yīng)當(dāng)是比較容易的。

例如,萊迪思IPexpress工具只需三個(gè)步驟,如圖3所示,在ispLEVER設(shè)計(jì)軟件中創(chuàng)建ECP3 DDR3存儲(chǔ)器控制器IP核:

1)從萊迪思網(wǎng)站下載IPexpress工具并將IP核導(dǎo)入。

2)IP核參數(shù)可通過每個(gè)配置組對(duì)應(yīng)的選項(xiàng)卡進(jìn)行選擇,配置組有:類型、設(shè)置、時(shí)序、引腳和設(shè)計(jì)工具。

3)基于Verilog或VHDL的IP核和測(cè)試基準(zhǔn)一起生成,包括頂層、監(jiān)視器、指令生成器、用于Aldec或ModelSim的配置和腳本文件。

圖3:下載、配置和生成IP核設(shè)計(jì)流程

小結(jié)

在數(shù)據(jù)處理應(yīng)用的設(shè)計(jì)中,如本文中視頻處理的例子,當(dāng)存儲(chǔ)器具有足夠的帶寬時(shí),可以充分利用FPGA的并行處理能力的優(yōu)勢(shì)。DDR3存儲(chǔ)器具有靈活、易于使用的存儲(chǔ)器控制器,如:萊迪思ECP3 DDR3存儲(chǔ)器控制器IP核,加上正確使用突發(fā)模式訪問、數(shù)據(jù)緩沖器分配和存儲(chǔ)器交叉存取可以大大加快數(shù)據(jù)處理速度。此外,一個(gè)經(jīng)驗(yàn)證的IP核與可靠的設(shè)計(jì)和驗(yàn)證環(huán)境也加速了這些應(yīng)用的上市。