USB(通用串行總線)作為一種外設(shè)連接技術(shù),是計(jì)算機(jī)外設(shè)連接技術(shù)的重大變革,USB具有速度快、通用性好、擴(kuò)展性強(qiáng)、功耗低、穩(wěn)定、易開(kāi)發(fā)等眾多優(yōu)點(diǎn),在實(shí)踐中獲得了廣泛的應(yīng)用,逐步成為PC機(jī)的一種標(biāo)準(zhǔn)接口。USB接口控制芯片是實(shí)現(xiàn)USB設(shè)備與主機(jī)建立通信所必須的芯片,目前國(guó)內(nèi)的USB開(kāi)發(fā)者所采用的芯片都是由國(guó)外的芯片商所提供,如Cypress、NEC、Motorola等大的IC設(shè)計(jì)公司,價(jià)格較貴。由于USB的廣泛應(yīng)用,國(guó)內(nèi)外眾多科研機(jī)構(gòu)和集成電路設(shè)計(jì)公司都把目光投向USB這項(xiàng)具有廣闊市場(chǎng)前景的技術(shù)。USB內(nèi)核(USB Core)是USB接口控制芯片的關(guān)鍵模塊,設(shè)計(jì)一個(gè)穩(wěn)定、高速的USB內(nèi)核更是芯片成功推向市場(chǎng)的前提。

1 USB通信原理

USB通信邏輯上分成了3層:信號(hào)層、協(xié)議層和數(shù)據(jù)層。信號(hào)層用來(lái)實(shí)現(xiàn)在USB設(shè)備和主機(jī)的物理連接之間傳輸位信息流的信息。邏輯層用來(lái)實(shí)現(xiàn)在USB設(shè)備和USB主機(jī)端的協(xié)議軟件之間傳輸包字節(jié)流的信息,它們?cè)谛盘?hào)層被編碼成NRZI位信息后傳送出去。數(shù)據(jù)傳輸層用來(lái)實(shí)現(xiàn)在USB主機(jī)端的客戶(hù)端驅(qū)動(dòng)程序和設(shè)備端的功能接口之間傳輸有一定意義的信息,這些信息在協(xié)議層被打包成包格式。

1.1 傳輸?shù)幕締卧?br />

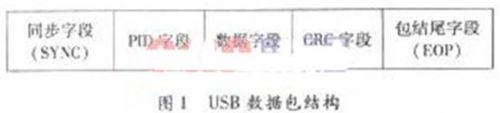

包(Packet)是USB系統(tǒng)中信息傳輸?shù)幕締卧=Y(jié)構(gòu),如圖1所示,根據(jù)USB規(guī)范,包的類(lèi)型有:令牌包、數(shù)據(jù)包、握手包和專(zhuān)用包。

USB總線操作(通訊過(guò)程)都可以歸結(jié)為3種包的傳輸:令牌包、數(shù)據(jù)包和應(yīng)答包。任何操作都是從主機(jī)開(kāi)始的,主機(jī)以預(yù)先排好的時(shí)序,發(fā)出一個(gè)描述操作類(lèi)型、方向、外設(shè)地址以及端點(diǎn)號(hào),稱(chēng)之為令牌包Foken Packet。然后由在令牌中指定的數(shù)據(jù)發(fā)送者發(fā)出一個(gè)數(shù)據(jù)包Data Packet或者報(bào)告它沒(méi)有數(shù)據(jù)可以傳輸。而數(shù)據(jù)的目的地一般要以一個(gè)應(yīng)答包Handshake Packet做出響應(yīng)表明傳輸是否成功。

1.2 事務(wù)處理

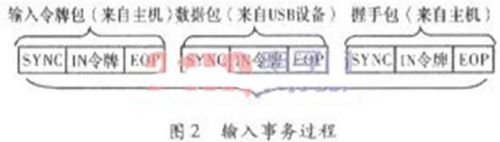

事務(wù)處理(Transaction)是指USB總線上數(shù)據(jù)信息的一次接收或發(fā)送的處理過(guò)程。事務(wù)處理的類(lèi)型包括輸入事務(wù)、輸出事務(wù)、設(shè)置(Setup)事務(wù),幀開(kāi)始(SOF),幀結(jié)束(EOF)等類(lèi)型,下面以輸入事務(wù)處理為例加以介紹。

如圖2顯示了輸入事務(wù)處理中無(wú)差錯(cuò)事務(wù)情況,首先由主機(jī)向總線發(fā)出輸入令牌包通知某個(gè)設(shè)備向主機(jī)發(fā)送數(shù)據(jù);當(dāng)所指定的設(shè)備接收到此令牌包并檢驗(yàn)身份后,將準(zhǔn)備好的數(shù)據(jù)組裝成數(shù)據(jù)包向主機(jī)傳送出去;接著當(dāng)主機(jī)接收到的數(shù)據(jù)經(jīng)校驗(yàn)無(wú)差錯(cuò)后,創(chuàng)建一個(gè)ACK的握手包返回給設(shè)備通知主機(jī)已正確接收到數(shù)據(jù),然后進(jìn)行新的事務(wù)處理過(guò)程。若主機(jī)接收數(shù)據(jù)包錯(cuò)誤,則不發(fā)送ACK握手包,表示處理過(guò)程沒(méi)有成功;若設(shè)備未準(zhǔn)備好數(shù)據(jù),設(shè)備會(huì)向主機(jī)發(fā)送NAK握手包,提醒主機(jī)暫時(shí)不能發(fā)送數(shù)據(jù);若設(shè)備出錯(cuò),則返回主機(jī)STALL握手包通知設(shè)備出錯(cuò)。

1.3 總線傳輸

為了滿(mǎn)足不同外設(shè)和用戶(hù)的要求,USB提供了4種傳輸方式:控制傳輸、實(shí)時(shí)傳輸、中斷傳輸、批量傳輸。它們?cè)跀?shù)據(jù)格式傳輸方向數(shù)據(jù)包容量限制和總線訪問(wèn)限制等方面有著各自不同的特征。

控制傳輸用來(lái)對(duì)設(shè)備進(jìn)行初始化和配置管理,所有USB設(shè)備必須直接控制傳輸,是總線傳輸中最復(fù)雜的傳輸方式;實(shí)時(shí)傳輸用來(lái)傳送音頻或視頻的數(shù)據(jù);中斷傳輸用來(lái)傳輸類(lèi)似PCI或ISA總線上中斷信號(hào)的數(shù)據(jù);批量傳輸用于打印機(jī)或掃描儀等傳輸大塊數(shù)據(jù)的設(shè)備。

控制傳輸一般包括2或3個(gè)事務(wù)處理階段,即設(shè)置階段,數(shù)據(jù)階段(可選)和狀態(tài)階段。圖3給出了設(shè)置階段的細(xì)節(jié)。如果數(shù)據(jù)沒(méi)有正確接收設(shè)備就會(huì)忽略它,而且不返回應(yīng)答包。

2 USB IP模塊設(shè)計(jì)和代碼編寫(xiě)

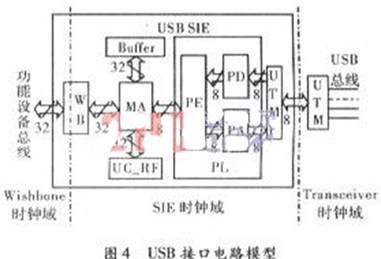

USB接口主要有UTM(USB Transceiver Macrocell)、SIE(SefiM Interface Engine)和設(shè)備功能總線組成。電路結(jié)構(gòu),如圖4所示,時(shí)鐘域分為:Transceiver時(shí)鐘域,SIE時(shí)鐘域和Wish- bone總線時(shí)鐘域。

2.1 UTM模塊

USB總線數(shù)據(jù)線由DP和DN組成,是I/O端口。并行通過(guò)對(duì)DP和DN的上拉、下拉來(lái)區(qū)別低速USB設(shè)備和高速USB設(shè)備。

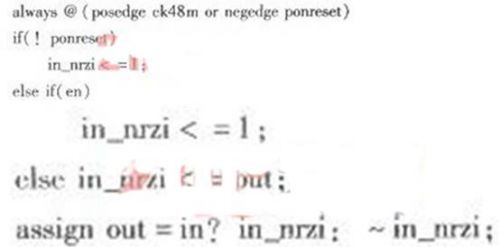

USB總線上的數(shù)據(jù)首先通過(guò)UTM,進(jìn)行NRZI解碼和位剝離后,串并轉(zhuǎn)換為8位并行數(shù)據(jù),傳送給SIE中的UTMI或從UTMI接收8位并行數(shù)據(jù),經(jīng)過(guò)NRZI編碼和位填充后,發(fā)送到USB總線。由于USB系統(tǒng)采用NRZI編碼,對(duì)于一串0來(lái)說(shuō),它的數(shù)據(jù)線的電平狀態(tài)會(huì)按位跳變,對(duì)以一串l則不然,電平會(huì)長(zhǎng)時(shí)間不變,可能導(dǎo)致數(shù)據(jù)接受方的時(shí)間同步漂移,為了避免漂移,每遇到6個(gè)1就在NRZI編碼之前加0,即位填充。

NRZI的vefilog實(shí)現(xiàn)代碼為:

2.2 串行接口引擎

串行接口引擎(Serial Interface Engine,SIE)主要由PL(Protocol Layer),MA(memory buffer arbiter),UTMI(UTM Interface)等組成。PD,PA,PE3個(gè)模塊組成了USB SIE的協(xié)議層(PL)。

UTMI(UTM Interface)是UTM和SIE的接口主要功能是檢測(cè)總線狀態(tài)以及識(shí)別總線速度。負(fù)責(zé)PL與UTM的數(shù)據(jù)交換。

PD將UTMI接收到的信息數(shù)據(jù)包進(jìn)行解析,解析出包標(biāo)識(shí)(PID)、端點(diǎn)地址和設(shè)備地址以及包含在包中的有效數(shù)據(jù)命令。在解碼時(shí),對(duì)PID進(jìn)行校驗(yàn),即PID[7:4]~PID[3:0],還要對(duì)必要的令牌包進(jìn)行CRC5校驗(yàn),對(duì)數(shù)據(jù)包進(jìn)行CRCl6校驗(yàn)。CRCl6,CRC5多項(xiàng)式為:x16+x15+x2+1和x5+x2+1。

設(shè)計(jì)中把命令解碼電路也設(shè)計(jì)在PD上,解碼電路的設(shè)計(jì)思路是:通過(guò)一個(gè)計(jì)數(shù)器將8 bit的命令數(shù)據(jù)分別存放在8個(gè):Register中,然后對(duì)Register進(jìn)行解碼,來(lái)判斷該條命令帶表的含義和執(zhí)行的操作。例如:Get Descriptor命令,主機(jī)發(fā)送的命令數(shù)據(jù)為8’ha0,8’h06,8’h00,8’h01,8’h00,8’h00,8’h4O,8’h00,然后解碼電路根據(jù)這8 bit來(lái)判斷命令的含義。如果主機(jī)發(fā)送命令有誤,或該設(shè)備不支持命令,則這條命令被忽略或返回NAK握手包。

PA根據(jù)PE(Protocol Engine)送來(lái)的PID組織相應(yīng)的信息包,把要發(fā)送的數(shù)據(jù)安排在相應(yīng)的數(shù)據(jù)包,或者令牌包。發(fā)送令牌包時(shí),不必產(chǎn)生CRC5校驗(yàn)位。在發(fā)送數(shù)據(jù)包寸,需要把有效數(shù)據(jù)的CRCl6校驗(yàn)位放在包末尾一起發(fā)送。

PE可以對(duì)IN,OUT以及Setup事務(wù)進(jìn)行單線程處理,且確定當(dāng)前傳輸事務(wù)要操作的端點(diǎn)地址,所有對(duì)MA和RF的當(dāng)前操作都基于這個(gè)端點(diǎn)地址。PE要根據(jù)當(dāng)前端點(diǎn)的配置或當(dāng)前狀態(tài)處理傳輸事務(wù),并在傳輸事務(wù)中實(shí)時(shí)更新控制/狀態(tài)寄存器CSR。SIE還能通過(guò)CSR中的中斷向量請(qǐng)求設(shè)備總線的控制支持。

3 系統(tǒng)仿真與實(shí)現(xiàn)

設(shè)計(jì)中包含了UTM,SIE,并根據(jù)協(xié)議寫(xiě)出了含有設(shè)備描述符的ROM。這樣IP具有USB接口的功能,可以作為一個(gè)USB設(shè)備與主機(jī)進(jìn)行通信。根據(jù)USB協(xié)議,模擬主機(jī)動(dòng)作編寫(xiě)Testbench,它主要由模擬主機(jī)數(shù)據(jù)包(Send Data),Stuffing檢測(cè),CRC校驗(yàn)檢錯(cuò)等來(lái)仿真。仿真波形,如圖5所示。

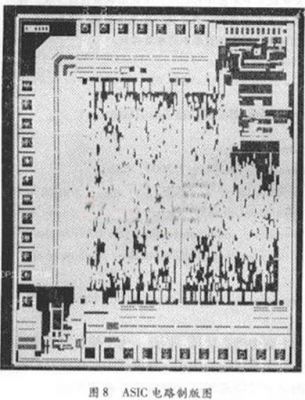

最后將電路用ASIC實(shí)現(xiàn)。采用0.35μm CMOS工藝實(shí)現(xiàn)后端設(shè)計(jì),數(shù)字電路采用單元庫(kù)自動(dòng)布線,模擬電路手工繪制版圖,并進(jìn)行DRC和LVS檢查,最終版圖預(yù)覽圖,如圖8所示,芯片面積為1.2 ms2;經(jīng)過(guò)后仿真得出:工作頻率為120 MHz,工作電流9 mA,靜態(tài)電流40μA。工作頻率可以實(shí)現(xiàn)高速USB協(xié)議的要求,功耗、電流等參數(shù)也符合設(shè)計(jì)要求。

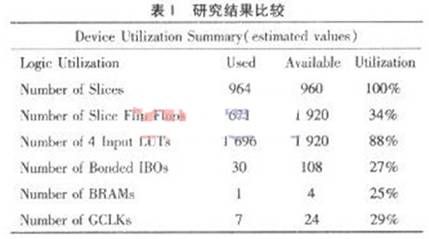

本設(shè)計(jì)與國(guó)內(nèi)其他的研究結(jié)果進(jìn)行比餃,如表1所示。

從表1中對(duì)表可以看出,本設(shè)計(jì)在滿(mǎn)足頻率(FX8>480 MHz)的條件下,精簡(jiǎn)了多個(gè)單元,節(jié)省了資源,完全符合USB協(xié)議的要求。將IP下載到FPGA中與主機(jī)通信,主機(jī)能正確讀出設(shè)備描述符和正確完成其他操作,并在主機(jī)端顯示USB2.0 Device。進(jìn)一步證明了設(shè)計(jì)的正確性和實(shí)用性。

4 結(jié)束語(yǔ)

文中介紹了基于USB協(xié)議層模塊的設(shè)計(jì),最后在Modelsim6.0下仿真和ISE9.1進(jìn)行了綜合,采用Xilinx Spartan3E的XC3S1OOE進(jìn)行FPGA驗(yàn)證,并利用0.35μm CMOS工藝進(jìn)行系統(tǒng)的后端設(shè)計(jì)。實(shí)現(xiàn)了工作頻率120 MHz,功耗30 mW。

結(jié)果表明,設(shè)計(jì)的USB協(xié)議層模塊各功能達(dá)到了預(yù)期目標(biāo)、整體性能良好。此IP core可以廣泛應(yīng)用于各種USB設(shè)備接口、通信轉(zhuǎn)接器件,也可以集成在SOC中,作為系統(tǒng)芯片總線接口。文中設(shè)計(jì)的USB IP已成功地應(yīng)用于兩款USB設(shè)備端的接口控制芯片(USB轉(zhuǎn)PS/2接口IC和USB集線器IC),在實(shí)際應(yīng)用中性能可靠、速度穩(wěn)定,而且價(jià)格低廉。

發(fā)布者:小宇