引 言

ARM公司于2008年11月12日發(fā)布了ARM Cortex微控制器軟件接口標(biāo)準(zhǔn)(CMSIS:Cortex Microcon-troller Software InteRFace Standard)。CMSIS是獨立于供應(yīng)商的Cortex-M處理器系列硬件抽象層,為芯片廠商和中間件供應(yīng)商提供了連續(xù)的、簡單的處理器軟件接口,簡化了軟件復(fù)用,降低了Cortex-M3上操作系統(tǒng)的移植難度,并縮短了新入門的微控制器開發(fā)者的學(xué)習(xí)時間和新產(chǎn)品的上市時間。

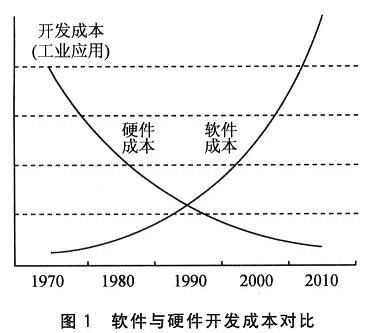

根據(jù)近期的調(diào)查研究,軟件開發(fā)已經(jīng)被嵌入式行業(yè)公認(rèn)為最主要的開發(fā)成本。圖1為近年來軟件開發(fā)與硬件開發(fā)成本對比圖。因此,ARM與Atmel、IAR、Keil、hami-nary Micro、Micrium、NXP、SEGGER和ST等諸多芯片和軟件廠商合作,將所有Cortex芯片廠商產(chǎn)品的軟件接口標(biāo)準(zhǔn)化,制定了CMSIS標(biāo)準(zhǔn)。此舉意在降低軟件開發(fā)成本,尤其針對新設(shè)備項目開發(fā),或者將已有軟件移植到其他芯片廠商提供的基于Cortex處理器的微控制器的情況。有了該標(biāo)準(zhǔn),芯片廠商就能夠?qū)⑺麄兊馁Y源專注于產(chǎn)品外設(shè)特性的差異化,并且消除對微控制器進(jìn)行編程時需要維持的不同的、互相不兼容的標(biāo)準(zhǔn)的需求,從而達(dá)到降低開發(fā)成本的目的。

1 基于CMSIS標(biāo)準(zhǔn)的軟件架構(gòu)

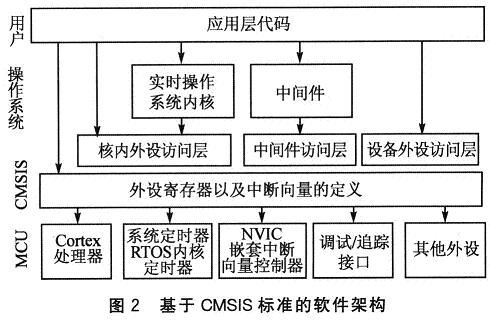

如圖2所示,基于CMSIS標(biāo)準(zhǔn)的軟件架構(gòu)主要分為以下4層:用戶應(yīng)用層、操作系統(tǒng)及中間件接口層、CMSIS層、硬件寄存器層。其中CMSIS層起著承上啟下的作用:一方面該層對硬件寄存器層進(jìn)行統(tǒng)一實現(xiàn),屏蔽了不同廠商對Cortex-M系列微處理器核內(nèi)外設(shè)寄存器的不同定義;另一方面又向上層的操作系統(tǒng)及中間件接口層和應(yīng)用層提供接口,簡化了應(yīng)用程序開發(fā)難度,使開發(fā)人員能夠在完全透明的情況下進(jìn)行應(yīng)用程序開發(fā)。也正是如此,CMSIS層的實現(xiàn)相對復(fù)雜。

CMSIS層主要分為3部分。

①核內(nèi)外設(shè)訪問層(CPAL):由ARM負(fù)責(zé)實現(xiàn)。包括對寄存器地址的定義,對核寄存器、NVIC、調(diào)試子系統(tǒng)的訪問接口定義以及對特殊用途寄存器的訪問接口(如CONTROL和xPSR)定義。由于對特殊寄存器的訪問以內(nèi)聯(lián)方式定義,所以ARM針對不同的編譯器統(tǒng)一用_INLINE來屏蔽差異。該層定義的接口函數(shù)均是可重入的。

②中間件訪問層(MWAL):由ARM負(fù)責(zé)實現(xiàn),但芯片廠商需要針對所生產(chǎn)的設(shè)備特性對該層進(jìn)行更新。該層主要負(fù)責(zé)定義一些中間件訪問的API函數(shù),例如為TCP/IP協(xié)議棧、SD/MMC、USB協(xié)議以及實時操作系統(tǒng)的訪問與調(diào)試提供標(biāo)準(zhǔn)軟件接口。該層在1.1標(biāo)準(zhǔn)中尚未實現(xiàn)。

③設(shè)備外設(shè)訪問層(DPAL):由芯片廠商負(fù)責(zé)實現(xiàn)。該層的實現(xiàn)與CPAL類似,負(fù)責(zé)對硬件寄存器地址以及外設(shè)訪問接口進(jìn)行定義。該層可調(diào)用CPAL層提供的接口函數(shù),同時根據(jù)設(shè)備特性對異常向量表進(jìn)行擴展,以處理相應(yīng)外設(shè)的中斷請求。

2 CMSIS規(guī)范

(1)文件結(jié)構(gòu)

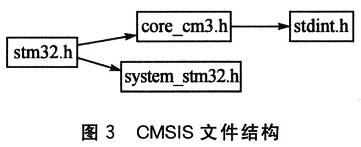

CMSIS的文件結(jié)構(gòu)如圖3所示(以STM32為例)。其中stdint.h包括對8位、16位、32位等類型指示符的定義,主要用來屏蔽不同編譯器之前的差異。core_cm3.h和core_cm3.C中包括Cortex_M3核的全局變量聲明和定義,并定義一些靜態(tài)功能函數(shù)。system_

(2)工具鏈

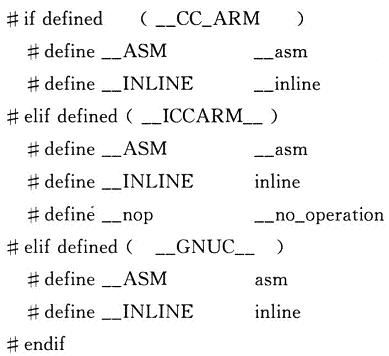

CMSIS支持目前嵌入式開發(fā)的三大主流工具鏈,即ARM ReakView(armcc)、IAR EWARM(iccarm)以及GNU工具鏈(gcc)。通過在core_cm3.C中的如下定義,來屏蔽一些編譯器內(nèi)置關(guān)鍵字的差異。

這樣,CPAL中的功能函數(shù)就可以被定義成靜態(tài)內(nèi)聯(lián)類型(static_INLINE),實現(xiàn)編譯優(yōu)化。

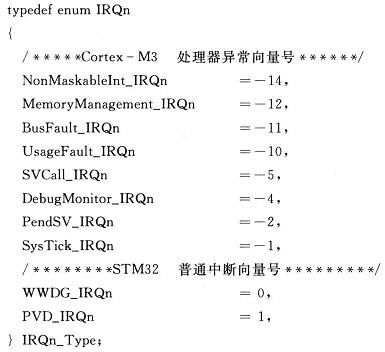

(3)中斷異常

CMSIS對異常和中斷標(biāo)識符、中斷處理函數(shù)名以及中斷向量異常號都有嚴(yán)格的要求。異常和中斷標(biāo)識符需加后綴_IRQn,系統(tǒng)異常向量號必須為負(fù)值,而設(shè)備的中斷向量號是從0開始遞增,具體的定義如下所示(以STM32為例):

CMSIS對系統(tǒng)異常處理函數(shù)以及普通的中斷處理函數(shù)名的定義也有所不同。系統(tǒng)異常處理函數(shù)名需加后綴_Handler,而普通中斷處理函數(shù)名則加后綴_IRQHandler。這些異常中斷處理函數(shù)被定義為weak屬性,以便在其他的文件中重新實現(xiàn)時不出現(xiàn)重復(fù)定義的錯誤。這些處理函數(shù)的地址用來填充中斷異常向量表,并在啟動代碼中給以聲明,例如:NMI_Handler、MemManage_Handler、SysTick_Handler、WWDG_IRQHandler等。