引 言

FPGA" target="_blank">FPGA廣泛應用在電子通信領域,其安全性引起了注意,本文針對安全配置提出了解決方案。

現場可編程門陣列FPGA(Field Programmablc Gate Array)是基于門陣列方式為用戶提供可編程資源的,其內部邏輯結構的形成是由配置數據決定的。采用在線可重配置方式ICR(In-Circuit Reconfigurability)將這些配置數據配置到FPGA內部SRAM中,但由于SRAM的易失性,每次上電時,都必須對FPGA重新進行配置,從而實現用戶編程所要實現的功能。

以前的設計大多是將配置數據存放在FPGA組成的系統(tǒng)上,本文提出將配置數據存放在使用者自己攜帶的外部存儲器(如可加密的U盤)中。使用前將U盤接入FPGA組成的系統(tǒng),系統(tǒng)上電時由單片機控制讀出配置數據,再傳送給FPGA進行配置。這樣做優(yōu)點很多:修改、升級簡便,現場保密性強,安全性高;可多人分時使用同一硬件系統(tǒng),同一硬件系統(tǒng)插入不同的配置U盤就可以實現不同的功能,可以方便地存儲大容量配置數據或多個配置數據文件等;同時,符合計算機和嵌入式系統(tǒng)的熱點USB OTG(On The Go,移動USB)技術趨勢,是具有創(chuàng)新的設計。

1 FPGA的配置方式和配置數據文件

1.1 FPGA的配置方式

以Altera公司的FPGA器件為例,有2類配置下載方式:主動配置和被動配置。主動配置方式是由FPGA器件主動引導配置操作,從外圍專用配置芯片(如EPC4)中獲得配置數據的過程;被動配置方式則是由外部計算機或控制器控制配置過程。

以Mercury、APEX 20K(2.5V)、ACEX 1K和FLEX10K系列FPGA為例,配置方式有:被動串行PS(PasiveSerial)、被動并行同步PPS(Passive Parallel Synchronous)、被動并行異步PPA(Passive Parallel Asyn-chronous)和JTAG(Jont Test Action Group)等。具體配置方式由方式選擇引腳MSEL1和MSELO的邏輯電平組合決定。

基于SRAM LUT(查找表)結構的FPGA采用在線可重配置方式ICR。以配置方式PS為例,可通過下載電纜南計算機直接對FPGA器件進行配置。這種方法在設計調試時非常方便,但在現場應用巾是很不現實的。上電后自動加載對FPGA器件進行配置是實際必須的,有許多方法,例如專用配置芯片(如EPC4)配置、單片機控制配置、MAX3000A控制F1ash存儲器配置、PCI總線配置、Internet配置、PSD(Programmable System Devices可編程器件)配置等。

1.2 FPGA的配置數據文件

Altera公司的Quartus II開發(fā)工具可以生成多種配置或編譯文件,用于不同配置方式。對于不同的目標器件,編譯后開發(fā)工具會根據指定的FPGA器件自動生成“.sof(SRAM Object File)”和“.pof(Programmer ObjectFile)”配置文件。“.sof”配置文件是由下載電纜將其下載到FPGA中的;“.pof”配置文件是存放在配置器件里的。用單片機配置時,要將“.sof”文件轉換成“.rbf(Raw BinaryFile)”文件,可打開QuartusII的File菜單,單擊ConvertProgramming Fiks進行轉換。配置文件的大小隨FPGA器件的不同而不同,例如EPFlOKlO的配置文件“.sof”和“.rbf”的大小為15KB。

2 單片機配置FPGA設計

2.1 單片機配置FPGA的優(yōu)點

在實際應用中,單片機控制配置FPGA,對于保密和升級,以及實現多任務電路結構重配置和降低配置成本,都是很好的選擇。配置方式PS、PPS和PPA均可以用單片機控制配置。

由單片機和外部存儲器組成配置FPGA電路,將配置數據寫入外部存儲器,系統(tǒng)上電時再由單片機控制對FPGA進行配置。也可將多個配置文件分區(qū)存儲到外部存儲器中,然后由單片機接收不同的命令,選擇讀取不同存儲區(qū)的數據配置到FPGA器件,從而實現多任務電路結構重配置,在線配置成多種不同的電路功能;代替了價格昂貴的不可擦寫和可擦寫配置芯片,降低了成本。

2.2 配置數據存儲在U盤

在銀行等保密行業(yè),如果要求安全和保密程度非常高,那么一定要有權限的使用者才能使用,或由不同的用戶分時使用同一臺FPGA組成的系統(tǒng)。最好是不要將配置數據存放在FPGA組成的系統(tǒng)上,而是將配置數據存放在使用者自己攜帶的外部存儲器(如U盤)中(對U盤的讀/寫還可以加密);使用前將存放配置數據的外部存儲器接入FPGA組成的系統(tǒng),系統(tǒng)上電時冉由單片機控制對FPGA進行配置就可以了。

1994年11月,以Intel為首的7家公司推出了通用串行總線USB(Universal serial Bus)協議規(guī)范的第一個草案。USB協議從1.1過渡到2.0,作為其最重要指標的設備傳輸速度也從USBl.1標準的低速1.5 Mbps和全速12Mbps提高到USB2.0標準的高速480Mbps。目前,USB設備已經非常普遍,USB接口以其速度快、功耗低、支持即插即用、使用安裝方便和價格低廉等優(yōu)點得到了廣泛應用。USB OTG已經成為嵌入式系統(tǒng)領域中的熱點,使得USB能應用在沒有PC的領域中,實現移動數據交換和存儲。本文提出將配置數據存儲在U盤中,通過單片機控制讀/寫,符合USB OTG發(fā)展趨勢,將在嵌入式和FPGA領域得到廣泛應用。

|

2.3 單片機讀取存儲在u盤中的配置數據

通常USB設備終端必須與計算機連接。如果沒有PC,則需要通過USB總線的通用接口芯片(當然也可以利用帶USB接口的單片機)控制U盤的讀/寫。本設計采用單片機AT89S52控制USB總線的通用接口芯片CH375來讀取存儲在U盤的配置數據。

CH375是一個USB總線的通用接口芯片,內部集成了PLL倍頻器、主從USB接口SIE、數據緩沖區(qū)、被動并行接口、異步串行接口、命令解釋器、控制傳輸的協議處理器和通用的固件程序等;支持USB-HOST主機方式和USB-DEVICE/SLAVE沒備方式,可以方便地掛接到單片機/DSP/MCU/MPU等控制器的系統(tǒng)總線上。外部單片機可以直接以扇區(qū)為基本單位讀/寫常用的USB存儲設備(包括USB硬盤、USB閃存盤和U盤)。

硬件設計:CH375工作于并口方式,與普通的MCS-5l單片機的連接如圖1所示。CH375的TXD引腳通過l kΩ左右的下拉電阻接地或者直接接地,從而使CH375工作于并口方式。

軟件設計:①進入USB主機模式,要讀/寫U盤,必須先設置CH375使其工作于USB主機方式。②將U盤當作存儲器進行讀/寫,方法與讀/寫閃存差不多,操作簡單且速度快。單片機讀/寫U盤文件程序分層如圖2所示。

|

2.4 用單片機配置FPGA的過程

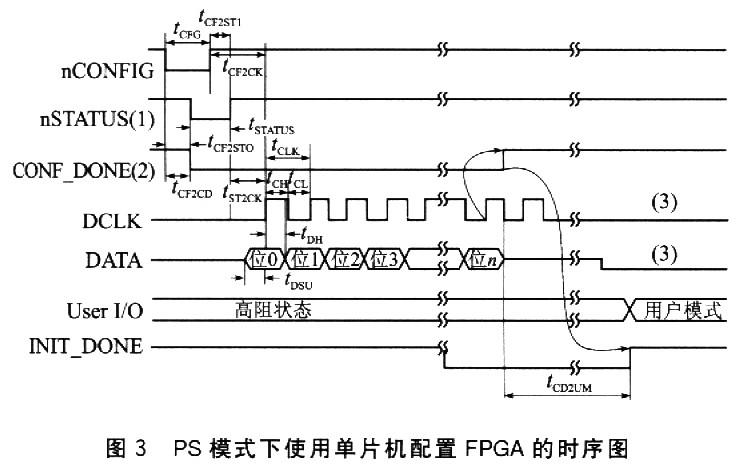

FPGA器件上電以后,開始配置過程的復位、配置和初始化3個階段,然后進入用戶狀態(tài)。以配置FLEX10K10為例,圖3為PS模式下使用單片機配置FPGA的時序圖。

|

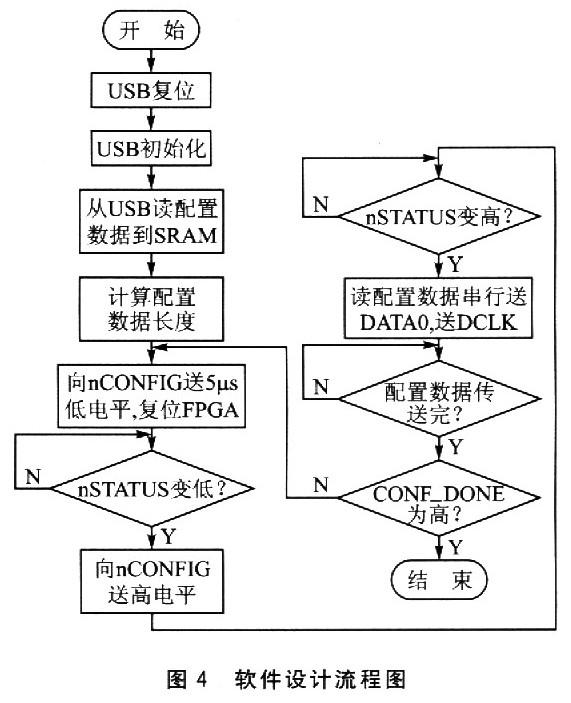

配置過程如下:①MCU的P1.7引腳產生一個tCFG≥μs的低電平給FPGA的nCONFIG引腳使FPGA復位,200 ns后nSTATUS和CONF_DONE同時跟隨變?yōu)榈碗娖剑籉PGA的I/O端口為高阻狀態(tài),RAM被清除。②MCU的P1.7引腳產生上跳變時開始配置,FPGA退出復位狀態(tài),4μs后nSTATUS被釋放并被上拉電阻拉高,FPGA準備接收數據進入配置階段。設置MCU的串口工作方式為O,單片機檢測到nSTATUS由低跳到高后,讀取配置數據(從U盤讀取或上電時先將配置數據從U盤讀到SRAM62255)由RXD送到FPGA的DATA0(注意低位LSB先送出);MCU的TXD接收FPGA的DCLK以提供時鐘信號,配置數據足在DCLK上升沿被移位入FPGA的,全部配置數據移入FPGA直到CONF_DONE變?yōu)楦唠娖剑渲秒A段結束。若CONF_DONE沒有變?yōu)楦唠娖剑瑒t需要重新配置。③初始化階段,持續(xù)O.6~2μs。不同的FPGA器件,持續(xù)時間不等。A1tera公司的Quartus II開發(fā)工具生成配置文件時,對于不同的目標器件和配置方式已經添加了相應的空DCLK。軟件設計使微處理器提供配置所需的時序和串行傳送配置數據,以及對配置進行監(jiān)測,從而實現配置過程。軟件設計流程如圖4所示。

|

3 結論

FPGA器件的配置技術猶如集成電路制造中的流片,是非常重要的一個環(huán)節(jié)。用單片機配置FPGA器件與用專用器件相比,具有成本低、保密性好、可升級、可實現多任務電路結構重構(符合軟件無線電思想)等特點,本設計具有創(chuàng)新性,硬件設計簡單可靠,且成本低,易于實現,是確保FPGA安全性和保密性的一種方法,在金融等關系到國家利益的場合具有重大實用價值。