RF Engines公司的ChannelCore64使設(shè)計者能夠用一個可對FPGA編程的IP核來替代多達16個DDC(直接下變頻器)ASIC,可顯著減少PCB面積,降低功耗而且增加靈活性。和原來的方法相比,新方法是降低成本的典型代表,隨著通道數(shù)目的增加,降低成本的需求愈加突出。在提供靈活性和簡化設(shè)計的同時,這種方法也能降低功耗。ChannelCore64的應(yīng)用包括無線基站,衛(wèi)星地面站和其它多通道無線電接收器等。在這些系統(tǒng)應(yīng)用中,需要從一個頻帶非常寬的信號中提取很多具有不同帶寬的通道(或者信號),然后將整個系統(tǒng)的其它部分與之匹配來簡化設(shè)計。

ChannelCore64

幾乎所有的無線接收器都要通過下變頻,從一個非常寬的輸入頻譜中提取一個或者多個相對窄的通道。在系統(tǒng)的前端,隨著靈活性的增加,迫切要求不同的無線接入技術(shù)協(xié)同合作,

允許對波段進行動態(tài)的可重新配置,以及對接收系統(tǒng)設(shè)計的投資進行前景估計。此外,用戶對帶寬需求的不斷增加,加上諸如MIMO(多輸入/多輸出)等新技術(shù)的出現(xiàn),要求系統(tǒng)必須具有支持和處理越來越多的信號通道的能力。到目前為止,一般都是利用DDC ASIC,通常能處理達4個通道,因此,一個復(fù)雜的多通道應(yīng)用就需要多個大且昂貴的系統(tǒng)板。RF Engines公司提出了一個新穎的通道選擇架構(gòu), 能夠在單個FPGA器件上處理多達64個通道。 這能大幅降低成本、面積和功耗,因為一個器件能夠替代原先16個ASIC,尤其在信道數(shù)量增加時較傳統(tǒng)方式更能降低成本。

ChannelCore64利用了一種獨特的下變頻方法,和其它基于FPGA的DDC解決方案相比,此方法能夠獲得很大的硅面積節(jié)省,同時還能提供各種先前基于ASIC的DDC芯片具有的配置控制選項。例如,此IP核能夠很好地工作在Xilinx Virtex II Pro 30 FPGA器件上,在所有通道都有效的工作環(huán)境下,最大功耗只有4W。如果用Altera器件實現(xiàn),性能大體相當(dāng)。

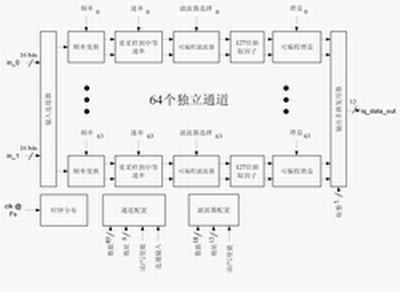

圖1 ChannelCore64內(nèi)部構(gòu)成

此IP核(見圖1)能夠使用戶從一個或者兩個輸入源獨立地選擇各個通道,調(diào)節(jié)每個通道的中心頻率和增益,且選擇不同的濾波形狀和帶寬采樣速率以適應(yīng)變化信號的工作環(huán)境。一個集成的高質(zhì)量信號重采樣器能夠保證終端到終端的動態(tài)范圍至少在80dB以上,即使對于分數(shù)重采樣比例也能達到此動態(tài)范圍。這要比其它分數(shù)重采樣解決方案高很多。

ChannelCore64提供了8個獨立的用戶可編程濾波器,用戶能夠根據(jù)系統(tǒng)所需要的性能要求進行匹配。濾波器設(shè)計包括等紋波,根余弦和高斯濾波器等。 這些濾波器能夠工作在高采樣速率下,作為重采樣處理過程的一部分。能夠?qū)σ粋€4倍的過采樣輸出提供相當(dāng)于一個80抽頭的濾波器。為了使濾波器能夠提供多個可能的輸出帶寬,選擇濾波器時應(yīng)充分考慮輸出采樣速率。

重采樣器能夠?qū)γ總€通道提供輸出速率控制,用于匹配調(diào)制系統(tǒng)速率。采樣速率的分辨率小于0.01Hz。對于每個通道,飽和度指示和微調(diào)增益控制的分辨率為0.01dB,各個通道完全獨立,內(nèi)核執(zhí)行過程中在不影響其它信道工作的條件下可進行信道重構(gòu)。

ChannelCore64的主要特色包括:支持兩個16位ADC輸入(每個采樣率達140MSPS);64個獨立的可連接各自ADC的下變頻信道;獨立的信道中心頻率調(diào)諧能力,分辨率高于0.01Hz;獨立的信道頻寬選擇功能;獨立的采樣率輸出選擇功能,分辨率高于0.01Hz。

該內(nèi)核針對無線基站、衛(wèi)星地面站及其它多信道無線接收機等應(yīng)用。在這些應(yīng)用中,MIMO技術(shù)可被很好地應(yīng)用,例如用額外的天線來獲得更多的信號信息,通過去除多通路效應(yīng),對大量輸入信息的處理可獲得較好的接收質(zhì)量,因此大大提高了服務(wù)質(zhì)量。通常,天線數(shù)目越多,也就意味著需要更多的ASIC,同時也就意味著成本和功耗的增加。然而,利用基于ChannelCore64的解決方案,額外的通道能夠很容易地配置,例如,從24通道到64通道,服務(wù)質(zhì)量大大提高了,但是成本的增加幾乎可以忽略。

ChannelCore64 可以EDIF網(wǎng)表的形式交付, 同時可以加上用戶約束文件、例化模版、VHDL模型、測試文件和Matlab模型。Bit-true Matlab模型可以免費提供,允許設(shè)計者在系統(tǒng)環(huán)境下,精確地仿真ChannelCore64核。該核可提供簡單的授權(quán)模型以及用戶變量,包括上變頻器,均可根據(jù)需要定制。ChannelCore64已經(jīng)完成測試,證明其能提供快速的、低風(fēng)險的、經(jīng)過優(yōu)化的解決方案。

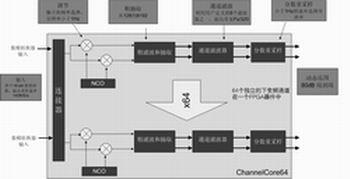

圖2 ChannelCore64可在一個FPGA中實現(xiàn)64個獨立的下變頻通道

實現(xiàn)64個獨立的下變頻通道

這個64位的核能夠和目前流行的A/D轉(zhuǎn)換技術(shù)匹配, 能夠提供通用功能來滿足盡可能廣的要求(見圖2)。RF Engines公司正在對定制FPGA的開發(fā)進行專門研究,并且很快就能根據(jù)客戶的需要提供相關(guān)的替代產(chǎn)品。對于一個給定的核的設(shè)計,其最主要的可變設(shè)計參數(shù)包括: 數(shù)據(jù)和可編程界面, 頻率和數(shù)據(jù)率精度, 濾波器參數(shù)和無雜散動態(tài)范圍。