SOC" title="PSOC">PSOC微處理器擁有多系列、多規(guī)格的應(yīng)用芯片,以滿足不同用戶的不同層次的需要,如CY8C26XXX/CY8C24XXX/CY8C22XXX等等。它的出現(xiàn)使設(shè)計者逐步擺脫了板級電子系統(tǒng)設(shè)計方法層次而進入芯片級電子系統(tǒng)設(shè)計,減少了單片機的品種和規(guī)格,同時更有利于新品開發(fā)和升級換代。與同種價位的普通單片機比較,其豐富的內(nèi)部資源、新穎的設(shè)計界面、靈活的設(shè)計方式、簡單的編程技巧都使其極具特點。文中以CY8C24223為例,介紹一種典型應(yīng)用——基于PSoC可編程片上系統(tǒng)的感煙火災(zāi)探測器。它將對煙霧變化信號的放大、處理、模數(shù)轉(zhuǎn)換功能集成到微處理器的內(nèi)部完成,減少了芯片的外圍器件,提高了系統(tǒng)整體的集成性能。

1 內(nèi)部資源及開發(fā)環(huán)境

1.1 內(nèi)部資源介紹

PSoC內(nèi)部有一個高速M8C內(nèi)核、快閃內(nèi)存和SRAM數(shù)據(jù)內(nèi)存

,以及可進行多種配置的模擬模塊陣列和數(shù)字模塊陣列;內(nèi)核采用Haryard結(jié)構(gòu),具有獨立的程序存儲器和數(shù)據(jù)存儲器總線,處理器工作頻率可達到24 MHz。對于不同系列、不同型號的片上系統(tǒng),其內(nèi)部資源配置不同。以CY8C24223芯片為例,內(nèi)部具有4 KB的Flash以及256 B的片內(nèi)SRAM數(shù)據(jù)存儲器;4個數(shù)字模塊、6個模擬模塊;16個通用I/0口,最大輸出電流可達25 mA,每個I/O口引腳均可通過編程設(shè)置,所有I/O口引腳都能作為中斷源;具有存儲字節(jié)可變的EEPROM模塊和ISSP串行編程功能。

1.2 集成開發(fā)環(huán)境lDE

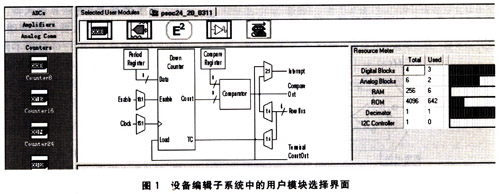

用于PSoC的集成開發(fā)環(huán)境PSoC Designer是一種功能齊全、基于Gul的設(shè)計工具套件。它分為設(shè)備編輯子系統(tǒng)、應(yīng)用編輯子系統(tǒng)和調(diào)試程序子系統(tǒng)。其界面將根據(jù)不同的子系統(tǒng)而被分割成多個活動窗口。其中最具特色的是設(shè)備編輯子系統(tǒng),具有相當(dāng)?shù)撵`活性和可操作性,如圖l所示。

用戶可通過選擇和放置用戶模塊、配置參數(shù)、連接模塊、定義引腳功能、生成應(yīng)用文件API來最終完成設(shè)備編輯工作。在產(chǎn)品的開發(fā)研制過程中,無論是更改設(shè)計原理還是更改設(shè)計參數(shù),都無需在PCB板上進行,而只需借助簡單的鼠標(biāo)點擊選項就可對硅片進行重新配置,快速、簡單地完成產(chǎn)品的功能塊選用以及功能塊之間的連線。

2 PSoC片上系統(tǒng)的開發(fā)關(guān)鍵

2.1 混合信號陣列的系統(tǒng)級集成

用戶的模擬模塊陣列和數(shù)字模塊陣列的可配置性是這一可編程片上系統(tǒng)的最大特點,它不同于FPGA或CPLD嵌入式片上系統(tǒng)。FPGA與CPLD是對邏輯門陣列進行現(xiàn)場編輯,而PSoC‘微處理器不僅能對數(shù)字模塊進行動態(tài)配置,同時也能對模擬模塊進行動態(tài)配置,實現(xiàn)混合信號陣列的系統(tǒng)級集成。

在應(yīng)用時,片上系統(tǒng)中的數(shù)字模塊陣列可配置成多種功能,如定時/計數(shù)器、UART、SPI、CRC發(fā)生器、PWM等等;模擬模塊陣列可配置成具有不同工作方式的ADC、可編程增益放大器PGA、比較器、可編程濾波器、DAC等等。通過用數(shù)字模塊配置的定時器作為ADC的采樣頻率等等類似方法,實現(xiàn)數(shù)字模塊陣列和模擬模塊陣列的集成應(yīng)用,使PSoC微處理器具有強大的混合信號陣列的系統(tǒng)級集成功能。

PSoC微處理器的模塊功能中,最簡單的混合信號集成功能的應(yīng)用是A/D轉(zhuǎn)換器。PSoC微處理器支持多種A/D轉(zhuǎn)換器,如14位遞增式、11位△-∑ADC、8位逐次逼近式ADC和6位SAR-ADC。用戶可根據(jù)A/D轉(zhuǎn)換精度和轉(zhuǎn)換時間的設(shè)計要求,設(shè)置不同工作方式的A/D模塊。以配置一個8位△-A/D轉(zhuǎn)換器為例,轉(zhuǎn)換器需占用微處理器的內(nèi)部資源為:1個數(shù)字模塊、1個開關(guān)電容模擬SC模塊、1個外部模擬輸入引腳,以及生成8位△-ΣA/D轉(zhuǎn)換器應(yīng)用程序API所需的8字節(jié)的內(nèi)部RAM和143字節(jié)的Flash。

圖2是一個8位△-∑A/D轉(zhuǎn)換器的結(jié)構(gòu)框圖。它由模擬開關(guān)電容SC模塊、8位定時器和抽樣器各一個組成。模擬開關(guān)電容SC模塊完成信號的采集與轉(zhuǎn)換工作;8位定時器用于配置數(shù)據(jù)時鐘信號來控制采樣速率,采樣速率為O.125 ksps~31.25 ksps;△-∑型ADC里的抽樣器實際上是一個SINC2濾波器。在x域,它的傳遞函數(shù)如下:

其中的n是抽樣等級。這個抽樣濾波器是由軟硬件協(xié)同工作完成的。式(1)中分母部分的二次積分項由硬件實現(xiàn),分子部分的二次差分項的抽樣率計算由軟件實現(xiàn)。

2.2 動態(tài)可重新配置功能

嵌入式系統(tǒng)設(shè)計人員利用PSOC架構(gòu)的靈活性,在單個器件上動態(tài)地創(chuàng)建多種

配置,這是PSoC可編程片上系統(tǒng)的另一大特點。可以想象。這如同用FPGA進行設(shè)計,既使是在系統(tǒng)運行時,也可以對其硬件進行升級或重新配置。動態(tài)重新配置功能使設(shè)計人員能多次、重復(fù)使用芯片內(nèi)的模擬與數(shù)字資源,而無需增加成本和元件庫。

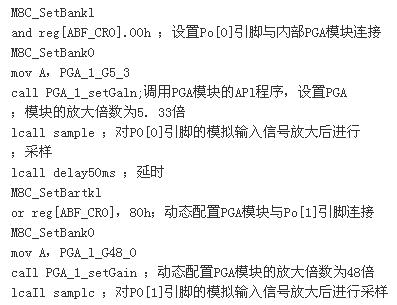

下面以PGA模塊為例,說明其動態(tài)配置功能。

(1)PGA模塊的資源及參數(shù)配置

PSoC微處理器中的PGA模塊擁有高的輸入阻抗、寬的帶寬增益和可動態(tài)配置的增益參數(shù),其功能建立在模擬連續(xù)時間CT模塊的基礎(chǔ)之上。通過對CT模塊的三個控制寄存器的配置,支持增益輸出或衰減輸出、配置信號輸入端口和輸出端口。完成一個PGA配置,需占用微處理器的內(nèi)部資源為:1個CT連續(xù)時間模擬模塊、1個外部I/O引腳以及生成PGA應(yīng)用程序API所需的52字節(jié)的Flash。圖3為可編程增益放大器PGA的結(jié)構(gòu)框圖。

對于增益≥1的運算放大器,可編程電阻風(fēng)、Rb、Ra串聯(lián),Rb一端連到放大器的輸出端。Ra一端連接VGND,VGND有多種選擇,用戶可根據(jù)不同需要將VGND接數(shù)字地、模擬地、內(nèi)部帶隙電壓或外部輸人電壓信號;Rb與Ra中間連接端連到放大器的負反饋輸人端。由此,可推出放大器的傳輸函數(shù)如下:

對于增益<1的衰減運算放大器,需配置成電壓跟隨器,可編程電阻Rb一端連到放大器的輸出端,Ra一端連到VGND,Rb與Ra中間連接端連到用戶模塊輸出端。由此,可推出負增益放大器的傳輸函數(shù)如下:

在應(yīng)用中,PGA模擬模塊的輸入端、增益參數(shù)、輸出端都可進行動態(tài)配置。其輸入端可以和一個模擬信號輸入引腳連接,也可以動態(tài)地將此PGA模塊與另一個模擬信號輸入引腳相連接,在不同時刻完成對多路模擬輸入信號的放大工作,而無需在單個器件上配置多個PGA模塊;其增益參數(shù)也可以動態(tài)調(diào)節(jié)(從負增益0.06倍到最大正增益48倍),極方便地拓展了PGA模塊的輸入電壓范圍;其輸出端也可以按需要動態(tài)地接到輸出引腳、A/D模塊輸入端或濾波器。其動態(tài)重配置部分的程序如下:

3 CY8C24223在感煙火災(zāi)探測器中的應(yīng)用

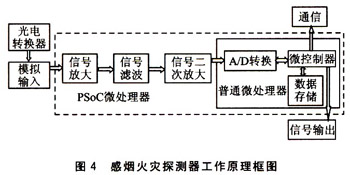

光電感煙火災(zāi)探測器應(yīng)用散射原理,將煙霧濃度的變化轉(zhuǎn)化為微弱的光電信號,經(jīng)放大和濾波處理后,進行A/D轉(zhuǎn)換,完成對煙霧濃度的檢測,實現(xiàn)火災(zāi)報警功能。感煙火災(zāi)探測器的工作原理框圖如圖4所示。

目前,光電感煙火災(zāi)探測器多使用帶A/D轉(zhuǎn)換的普通嵌入式微處理器,需通過外部電路完成信號的放大和濾波處理工作。在產(chǎn)品的原理設(shè)計過程中,需要反復(fù)對外部電路作硬件參數(shù)調(diào)整;在PCB板布線時,又要注意避免來自空間及器件間的電磁干擾。可以肯定,要解決這些問題是件非常復(fù)雜而費時的工作。

當(dāng)選用CY8C24223芯片作為探測器的微處理器時(虛線框內(nèi)為PSOC芯片內(nèi)所具有的模塊功能),與選用帶A/D功能的微處理器相比,節(jié)省了大量的外部資源,如放大器及其相關(guān)元器件、濾波元器件等等。設(shè)計人員可在PSoC的設(shè)備編輯器中,通過配置模擬模塊陣列和數(shù)字模塊陣列完成信號放大、濾波、模/數(shù)轉(zhuǎn)換、數(shù)據(jù)存儲、通信等工作,并避免了由于放大器等外圍器件在PCB布線時造成的電磁干擾問題。更為重要的是,用戶可根據(jù)環(huán)境的變化,如白天與夜晚、潔凈空間與污染空間,動態(tài)配置放大器的增益系數(shù),并實現(xiàn)多路模擬信號輸入的檢測,以降低火災(zāi)探測器的誤報率。

在探測器的快速原型設(shè)計中,通過片上系統(tǒng)的可編程混合信號陣列的集成應(yīng)用及動態(tài)配置,極大提高了工作效率,使開發(fā)成本降低了1/2,PCB的板級空間縮減了l/3,生產(chǎn)成本降低了1/10。

結(jié) 語

PSoC方便、快捷的設(shè)計界面,面向?qū)ο蟮脑O(shè)計開發(fā)系統(tǒng),混合信號陣列的模塊化及動態(tài)可配置功能使其在嵌入式系統(tǒng)應(yīng)用中擁有更為靈活的設(shè)計方式,使設(shè)計人員能夠隨意創(chuàng)建新的系統(tǒng)功能。利用PSoC可以快速、便捷地完成相應(yīng)程序的開發(fā)工作,縮短產(chǎn)品的研發(fā)周期,降低開發(fā)成本和生產(chǎn)成本。