IP over SDH(PoS)技術(shù)是通過(guò)SDH提供的高速傳輸通道直接傳送IP分組,它位于數(shù)據(jù)傳輸骨干網(wǎng),使用點(diǎn)到點(diǎn)協(xié)議PPP將IP數(shù)據(jù)包映射到SDH幀上,按各次群相應(yīng)的線速率進(jìn)行連續(xù)傳輸,其網(wǎng)絡(luò)主要由大容量的高端路由器經(jīng)由高速光纖傳輸通道連接而成。這種技術(shù)實(shí)際上是對(duì)傳統(tǒng)IP網(wǎng)絡(luò)概念的延續(xù),完全兼容傳統(tǒng)的IP協(xié)議體系,只是在物理通道上借助SDH提供的點(diǎn)到點(diǎn)物理連接,從而使速率提高到Gbit/s量級(jí),因此PoS技術(shù)現(xiàn)在和今后都將是非常重要的IP網(wǎng)絡(luò)傳輸手段。

155Mbit/s PoS接口是IPv6路由器所提供的一種重要的PoS接口,本文介紹基于PMC公司PM5380型8×155Mbit/s和Xilinx公司VIRTEX-II PRO型300萬(wàn)門(mén)的大規(guī)模可編程器件的網(wǎng)絡(luò)接口硬件設(shè)計(jì)與實(shí)現(xiàn)方案,也給出其中關(guān)鍵的FPGA設(shè)計(jì)。該設(shè)計(jì)在國(guó)家數(shù)字交換系統(tǒng)工程技術(shù)研究中心研制的IPv6路由器(國(guó)家863重大項(xiàng)目)中已經(jīng)獲得實(shí)現(xiàn),性能良好。

1 155Mbit/s PoS接口工作原理

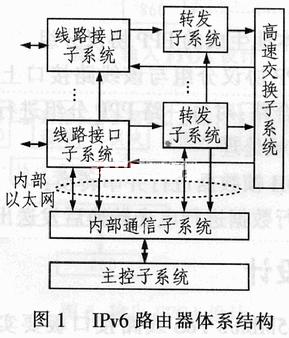

1.1 IPv6路由器體系結(jié)構(gòu)

IPv6路由器主要包含如下子系統(tǒng):線路接口子系統(tǒng)、多功能轉(zhuǎn)發(fā)子系統(tǒng)(“多功能”主要是指該轉(zhuǎn)發(fā)系統(tǒng)支持多種協(xié)議類型:IPv4、IPv6、MPLS)、高速交換子系統(tǒng)和主控(完成各個(gè)子系統(tǒng)的管理,集中處理本路由器收到的路由信息,計(jì)算并更新路由表)以及OAM(操作維護(hù)臺(tái))。圖1是IPv6路由器的體系結(jié)構(gòu)。

不同類型的網(wǎng)絡(luò)分別通過(guò)相應(yīng)類型的線路接口接入路由器,數(shù)據(jù)從線路接口進(jìn)入路由器后再進(jìn)行轉(zhuǎn)發(fā)和交換,在此過(guò)程獲取指明下一路網(wǎng)絡(luò)的路的信息,最終從相應(yīng)的接口以輸出網(wǎng)絡(luò)要求的格式輸出。PoS線路接口就是是線路接口子系統(tǒng)的一種。

1.2 155Mbit/s PoS接口的工作原理

155Mbit/s PoS線路接口板的設(shè)計(jì)目標(biāo)是為IPv6路由器提供8個(gè)155Mbit/s PoS接口,并支持IPv4、IPv6和MPLS包。在接收方向上將封裝在SDH幀中的IP包提取出來(lái)送到協(xié)議處理單元或轉(zhuǎn)發(fā)模塊處理;在發(fā)送方向上將IP包封裝在SDH幀中,然后送到SDH傳送網(wǎng)上。

155Mbit/s PoS線路接口板的主要功能就是實(shí)現(xiàn)IP數(shù)據(jù)包和SDH幀的映射和去映射,具體功能可從接收和發(fā)送二個(gè)方向詳細(xì)描述。

在接收方向(到達(dá)路由器)的主要功能有:

·接收外部線路光信號(hào),進(jìn)行光/電轉(zhuǎn)換,以串行數(shù)據(jù)輸出;

·對(duì)串行數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換,得到SDH幀;

·對(duì)SDH幀進(jìn)行去開(kāi)銷和拆幀處理,輸出SDH網(wǎng)管信息并提取出HDLC幀;

·從HDLC幀中提取出PPP分組;

·檢測(cè)PPP分組類型,區(qū)分PPP協(xié)議分組和PPP數(shù)據(jù)分組;

·對(duì)于PPP協(xié)議分組,送到線路接口處理機(jī)去處理;

·對(duì)于PPP數(shù)據(jù)分組,提取出其中的IP包或MPLS包,按照要求格式轉(zhuǎn)換后送到緩存(FIFO)中。 發(fā)送方向(離開(kāi)路由器)的主要功能有:

·接收輸出處理模塊的IP分組,去除內(nèi)部IP包頭,形成PPP分組,并將它輸出到相應(yīng)的線路接口上;

·接收本地生成的PPP協(xié)議分組;

·將PPP協(xié)議分組與該線路接口上的PPP數(shù)據(jù)分組進(jìn)行合路;對(duì)每一路PPP分組進(jìn)行HDLC成幀和SDH成幀處理;

·對(duì)SDH幀數(shù)據(jù)進(jìn)行并串行轉(zhuǎn)換;

·將串行數(shù)據(jù)進(jìn)行電光轉(zhuǎn)換后發(fā)送出去。

2 系統(tǒng)設(shè)計(jì)

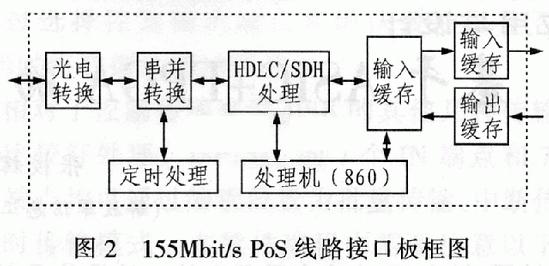

根據(jù)155Mbit/s PoS線路接口板要實(shí)現(xiàn)的主要功能和PoS的工作原理,可以將155M PoS線路接口分為8個(gè)模塊:光電轉(zhuǎn)換模塊、定時(shí)處理模塊、串并轉(zhuǎn)換模塊、SDH和HDLC處理模塊、PPP處理模塊、處理機(jī)模塊、輸入緩存模塊和輸出緩存模塊,其邏輯結(jié)構(gòu)框圖如圖2所示。

其中,光電轉(zhuǎn)換模塊主要實(shí)現(xiàn)光信號(hào)和電信號(hào)之間的轉(zhuǎn)換。定時(shí)處理模塊負(fù)責(zé)從接收的串行數(shù)據(jù)中提取時(shí)鐘信號(hào)。串并轉(zhuǎn)換模塊實(shí)現(xiàn)串行數(shù)據(jù)和并行數(shù)據(jù)之間的轉(zhuǎn)換。在接收方向上,在對(duì)信號(hào)進(jìn)行串并轉(zhuǎn)換之前,對(duì)于串行的輸入數(shù)據(jù)需要進(jìn)行幀和字節(jié)邊界的檢測(cè)。SDH和HDLC處理模塊是155M PoS線路接口的關(guān)鍵模塊,完成STM-1的映身教 處理及HDLC幀格式的封裝和拆裝。PPP處理模塊主要完成對(duì)PPP分組的硬件處理。處理機(jī)模塊負(fù)責(zé)單板的初始化、狀態(tài)監(jiān)測(cè)和控制、處理PPP協(xié)議分組以及與主控通信等任務(wù)。輸入緩存用來(lái)存放線路接口發(fā)送轉(zhuǎn)發(fā)處理的數(shù)據(jù)包,輸出緩存用來(lái)存放調(diào)度輸出后送給線路接口的數(shù)據(jù)包。

根據(jù)目前的技術(shù)水平,可選擇如下方案:光電轉(zhuǎn)換模塊由專用的光電器件完成,串并轉(zhuǎn)換、定時(shí)處理、HDLC/SDH等物理層處理功能由專用電路完成,而PPP處理由FPGA完成。

3 關(guān)鍵電路的選型及說(shuō)明

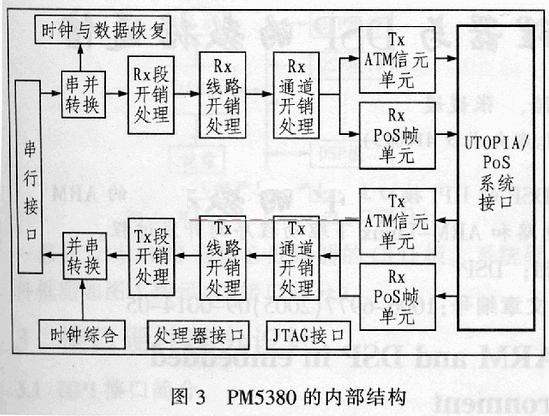

物理層處理電路采用PMC公司的PM5380,它是一款新型的PoS/ATM專用處理電路,支持8路獨(dú)立的ATM/PoS接口。該電路具有極高的集成度,將定時(shí)提取模塊、串行轉(zhuǎn)換模塊、段開(kāi)銷處理模塊、通道開(kāi)銷處理模塊、路開(kāi)銷處理模塊和HDLC處理模塊等集成到一起,功能非常強(qiáng)大。其內(nèi)部結(jié)構(gòu)見(jiàn)圖3。

PM5380的設(shè)計(jì)符合IETF PPP工作組提出的PPP over SDH/SONET規(guī)范;支持8路全雙工155Mbit/s的STM-1接口,并帶有數(shù)據(jù)和時(shí)鐘恢復(fù)(CDR)電路;完全符合Utopia-2接口規(guī)范,支持多地址和奇偶校驗(yàn);對(duì)PoS應(yīng)用提供相

當(dāng)于Utopia-2的系統(tǒng)接口,16位總線寬度,支持包傳送和字節(jié)傳送,內(nèi)置8個(gè)FIFO緩存對(duì)應(yīng)接口的數(shù)據(jù);提供串行的155Mbit/s的接口與光器件對(duì)接,并且都是差分線路;提供一個(gè)通用的八位微處理器接口來(lái)完成PM5380的初始化配置、工作控制以及狀態(tài)監(jiān)測(cè);支持線路環(huán)回、串行環(huán)回和并行環(huán)回;單電源3.3VCMOS制作工藝,輸入兼容PECL和TTL電平,輸出為T(mén)TL電平。在本設(shè)計(jì)中,需要通過(guò)處理機(jī)配置相應(yīng)的寄存器,使PM5380工作于PoS模式。

FPGA選用Xilinx公司VIRTEX-II PRO,該電路是300萬(wàn)門(mén)級(jí)的FPGA,其高速I(mǎi)/O模塊可提供多達(dá)16路Rocket I/O,內(nèi)置Power PC核提供高性能的數(shù)字時(shí)鐘管理,并且具有強(qiáng)大的開(kāi)發(fā)軟件支持。

4 實(shí)現(xiàn)方案

圖4為155Mbit/s PoS接口的實(shí)現(xiàn)方案圖。在輸入方向上,從光纖傳入的信號(hào)經(jīng)光電轉(zhuǎn)換后送入PM5380,完成定時(shí)處理、幀同步,從輸入比特流中提取出SDH幀并進(jìn)而恢復(fù)出PPP幀,并按接口緩存于內(nèi)部8個(gè)FIFO中。輸入鏈路處理模塊輪詢讀取PM5380的FIFO,獲得PPP幀并完成PPP相關(guān)處理,恢復(fù)出IP報(bào)文并且完成查IP地址表的工作,將協(xié)議報(bào)文交處理機(jī),而普通的數(shù)據(jù)報(bào)文合路輸入FIFO,進(jìn)而通過(guò)FPGA的Rocket I/O(高速I(mǎi)/O)送轉(zhuǎn)發(fā)處理。

在輸出方向上,從轉(zhuǎn)發(fā)過(guò)來(lái)的數(shù)據(jù)報(bào)文 經(jīng)Rocket I/O送FPGA內(nèi)部,在輸出鏈路處理模塊中完成與協(xié)議報(bào)文的合路并且封裝成PPP幀,然后根據(jù)內(nèi)部報(bào)文格式中的出接口號(hào)來(lái)判斷送往ASIC的哪個(gè)接口;ASIC完成SDH幀的映射,最后經(jīng)電光轉(zhuǎn)換通過(guò)光纖送到外部SDH網(wǎng)絡(luò)。

5 FPGA設(shè)計(jì)

圖5中的虛線框內(nèi)為輸入FPGA設(shè)計(jì)原理。輸入FPGA的輪詢接收模塊從PM5380的FIFO中輪詢讀取8個(gè)外部接口的數(shù)據(jù),并將完整的PPP包緩存;分揀模塊查本地IP表,將協(xié)議報(bào)文緩存于協(xié)議FIFO并經(jīng)處理機(jī)送交主控處理,需轉(zhuǎn)發(fā)的數(shù)據(jù)報(bào)文送轉(zhuǎn)發(fā)FIFO。圖中的MPM5380管理模塊負(fù)責(zé)產(chǎn)生處理機(jī)管理PM5380時(shí)所需要的時(shí)序,CPU模塊負(fù)責(zé)和860的交互,時(shí)鐘模塊產(chǎn)生系統(tǒng)時(shí)鐘,它們是公共模塊。

圖6示出輸出FPGA設(shè)計(jì)原理。從轉(zhuǎn)發(fā)過(guò)來(lái)的數(shù)據(jù)經(jīng)Rocket I/O后緩存于輸出FIFO,合路模塊將數(shù)據(jù)報(bào)文和從處理機(jī)下發(fā)的協(xié)議報(bào)文合路送發(fā)送模塊按照PM5380要求的時(shí)序?qū)懙较鄳?yīng)接口的FIFO中發(fā)送,但這里必須嚴(yán)格滿足PM5380的寫(xiě)時(shí)序要求。

6 結(jié)束語(yǔ)

本文根據(jù)IPv6路由器155Mbit/s PoS接口的需求,提出并實(shí)現(xiàn)了一種基于ASIC+FPGA的設(shè)計(jì)方案。目前該方案已經(jīng)在國(guó)家數(shù)字交換系統(tǒng)工程技術(shù)研究中心開(kāi)發(fā)的IPv6路由器中得到實(shí)現(xiàn),測(cè)試后的系統(tǒng)性能穩(wěn)定,達(dá)到了預(yù)期的設(shè)計(jì)目標(biāo)。