長期以來,降低功耗一直是芯片設(shè)計(jì)中的重要需求。隨著更大、更快的集成電路應(yīng)用于便攜式產(chǎn)品中,這個(gè)需求變得日益重要。因此,貫穿整個(gè)設(shè)計(jì)流程的功率管理技術(shù)也在不斷改進(jìn),以確保產(chǎn)品的各個(gè)部分均得到適當(dāng)、高效的功率供應(yīng),同時(shí)保證產(chǎn)品的可靠性。諸如多電壓島,以及時(shí)鐘頻率和閾值電壓的動(dòng)態(tài)調(diào)整等技術(shù),均有助于在提供高性能的同時(shí),節(jié)省便攜產(chǎn)品中的電池能量。

更為重要的是,SOC在尺寸和速度方面的增長已經(jīng)給大量的設(shè)計(jì)帶來了功耗方面的挑戰(zhàn),而這些挑戰(zhàn)并不屬于傳統(tǒng)的受供電限制的范疇。在這些設(shè)計(jì)中,熱耗散和可靠性方面的問題,例如電遷移和電壓降已經(jīng)變得極為關(guān)鍵。深亞微米設(shè)計(jì)中的功率問題可能會(huì)限制設(shè)計(jì)的功能或性能,并嚴(yán)重影響到芯片的可制造性和良率。較高的功耗會(huì)造成結(jié)點(diǎn)區(qū)溫度上升,導(dǎo)致晶體管動(dòng)作速度變慢,并增加互連電阻。如果不考慮功率問題,會(huì)導(dǎo)致器件性能低于預(yù)期,進(jìn)而使得器件良率下降。此外,較高的功耗會(huì)要求在溫度管理方面采取更多的系統(tǒng)級(jí)措施。總而言之,這些功率問題正在造成

SoC和系統(tǒng)成本的增加。在SoC設(shè)計(jì)流程中進(jìn)行功耗管理,能夠有效控制這些成本。

SoC中的功耗

芯片的總功率等于動(dòng)態(tài)功率加上靜態(tài)功率。動(dòng)態(tài)功率是指在開關(guān)邏輯狀態(tài)轉(zhuǎn)換過程中所消耗的功率,包括單元內(nèi)部(內(nèi)部功率)和驅(qū)動(dòng)芯片節(jié)點(diǎn)及外部負(fù)載的功率(開關(guān)功率)。動(dòng)態(tài)功率 = CV2F其中,C為負(fù)載,V為電壓擺幅,F(xiàn)為邏輯狀態(tài)轉(zhuǎn)換的頻率。隨著半導(dǎo)體器件結(jié)構(gòu)日趨小型化,器件和互連電容降低,芯片獲得了更高的性能和更低的功耗。而更大規(guī)模的設(shè)計(jì)以及更高的開關(guān)速率將會(huì)導(dǎo)致功率增加。靜態(tài)功率(泄漏功率)是指在晶體管不進(jìn)行開關(guān)動(dòng)作時(shí)消耗的功率。

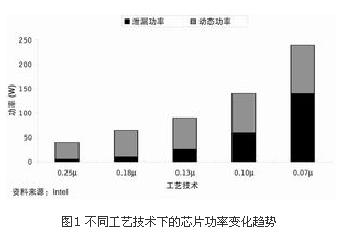

靜態(tài)功率=VISTAT盡管在晶體管漏極和襯底之間的一些反向偏置二極管中存在著漏電流,但大部分泄漏功率來自晶體管關(guān)斷時(shí)的亞閾值電流。由于亞閾值漏電流隨著晶體管閾值電壓(Vth)的降低而增大,從而帶來了一定的麻煩。隨著工藝技術(shù)向130nm及以下不斷發(fā)展,泄漏功率可能會(huì)占到芯片總功率的50%(見圖1)。泄漏功率的增加,會(huì)使得芯片中與可靠性相關(guān)的故障(即使是在待機(jī)狀態(tài)下)呈指數(shù)增長。

隨著CMOS工藝尺寸的減小,降低功率的主要方法轉(zhuǎn)為降低供電電壓VDD。由于功率和電壓的平方成正比,所以降低電壓對(duì)于控制芯片的動(dòng)態(tài)功率極為有效。但是,由于開關(guān)延遲時(shí)間與負(fù)載電容和Vth/VDD成正比,因此,僅降低供電電壓會(huì)導(dǎo)致電路速度降低。為了保證快速開關(guān)所需的足夠的驅(qū)動(dòng)能力,Vth必須與VDD成正比下降,這又會(huì)導(dǎo)致泄漏功率的增加。較好的方式是采用考慮了功率管理的設(shè)計(jì)流程,在時(shí)序要求和各類功耗目標(biāo)之間取得平衡。

功率解決方案

設(shè)計(jì)抽象層次越高,對(duì)功耗的影響也就越大。例如,在系統(tǒng)級(jí)和算法級(jí)上,采用并行實(shí)現(xiàn)而非串行實(shí)現(xiàn)能夠降低時(shí)鐘頻率,從而顯著降低功耗。但并行方法的低功率可能要以面積增加或性能降低為代價(jià)。

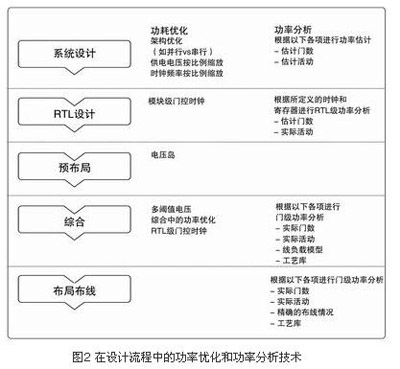

以一個(gè)用于串行接收數(shù)據(jù)樣本的芯片為例,來說明并行架構(gòu)與串行架構(gòu)的不同效果。將數(shù)據(jù)樣本并行處理,可將芯片邏輯電路的時(shí)鐘從80MHz降低至10MHz,供電電壓也可從1.8V降低至1.25V。并行處理邏輯電路要比相同的串行處理電路的面積大得多,但較低的電壓和工作頻率可將功耗降低75%。在其它一些設(shè)計(jì)中,占用面積上付出的代價(jià)較小,而功率節(jié)省效果卻很明顯,所以這是值得探索的一種折衷方案。圖2中介紹了幾種功率優(yōu)化和分析的技術(shù),這些技術(shù)在SoC的整個(gè)設(shè)計(jì)流程中均可得到應(yīng)用。本文所涉及的功率解決方案如下:(1)模塊門控時(shí)鐘(2)多供電電壓;(3)多閾值電壓;(4)綜合過程中的功率優(yōu)化,包括RTL級(jí)門控時(shí)鐘。

功率估計(jì)和分析

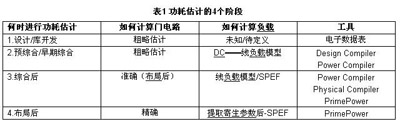

設(shè)計(jì)過程中,在如表1所示的4個(gè)階段內(nèi)進(jìn)行功耗估計(jì)是非常有用的。每個(gè)階段所估計(jì)的功耗準(zhǔn)確度隨增補(bǔ)設(shè)計(jì)和可利用的庫信息的增加而提高。

&nb sp; RTL級(jí)功率分析

在設(shè)計(jì)流程早期,功率分析可對(duì)設(shè)計(jì)的功耗進(jìn)行粗略估計(jì)。此時(shí)可能尚未選擇庫,所以庫數(shù)據(jù)有限,這時(shí),電子數(shù)據(jù)表(spreadsheet)分析可以用于找出最佳的注重功率的庫和設(shè)計(jì)架構(gòu)。在選定庫之后,即可用Design Compiler和Power Compiler來代替電子數(shù)據(jù)表,或向電子數(shù)據(jù)表提供數(shù)據(jù)。

功率分析的電子數(shù)據(jù)表中包含了大致的門數(shù)和每個(gè)模塊的活動(dòng)值、mW/MHz數(shù)據(jù)以及相關(guān)的功率估計(jì)。這時(shí)進(jìn)行的分析也有助于確認(rèn)一項(xiàng)設(shè)計(jì)的功耗是否過大而不現(xiàn)實(shí),從而可避免花費(fèi)數(shù)周時(shí)間來實(shí)現(xiàn)一個(gè)根本無法制造的設(shè)計(jì)方案。

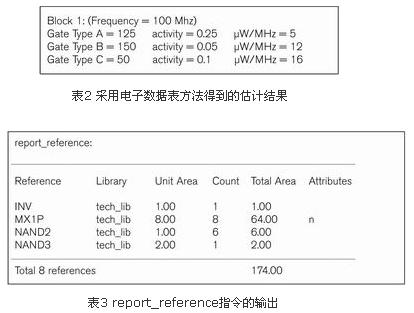

為了使用電子數(shù)據(jù)表分析方法,有必要對(duì)每一模塊的門數(shù)(每一種類型的庫單元數(shù)量)和活動(dòng)水平進(jìn)行估計(jì)。同時(shí)還需知道每種類型的單元在開關(guān)時(shí)所耗費(fèi)的能量,庫供應(yīng)商手冊(cè)中的數(shù)據(jù)可用于確定正確的功率速度比(mW/MHz)。一個(gè)模塊內(nèi)每種類型的單元的內(nèi)部功耗可由

下式計(jì)算:功耗=門數(shù)×mW/MHz×活動(dòng)×頻率。將一個(gè)模塊內(nèi)所有不同類型的單元的功率加在一起,就可得出這一模塊總的內(nèi)部動(dòng)態(tài)功率的估計(jì)值。在綜合前,可根據(jù)所選擇的體系結(jié)構(gòu)和對(duì)設(shè)計(jì)本身的理解來對(duì)門數(shù)進(jìn)行估計(jì)。例如,從總線寬度、字長、控制層和存儲(chǔ)器深度等可得出大致的門數(shù)。在選擇了庫以后,模塊的門數(shù)就可以利用Design Compiler的report-reference命令在初期綜合后進(jìn)行估計(jì),這項(xiàng)功能將報(bào)告設(shè)計(jì)中每個(gè)例化設(shè)計(jì)的數(shù)量。功率計(jì)算的一個(gè)關(guān)鍵方面是指定活動(dòng)水平。設(shè)計(jì)中的門電路都具有不同的活動(dòng)水平,在對(duì)設(shè)計(jì)進(jìn)行仿真提取開關(guān)動(dòng)作或不進(jìn)行仿真的情況下進(jìn)行估計(jì)均可。但在選擇了庫之后,推薦進(jìn)行功能仿真來確定開關(guān)動(dòng)作。

開關(guān)動(dòng)作以翻轉(zhuǎn)率(TR)衡量。翻轉(zhuǎn)率是指在單位時(shí)間內(nèi),一個(gè)設(shè)計(jì)對(duì)象(如節(jié)點(diǎn)、引腳或端口)從邏輯0至邏輯1以及從邏輯1至邏輯0進(jìn)行轉(zhuǎn)換的次數(shù)。對(duì)于一個(gè)節(jié)點(diǎn)來說,如果它在100ns的時(shí)間間隔內(nèi)有50次從邏輯1至邏輯0的轉(zhuǎn)換,以及50次從邏輯0至邏輯1的轉(zhuǎn)換,則其翻轉(zhuǎn)率為1,表示每ns有1次動(dòng)作轉(zhuǎn)換。功率與轉(zhuǎn)換率之間的關(guān)系可以理解為,在狀態(tài)改變的時(shí)間間隔內(nèi),為了完成內(nèi)部電路的狀態(tài)轉(zhuǎn)換,就必須提供一定的能量,因此,每次轉(zhuǎn)換都會(huì)消耗功率。

重要的是,只有在開關(guān)動(dòng)作代表了芯片的實(shí)際工作狀態(tài)的情況下,在任何抽象層次上的功率估計(jì)才有意義。常見的錯(cuò)誤是在試圖確定活動(dòng)時(shí),使用一個(gè)向量來仿真系統(tǒng)啟動(dòng)序列。此項(xiàng)活動(dòng)極少能夠代表真實(shí)的工作狀況,因而會(huì)導(dǎo)致不準(zhǔn)確的功率估計(jì)。采用RTL級(jí)仿真能夠自動(dòng)生成一個(gè)SAIF(Switching Activity Interchange Format)文件,但是活動(dòng)值只有在此向量現(xiàn)實(shí)時(shí)才是準(zhǔn)確的。目前的工具尚不能自動(dòng)生成這樣的向量,因?yàn)樗枰獙?duì)電路的實(shí)質(zhì)有明確的理解。

圖3所示為可以在VCS內(nèi)使用的編程語言接口(PLI)系統(tǒng)任務(wù),用于在仿真期間生成SAIF文件。Power Compiler提供了一項(xiàng)power_estimate功能,這項(xiàng)功能使用SAIF文件來定義庫和約束條件,以及對(duì)設(shè)計(jì)進(jìn)行注釋,以用于功率估計(jì)。Power Compiler針對(duì)未注釋端口的默認(rèn)開關(guān)動(dòng)作是,每個(gè)上升沿有1/4的概率翻轉(zhuǎn),此數(shù)值在整個(gè)模塊內(nèi)應(yīng)用和傳送。

表2和表3所示為采用上述方式的估計(jì)結(jié)果。計(jì)算出內(nèi)部功率之后,開關(guān)功率可以按內(nèi)部功率的30%進(jìn)行估計(jì)。由于沒有精確的負(fù)載和開關(guān)數(shù)據(jù),此數(shù)值僅為粗略的估計(jì)值。這樣的估計(jì)主要用于對(duì)不同設(shè)計(jì)方案的功耗進(jìn)行比較,而非用于預(yù)測(cè)芯片的實(shí)際功耗。但是,正如前文所述,RTL級(jí)的近似估計(jì)的確能夠在早期對(duì)芯片設(shè)計(jì)的可實(shí)現(xiàn)性提供參考意見。

泄漏功率可以根據(jù)每種單元類型的泄漏數(shù)據(jù)進(jìn)行估算。由于高態(tài)和低態(tài)下的泄漏不同,所以泄漏功率分析必須在信號(hào)處于一定邏輯狀態(tài)的靜態(tài)概率的基礎(chǔ)上進(jìn)行。靜態(tài)概率表示為0至1之間的一個(gè)數(shù),該數(shù)值可以根據(jù)信號(hào)的功能進(jìn)行估計(jì)。例如,一般情況下,一個(gè)低態(tài)有效的復(fù)位信號(hào)的邏輯“1”靜態(tài)概率(SP1)等于或接近1.0(100%)。對(duì)于一個(gè)數(shù)據(jù)總線信號(hào)而言,除非某些架構(gòu)特性建議有其它概率,其SP1通常可以 假設(shè)為0.5(50%)。在選定了庫之后,靜態(tài)概率可在仿真期間,通過將信號(hào)處于某一特定邏輯狀態(tài)下的時(shí)間和總仿真時(shí)間進(jìn)行比較來計(jì)算得到。

門電路級(jí)功率分析

在綜合完成后,有可能根據(jù)實(shí)際門數(shù)和仿真得到的活動(dòng)來從Power Compiler中獲得相當(dāng)精確的功率估計(jì)值。這時(shí)估計(jì)的不準(zhǔn)確性來自活動(dòng)以及布局前的線負(fù)載值。通過從門級(jí)仿真中生成SAIF文件,準(zhǔn)確性可以得到改善。在VCS中,與圖3中相同的指令可用于生成SAIF文件,只是其中的第一條指令應(yīng)當(dāng)改為:

$set_gate_level_monitoring ("on");

這里必須再次強(qiáng)調(diào),只有在仿真向量代表了真實(shí)的應(yīng)用行為時(shí),活動(dòng)值才是準(zhǔn)確的。Physical Compiler工具在物理優(yōu)化后使用write_parasitics -distributed指令用于改善負(fù)載的準(zhǔn)確性,這項(xiàng)指令能夠產(chǎn)生注釋了S

teiner路徑和寄生電阻、電容估計(jì)值的SPEF文件。

布局完成后,門級(jí)仿真能夠生成VCD(Value Change Dump)文件,用于PrimePower分析。VCD文件的記錄在仿真過程中變?yōu)橐粋€(gè)信號(hào)值,并提供了設(shè)計(jì)的節(jié)點(diǎn)活動(dòng)、結(jié)構(gòu)數(shù)據(jù)體系連接性、路徑延遲、時(shí)序和事件方面的信息。

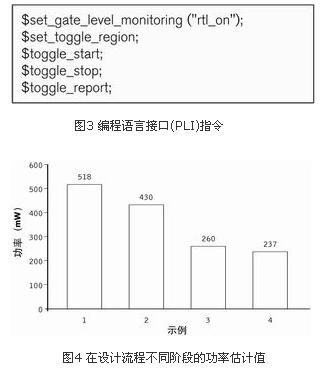

如果芯片的I/O數(shù)量眾多、在高速下切換開關(guān)并驅(qū)動(dòng)很長的線路,那它將有可能成為造成估計(jì)不準(zhǔn)確的重要因素。如果設(shè)計(jì)目標(biāo)要求得到準(zhǔn)確而非最壞情況下的功率估計(jì)時(shí),I/O的集總負(fù)載模型可能會(huì)產(chǎn)生過分悲觀的估計(jì)結(jié)果。要想獲得更為準(zhǔn)確的結(jié)果,可以在關(guān)鍵的I/O單元類型中利用精確的分布阻抗模型進(jìn)行HSPICE仿真。然后,I/O單元的功率即可采用確定每次上升/下降沿的電荷和能量的數(shù)值性方法來進(jìn)行計(jì)算。在得到HSPICE的電流和時(shí)間輸出后,每個(gè)瞬態(tài)的內(nèi)部功率就可以利用梯形積分法(如在Matlab軟件中)來進(jìn)行計(jì)算。在PrimePower分析中記錄的I/O活動(dòng)可以用于對(duì)I/O功率按比例進(jìn)行調(diào)整,同時(shí)總的I/O功率可與核心功率相結(jié)合,用于整體功率估計(jì)。為了表明在采用本文所述的不同設(shè)計(jì)階段和實(shí)施循環(huán)中的估計(jì)方法所獲得的功率估計(jì)值的差別,圖4列舉了在DSP設(shè)計(jì)中的一個(gè)高速FIR濾波器模塊的實(shí)例。這一實(shí)例驗(yàn)證了,根據(jù)所提供的信息準(zhǔn)確度的不同,功率估計(jì)值會(huì)有所差異。此圖也表明了范例模塊在設(shè)計(jì)流程中的4個(gè)不同階段下功率估計(jì)值的變化情況:

(1)示例1-采用最壞情況下的開關(guān)動(dòng)作和線負(fù)載估計(jì)值所得到的功率估計(jì)值;

(2)示例2-采用較為準(zhǔn)確的線負(fù)載估計(jì)值和最壞情況下的開關(guān)動(dòng)作所得到的功率估計(jì)值;

(3)示例3-采用準(zhǔn)確的線負(fù)載估計(jì)值和實(shí)際活動(dòng)所得到的功率估計(jì)值;

(4)示例4-采用精確的線負(fù)載(提取后)和基于SPICE準(zhǔn)確仿真的實(shí)際活動(dòng)所得到的功率估計(jì)值。■