功率優(yōu)化技術

圖5中,根據靜態(tài)與動態(tài)功率以及這些技術所應用的設計抽象層次,對各項功率優(yōu)化技術進行了分類。使用這些方法中的哪項或哪幾項要取決于設計目標。將這些方法結合到設計流程中,就形成了一種集成式的功率管理設計策略。

模塊門控時鐘

模塊門控時鐘可用于體系結構層次,對不在使用狀態(tài)下的某些設計部分禁用時鐘。Power Compiler能夠替換手動插入的門控時鐘邏輯電路,運用庫的ICG(集成門控時鐘)單元控制時鐘進入任何模塊。一旦用戶在腳本中創(chuàng)建出時鐘,此工具就能自動確定這樣的組合邏輯。

模塊門控時鐘可以應用于一系列的層次上,包括芯片級、域級(DSP、CPU等)、模塊和子模塊。當整個芯片處于空閑模式,但必須對外

部的喚醒事件做出響應時,可通過應用程序來對芯片時鐘進行門控。在最低層次上也同樣適用,當不需要訪問存儲器時,在SDRAM首先設定為自刷新模式后,SDRAM控制器中的時鐘可以關閉。除將時鐘關閉和打開以外,門控結構還可以包括可配置的時鐘信號分頻器,用于改變不同設計部分的時鐘速率。

設計這樣的時鐘結構要對芯片功能及功率分析有充分的了解。總的來說,時鐘開關功耗占據了芯片總功耗的30%以上,因此門控時鐘通常能夠獲得良好效果。

門控時鐘遇到的挑戰(zhàn)

除了確定在哪里和怎樣進行門控時鐘和(或)時鐘分頻以外,高層次的門控時鐘還涉及一系列的時序和可測性設計方面的問題。對時序問題可通過觀察時鐘結構中一段較長的路徑來進行了解,這段路徑可以包含一個數字式鎖相環(huán)、一個時鐘分頻器、多個模式開關多路轉換器和多級門控時鐘。

在用諸如Astro CTS(時鐘樹綜合)等工具對典型芯片進行高質量的時鐘樹綜合后,復雜的門控時鐘和分頻器會要求手動干預,在大多數情況下是要求修改工具范圍以外的設計部分,例如,為了防止出現嚴重的時鐘相位延遲,因而需要進入干預。

寄存器和高層次時鐘體系內的非CTS單元放置得過遠,會造成高層次擴展時鐘樹插入延遲的增加,并因此導致時鐘相位延遲的增加。非CTS單元的基于網絡權重的布局控制能夠避免這一問題。該方法可以提取連接門控時鐘單元、開關多路轉換器和受驅動的CTS宏的節(jié)點,從而在布局優(yōu)化中,將較重的網絡權重應用在這些節(jié)點上,并將這些單元的距離拉近。這項優(yōu)化技術能夠使單元的負載最小化,并因此使單元延遲和輸出回轉(slew)最小。

對時鐘分配效果不佳的布局也會導致相位延遲問題。這是由于時鐘樹綜合是根據時鐘樹里最長分支的延遲特性來平衡整個時鐘樹,因此,布局不當會造成單獨一根很長的時鐘通路,使得整個時鐘樹的插入延遲增加。適當的布局限制可以更好地平衡時鐘樹,防止這一問題的發(fā)生。

其它導致時鐘相位延遲的原因包括非CTS單元的布局不當,以及非CTS單元輸出回轉過大。Synopsys公司針對這些問題給出了解決方案,并提出了其它三種時鐘分布問題的處理方法:減少時鐘扭曲、減少時鐘占空比失真和提高門控時鐘效率。

由于受到上市時間的限制,手動時鐘樹分析和平衡方法不適用于復雜的ASIC設計。Synopsys公司提供了一項時鐘平衡自動化策略,這項自動化策略包括三個步驟:提取一個通用的共享時鐘分布拓撲、針對每個不適合通用時鐘分布的時鐘路徑定義局部平衡策略,以及將這些局部平衡限制條件與通用時鐘分布的限制條件相結合。其結果是生成用于CTS工具的時鐘樹綜合限制條件,對整個時鐘分布進行自動平衡。

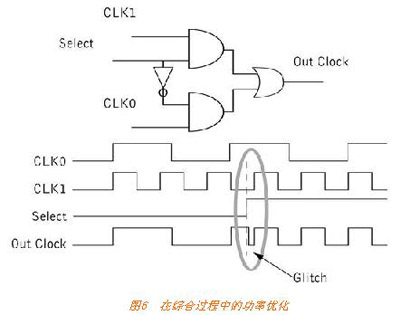

另一項時序問題是,在異步重新啟動時鐘時會出現時鐘毛刺,因此,有必要在設計中包含對重新啟動進行定時的電路,以避免出 現毛刺現象。

多電壓島

在門控時鐘對動態(tài)功率進行限制時,使用多種供電電壓和(或)多種閾值電壓有助于管理動態(tài)功率和泄漏功率。閾值電壓不必與供電電壓一起按比例縮放。

電壓島或電壓域的使用提供了一種同時滿足功耗和性能要求的方法。在本方案中,邏輯電路部分根據功能分為獨立的區(qū)域組,必須工作在最高速度下的區(qū)域采用最高的供電電壓,對時序要求不太嚴格的區(qū)域采用較低的供電電壓。

頻率有必要跟電壓一起按比例縮放,這樣,電壓島方法就能與門控時鐘進行良好的配合。門控時鐘模塊中的邏輯電路持續(xù)消耗泄漏功率,但是通過降低此模塊的供電電壓就能減小泄漏功率。

多供電電壓必須通過單獨的供電引腳或集成到器件內的模擬電壓調節(jié)器來提供。這些電壓調節(jié)器的效率必

須包含在器件的功率計算中。如果僅有小部分的設計工作在較低的電壓下,則在電壓調節(jié)器中耗費的功率可能會大于低壓邏輯電路中節(jié)省的功率。另外,電壓島的設計可能需要采用電平轉換單元,以確保在電壓域之間信號傳輸的正確轉換。

除了降低供電電壓外,還可以根據系統要求改變某一電壓島的供電電壓。相對于其它挑戰(zhàn)而言,這種方法要求采用已經在所有電壓下經過特性化的單元。Synopsys的可縮放多項式模型(Scalable Pdynomial Model, SPM)支持必要的時序和功率信息,非線性查找表格模型(Non-Linear look-up table Model, NLM)也可用于電壓島的設計。SOC還可以設計電源關斷的特定電壓島,以消除它們的泄漏功率。這些電壓島要求采用電源隔離單元,可以是簡單的"與"門。從電源關斷部分進入有源域的輸出絕對不允許出現漂移,電源隔離邏輯確保有源域的所有輸入信號均箝位在穩(wěn)定的數值上。另外,還可能需要采用狀態(tài)保持技術,從而保證模塊能在通電時恢復運行。對各個電壓島進行電源關斷或對電壓進行動態(tài)按比例縮放時,也可能需要電源排序電路,以確保芯片的正確運行。

多閾值設計

多供電電壓島與多閾值綜合之間可以良好配合,通過在關鍵的時序路徑上采用低Vth單元和在非關鍵的時序路徑上采用高Vth單元這樣的優(yōu)化手段能夠滿足時序目標。如果芯片供貨商提供了與狀態(tài)相關的泄漏模型,則利用它們可以獲得更好的泄漏結果。

根據設計團隊所采用的方法或選擇,可以將one-pass或two-pass的綜合流程應用于多閾值設計。初次綜合可采用低Vth、高性能庫來執(zhí)行,隨后采用多Vth庫來進行增量編譯,以降低泄漏電流。對于時序和泄漏均十分重要的設計,可同時采用多Vth庫來執(zhí)行one-pass綜合。這種設計首先對時序進行了優(yōu)化,然后在不影響已實現的時序效果(即worst negative slack,WNS)的條件下,再對泄漏功率進行優(yōu)化。功率優(yōu)化后,再進行面積優(yōu)化。不論是采用one-pass流程,還是two-pass流程對泄漏功率進行優(yōu)化,在綜合環(huán)境(使用Power Compiler搭配Design Compiler或Physical Compiler)中都推薦采用多Vth庫。

流程的實現要依靠合理的泄漏約束,此約束在Power Compiler中由set_max_leakage_power命令指定。

綜合中的功率優(yōu)化

綜合工具能夠通過采用如RTL級門控時鐘插入和門級功率優(yōu)化等技術來優(yōu)化功率設計。這些技術由Power Compiler結合Design Compiler和(或)Physical Compiler共同實現。

當無需觸發(fā)器的輸出信號時,RTL級門控時鐘能夠將通向大型寄存器組的時鐘信號關斷。圖6所示為沒有門控時鐘和帶有門控時鐘的 設計編輯的同步負載使能電路的比較。Power Compiler能夠自動插入門控時鐘電路,將圖6a中的反饋網和多路轉換器替代為圖6b中的鎖存器和插入到寄存器時鐘網的雙輸入門電路。

由于門控電路取代了多路器,因而這種類型的門控時鐘對面積的影響相對不大,而且,實際上還能將面積縮減5~15%。Power Compiler能夠自動實現這種門控電路,而且不需要改變RTL代碼。

Power Compiler還能采用庫中的ICG來替換手動插入的門控時鐘。這項功能能夠支持那些在物理流程中擁有手動門控時鐘的傳統模塊或IP。Power Compiler能夠識別ICG中與功率相關的屬性,從而有助于此類單元的布局。對于門控時鐘的高級用戶,Power Compiler能夠通過實現多級門控時鐘,來節(jié)省更多的功率。在這項技術中,一個門控時鐘單元代替寄存器組,作為另一個門控時鐘單元的饋入。

RTL級門控時鐘能

夠以多種方式節(jié)省功率:由于時鐘信號不必持續(xù)饋入寄存器組,因而內部功耗降低;由于時鐘網絡中的電容值減小,因而開關功耗降低;由于下游邏輯電路并未改變,因而功耗還能夠進一步降低。

在Power Compiler與Physical Compiler協同工作時,門控時鐘單元的布局得到了優(yōu)化。在Physical Compiler流程中,Power Compiler確保門電路單元能夠就近放置在一起,門控電路部件與其所驅動的部件也能靠近放置,這樣的布局減少了其它方式中門控時鐘可能出現的時鐘扭曲。

除非加入特定的可測性設計,否則門控時鐘會導致芯片的可測性下降。由于時鐘信號是由內部信號進行控制,所以測試工程師無法控制可測性設計掃描觸發(fā)器的負載。這個問題可以通過在測試編輯過程中增加一個測試引腳,并將其指定為一個固定值(1'b1)來加以避免。添加了控制點的門控時鐘電路如圖8所示。

Power Compiler的set_clock_gating_style指令的選項能夠在門控時鐘中指定所添加的具易測性的邏輯電路的數量和類型,以此改善芯片的可測試性。例如,可在門控時鐘鎖存器前后添加一個用于測試的控制點,并且選擇test_mode或scan_enable模式,還可通過其它選項增加可觀察性邏輯或者增加建立時間和保持時間裕量。若要使用Design Compiler的check_tes指令或check_dft指令,則要先使用hookup_testports和set_test_hold 1 Test_Mode指令。

門控時鐘不應在具有由Design Compiler實現的主/從觸發(fā)器的變量(或信號)的設計中使用。Design Compiler采用clocked_on_also信號類型屬性來實現這些觸發(fā)器。但在門控時鐘發(fā)生的抽象層面上,Power Compiler不能識別出這項屬性,而只能將觸發(fā)器的從時鐘信號進行門控。可以使用set_clock_gating_signals指令,將特定的由主從型觸發(fā)器實現的設計變量(或信號)排除在外:

dc_shell> set_clock_gating_signals -design TOP -exclude

{ A B }

總之,最佳的代碼編制是由以下四種方式中的任意一種實現的基本同步負載使能,這些實現方式可以混用,也可以相互嵌套。

"If-Else"語句

條件賦值

"Case"語句

"For"循環(huán)

&nb sp; 除了RTL級優(yōu)化外,Power Compiler還采用下列門級優(yōu)化技術(按優(yōu)先次序排列),同時對功率、時序和面積進行優(yōu)化:

尺寸選擇(sizing);

優(yōu)化技術(technology mapping) ;

引腳交換(pin swapping) ;

因子分解(factoring);

緩沖器插入(buffer insertion);

相位分配(phase assignment)

這些優(yōu)化要求采用具有功率特性的庫。由于Power Compiler自動保持時序,并在設計人員的約束下維持設計的面積

,因此,這項工具實現了門級的“一鍵式”(push-button)功率節(jié)省。

高水平功率管理范例

為了表明SOC中高水平功率管理的潛力,Synopsys公司與ARM、NS和Artisan公司共同合作,制造了一款用于驗證大幅節(jié)省功耗效果的測試芯片。此芯片采用專門的硬件和軟件,以控制不同芯片域內的電壓和時鐘頻率,并對本文上述的電壓和頻率按比例縮放技術應用了高層次控制。

控制組件包括了ARM公司的Intelligent Energy Manager軟件,此軟件用于平衡處理器的工作負載和能量消耗。而NS公司所提供的PowerWise硬件監(jiān)控性能以及與電壓調節(jié)器的通信,其目的是在每一種工作頻率下,將供電電壓按比例縮小至最低的工作電平。這套系統能夠對由于制造工藝所產生的硅芯片性能差別以及由于溫度波動所造成的運行時間性能變化進行補償。

這款240MHz的芯片分為三個主要的電源域:可縮放電壓的CPU電源、存儲器電源域和供芯片其它部分使用的標準固定電壓域。這些相互獨立的電源域能夠對CPU和RAM進行精確的電壓控制和電流測量。標準單元和電平轉換器的工作范圍是0.7~1.32V。

針對大量應用高速緩存的工作負載,對處理工作負載的功耗和精確時間均進行了測量,并對僅使用動態(tài)頻率按比例縮放的效果和同時使用動態(tài)電壓和頻率按比例縮放的效果進行了比較。圖8總結了標準化至1.2V工作電壓下的結果。圖中表明功率節(jié)省僅是在芯片的動態(tài)電壓和頻率按比例縮放子系統中。通常在這樣的SoC中,有些芯片無法進行電壓按比例縮放,如外部存儲器等部件通常只能工作在固定的電壓下,因此設計分區(qū)和規(guī)劃時必須考慮到系統級的功率節(jié)省。

與只有頻率按比例縮放相比,電壓和頻率均按比例縮放可以顯著降低能量消耗。例如,在120MHz下運行時,能夠削減一半的功耗要求,但如果同時對供電電壓進行按比例縮放,就能將功耗削減80%。

結語

通過將各種功率管理技術相結合,能夠使芯片功耗大幅降低,就像由Synopsys、ARM、NS和Aritisan等公司的測試芯片所獲得的那樣。典型的SoC設計可能不需要用到所有這些技術,但是主流的解決方案已經存在,可以滿足全部的設計要求。

設計人員應根據詳盡的功率分析和對可用工具功能的充分了解,選擇正確的解決方案。在設計流程中應盡早分析功率要求,以避免發(fā)生與功率相關的錯誤。因為層次較高的技術能夠最大程度地節(jié)省功率,所以早期分析還有益于功率目標的實現。