【摘 要】 在簡要介紹了PC/AT鍵碼、旋轉(zhuǎn)開關(guān)和EPM7128結(jié)構(gòu)特點的基礎(chǔ)上,介紹了利用FPGA" title="FPGA">FPGA實現(xiàn)旋轉(zhuǎn)開關(guān)信號到PC/AT鍵碼轉(zhuǎn)換的設(shè)計方法。

關(guān)鍵詞:接口" title="接口">接口電路,F(xiàn)PGA,鍵碼

在專用電路設(shè)計中,為了方便操作與控制,要對電路設(shè)計提出各種具體要求。本文即為一設(shè)計實例,其設(shè)計要求為:在旋轉(zhuǎn)開關(guān)的控制下,產(chǎn)生所需的PC/AT鍵碼控制信號,即當旋轉(zhuǎn)開關(guān)左轉(zhuǎn)時,每轉(zhuǎn)動一個位置,產(chǎn)生一個左箭頭鍵碼和斷開碼(E0、6B、E0、F0、6B)信號,控制光標左移一個位置;旋轉(zhuǎn)開關(guān)右轉(zhuǎn)時,每轉(zhuǎn)動一個位置,產(chǎn)生一個右箭頭鍵碼和斷開碼(E0、74、E0、F0、74)信號,控制光標右移一個位置;當按下一次旋轉(zhuǎn)開關(guān)的接通按鍵時,產(chǎn)生一個回車鍵碼和斷開碼(50、F0、50)信號,控制光標換行。為了實現(xiàn)這一設(shè)計要求,設(shè)計中采用Altera公司生產(chǎn)的可編程邏輯芯片EPM7128SLC,利用Maxplus2軟件完成設(shè)計任務(wù)。

1 基本概念

1.1 旋轉(zhuǎn)開關(guān)簡介

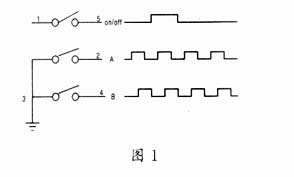

旋轉(zhuǎn)開關(guān)由A、B兩個通道開關(guān)、一個按壓通斷開關(guān)構(gòu)成,當左右旋轉(zhuǎn)時,A、B通道分別輸出具有90度相位差的控制信號;當按下通斷開關(guān)時,輸出一個通斷控制信號。旋轉(zhuǎn)開關(guān)的構(gòu)成及輸出波形如圖1所示。

1.2 PC/AT鍵碼特點

PC/AT鍵碼由接通碼與斷開碼構(gòu)成,當鍵按下時,產(chǎn)生相應(yīng)的PC/AT鍵碼,當鍵釋放后,產(chǎn)生對應(yīng)的斷開碼,不同的按鍵對應(yīng)不同的鍵碼和斷開碼,如左箭頭的鍵碼為E0、6B,斷開碼E0、F0、6B;右箭頭的鍵碼為E0、74,斷開碼E0、F0、74;回車鍵的鍵碼為50,斷開碼為F0、50。每發(fā)送一個鍵碼包含11個數(shù)據(jù)位,即1個起始位、8個數(shù)據(jù)位(低位在前,高位在后)、1個奇偶校驗位、1個停止位;在鍵碼傳送的同時,還傳送一個與鍵碼同步的時鐘信號,用于同步鍵碼數(shù)據(jù)的接收;鍵碼中每個數(shù)據(jù)位的傳送發(fā)生在鍵碼時鐘的下降沿,時鐘的波特率為16Kbps左右。

|

1.3 EPM7128簡介

EPM7128是Altera公司生產(chǎn)的建立在多陣列結(jié)構(gòu)基礎(chǔ)上的高性能可編程邏輯器件,其內(nèi)部具有符合IEEE1149.1標準的JTAG接口用于在線下載和修改程序,其內(nèi)部具有2500個可使用門陣列、128個宏單元、8個邏輯陣列塊,EPM7128SLC84具有68個用戶可使用I/O接口。

2 軟件設(shè)計

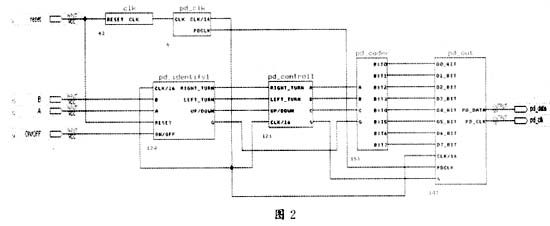

為了利用FPGA將旋轉(zhuǎn)開關(guān)信號轉(zhuǎn)換成PC/AT鍵碼信號,所設(shè)計的FPGA軟件由時鐘發(fā)生器模塊(clk)、時鐘編碼模塊(pd_clk)、旋轉(zhuǎn)開關(guān)狀態(tài)識別模塊(pd identify)、輸出數(shù)據(jù)編碼控制模塊(pd_control)、碼器模塊(pd coder)、輸出模塊(pd out)構(gòu)成,其功能連接如圖2所示

|

時鐘發(fā)生器模塊的功能為:在reset信號的控制下,產(chǎn)生頻率為15.5kHz的時鐘信號,其振蕩源為由5個非門構(gòu)成的串聯(lián)環(huán)路,該振蕩器產(chǎn)生的振蕩信號經(jīng)分頻電路分頻,獲得所需頻率的振蕩信號clk。

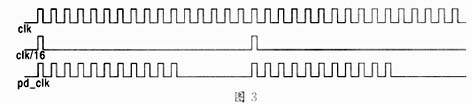

時鐘編碼模塊的功能有兩個,一是產(chǎn)生其它功能模塊所需的基準控制信號clk/16;二是產(chǎn)生所需的PC/AT時鐘信號pd clk,如圖3所示。

旋轉(zhuǎn)開關(guān)狀態(tài)識別模塊的功能是正確地識別旋轉(zhuǎn)開關(guān)的狀態(tài),并產(chǎn)生相應(yīng)的控制信號;如果旋轉(zhuǎn)開關(guān)向左旋轉(zhuǎn)一個位置,則輸出一個Left turn識別信號;如果旋轉(zhuǎn)開關(guān)向右旋轉(zhuǎn)一個位置,則輸出一個識別信號;如果按壓一次旋轉(zhuǎn)開關(guān)上的接通開關(guān),則輸出一個Up/Down識別信號。

輸出編碼控制模塊和編碼器模塊的功能是在旋轉(zhuǎn)開關(guān)識別信號的控制下,產(chǎn)生相應(yīng)的輸出編碼控制信號,控制編碼器,使編碼器產(chǎn)生相應(yīng)的編碼信號;如果輸入一個Left turn識別信號,則依次輸出E0、6B、E0、F0、6B五個編碼信號;如果輸入一個 識別信號,則依次輸出E0、74、E0、F0、 74五個編碼信號;如果輸入一個Up/Down識別信號,則依次輸出50、F0、50三個編碼信號。

輸出模塊的功能是:根據(jù)輸入的編碼信號,確定校驗位的值,如編碼信號中有奇數(shù)個1,則校驗位為0,否則為1;根據(jù)輸入的編碼信號與生成的校驗位,產(chǎn)生符合PC/AT鍵碼格式要求的鍵碼信號。

|

|

3 仿真結(jié)果

按照設(shè)計要求,利用Maxplus2軟件進行功能設(shè)計與仿真,在完成模塊功能設(shè)計與各功能模塊仿真之后,進行整體功能模塊連接與仿真,整體模塊連接如圖2所示,功能仿真結(jié)果如圖4所示。其中,reset信號為復位信號,A、B、ON/OFF信號為來自旋轉(zhuǎn)開關(guān)的輸出信號,所設(shè)計的

FPGA輸出的PC/AT鍵碼時鐘與數(shù)據(jù)信號分別為pd_clk和pd_data。

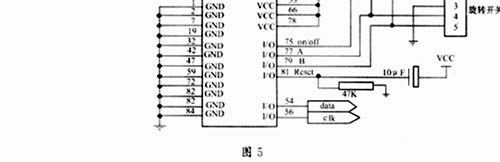

4 硬件結(jié)構(gòu)

所設(shè)計的FPGA程序,通過JTAG口與旋轉(zhuǎn)開關(guān)相連接的輸入接口、用于輸出PC/AT鍵碼和時鐘的輸出端口。

|

5 結(jié)束語

所設(shè)計的FPGA芯片可通過計算機鍵盤口進行測試,當左、右轉(zhuǎn)動旋轉(zhuǎn)開關(guān)時,控制顯示器上的光標隨之左、右移動;當按壓旋轉(zhuǎn)開關(guān)上的通斷按鍵時,控制顯示器上的光標換行。所設(shè)計的FPGA芯片已被實際工程項目應(yīng)用,實現(xiàn)了設(shè)計目的,滿足了要求。