前言

伴隨著工藝技術(shù)水平的提高,當(dāng)前ASIC設(shè)計(jì)規(guī)模和設(shè)計(jì)復(fù)雜度也不斷的提高。合理的選擇驗(yàn)證工具在ASIC設(shè)計(jì)過程中起了關(guān)鍵作用。下面就結(jié)合實(shí)際的項(xiàng)目開發(fā),對(duì)比驗(yàn)證工具的特點(diǎn),幫助大家更好的認(rèn)識(shí)驗(yàn)證工具。

SystemC 介紹

SystemC是一個(gè)開發(fā)硬件的面向?qū)ο蟮男滦徒7椒ǎ⒃贑++基礎(chǔ)上,是為了方便系統(tǒng)級(jí)設(shè)計(jì)和IP交換。System C是一個(gè)開放的標(biāo)準(zhǔn),由13家EDA和電子行業(yè)的公司共同控制。

包括

ARM Ltd.;Cadence Design Systems, Inc.;CoWare;Fujitsu;Mentor Graphics;Motorola;NECSynopsys

System C的源碼可以從http://www.systemc.org/網(wǎng)站上免費(fèi)下載。SystemC是由一些C++的類庫

組成。用System C開發(fā)的硬件模型可以用標(biāo)準(zhǔn)的C++編譯器來編譯:

Unix/Solaris: bcc,gcc

Windows: MSVC

經(jīng)編譯后形成一個(gè)可執(zhí)行的應(yīng)用程序,設(shè)計(jì)人員可以通過console來觀察系統(tǒng)的行為,驗(yàn)證系統(tǒng)功能和結(jié)構(gòu).

Specman E介紹

Specman Elite是Cadence公司的驗(yàn)證技術(shù)工具,它能提供可配置、可再使用和可擴(kuò)展的驗(yàn)證組件。能夠產(chǎn)生足夠多的測(cè)試激勵(lì)訊號(hào),并能對(duì)設(shè)計(jì)行為與預(yù)期結(jié)果進(jìn)行檢查確認(rèn)。

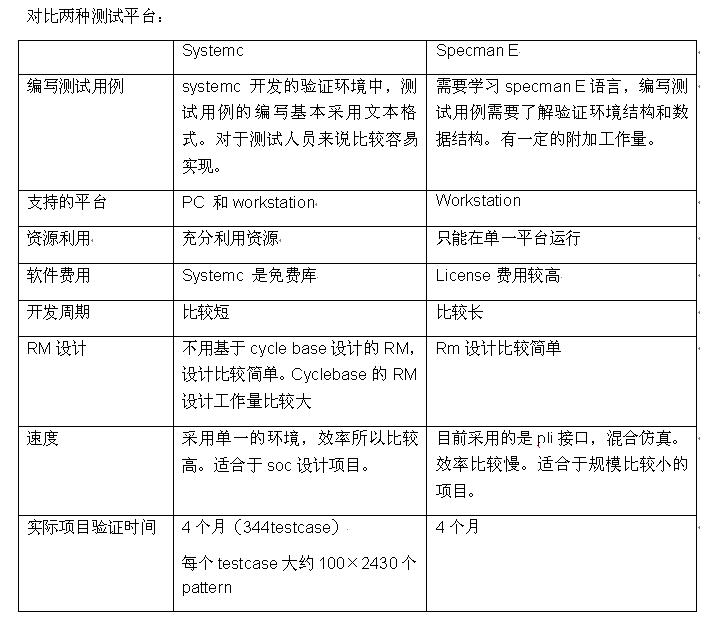

1. EOS 系統(tǒng)的驗(yàn)證

測(cè)試EOS 系統(tǒng)采用SystemC,比較以往的以verilog,specman E,vera語言要有以下特點(diǎn), 不用付高額的eda tool 費(fèi)用;可以充分的利用個(gè)人電腦系統(tǒng)資源;實(shí)際的開發(fā)周期大大縮短。

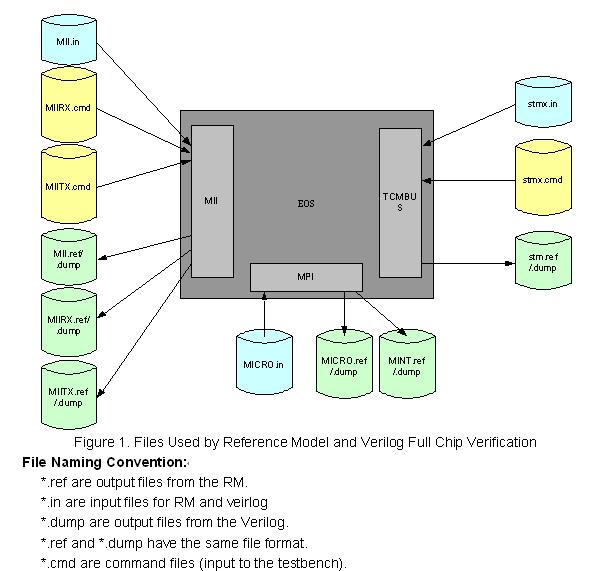

下面是EOS驗(yàn)證系統(tǒng)的設(shè)計(jì)框圖。

mii: Mii Interface

MPI: Microprocessor Interface

TCM: TCMBUS Interface

RM設(shè)計(jì)和測(cè)試用例設(shè)計(jì)基于pc的c++環(huán)境開發(fā),所有的測(cè)試用例產(chǎn)生的輸入輸出結(jié)果存為文件。Verilog代碼根據(jù)輸入文件產(chǎn)生激勵(lì),根據(jù)端口的輸出產(chǎn)生輸出文件(*.dump)。結(jié)果的檢查是通過比較所有的RM輸出的文件(*.REF)和verilog輸出的文件(*.DUMP)。

RM設(shè)計(jì)思路,基于數(shù)據(jù)流設(shè)計(jì),大大減少了具體硬件實(shí)現(xiàn)上的細(xì)節(jié),提高了RM設(shè)計(jì)效率。

這個(gè)基于RM(reference model)設(shè)計(jì)的方法,在項(xiàng)目前期驗(yàn)證設(shè)計(jì)系統(tǒng)結(jié)構(gòu)設(shè)計(jì)是否合理;后面驗(yàn)證可以繼承項(xiàng)目前期系統(tǒng)結(jié)構(gòu)設(shè)計(jì)階段的成果。同時(shí)基于硬件資源環(huán)境4 workstations 和13 PC。由于PC資源充足,把測(cè)試用例的設(shè)計(jì)和RM測(cè)試在PC上進(jìn)行設(shè)計(jì)。由于verilog的開發(fā)在workstation環(huán)境下,并且資源緊張,是項(xiàng)目開發(fā)進(jìn)度的瓶頸,所以選擇verilog速度最優(yōu)的驗(yàn)證途經(jīng)。

基于specmanE實(shí)現(xiàn)測(cè)試SDH系統(tǒng)軟件

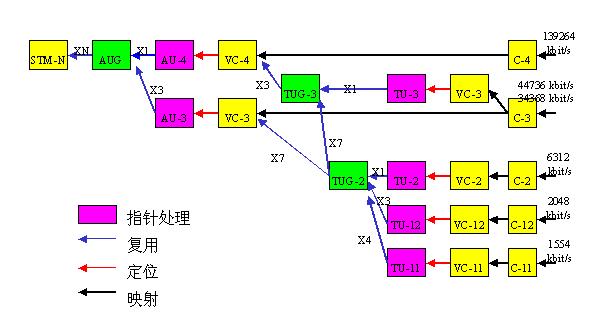

CPXXX支持的SDH業(yè)務(wù)基本復(fù)用結(jié)構(gòu)如下:

根據(jù)數(shù)據(jù)結(jié)構(gòu)特點(diǎn)和E語言特點(diǎn),創(chuàng)建了STM4、STM1、AUG1、AU4、AU3、VC4、TUG3、TUG2、TU3、TU2、TU12、TU11、VC3、VC2、VC12、VC11、C4、C3、C2、C12和C11基本數(shù)據(jù)結(jié)構(gòu)。實(shí)際的測(cè)試數(shù)據(jù)是通過擴(kuò)展基本數(shù)據(jù)結(jié)構(gòu)的方法配置SDH數(shù)據(jù)生成幀。可以配置數(shù)據(jù)結(jié)構(gòu)包括STM4、STM1、AUG1、AU4、AU3、VC4、TUG3、TUG2、TU3、TU2、TU12、TU11、VC3、VC2、VC12、VC11、C4、C3、C2、C12、C11。配置方法的實(shí)質(zhì)是對(duì)各種數(shù)據(jù)結(jié)構(gòu)生成的初始化函數(shù)進(jìn)行個(gè)性化擴(kuò)展。

這種基于E語言的驗(yàn)證設(shè)計(jì)環(huán)境,可以和verilog聯(lián)合仿真。但是仿真速度比較慢,單一的verilog仿真速度的1/4~1/3,在驗(yàn)證工作量比較大的項(xiàng)目中,這是個(gè)瓶頸。所以在實(shí)際的驗(yàn)證中,我們的策略是盡可能的把復(fù)雜的模塊進(jìn)行詳細(xì)的模塊級(jí)驗(yàn)證。因?yàn)槊總€(gè)模塊功能特性不一樣,這樣就需要維護(hù)的驗(yàn)證環(huán)境比較多。

結(jié)論

1. 對(duì)于驗(yàn)證工具的選擇,要結(jié)合資源(包括機(jī)器,人力和費(fèi)用)和實(shí)際項(xiàng)目的特點(diǎn),選擇合理的有效的驗(yàn)證工具搭建驗(yàn)證環(huán)境。

2. 對(duì)于驗(yàn)證設(shè)計(jì)工具,不要有排斥或者崇拜的情緒,要結(jié)合實(shí)際的應(yīng)用,搭建能發(fā)揮各自特點(diǎn)的環(huán)境是一個(gè)項(xiàng)目管理的要求。

參考:

1.《Writing Testbench:Functional Verification of HDL models》,Janick Bergeron, Qualis design corporation.

2.《E Reference》 Verisity Design, Inc.

作者簡(jiǎn)介: 陳思軍,project manager , Chiphomer Technology Limited.