引言

隨著深亞微米工藝技術(shù)日益成熟,集成電路芯片的規(guī)模越來越大。數(shù)字IC從基于時(shí)序驅(qū)動(dòng)的設(shè)計(jì)方法,發(fā)展到基于IP復(fù)用的設(shè)計(jì)方法,并在SOC設(shè)計(jì)中得到了廣泛應(yīng)用。在基于IP復(fù)用的SoC設(shè)計(jì)中,片上總線設(shè)計(jì)是最關(guān)鍵的問題。為此,業(yè)界出現(xiàn)了很多片上總線標(biāo)準(zhǔn)。其中,由ARM公司推出的AMBA片上總線受到了廣大IP開發(fā)商和SoC系統(tǒng)集成者的青睞,已成為一種流行的工業(yè)標(biāo)準(zhǔn)片上結(jié)構(gòu)。AMBA規(guī)范主要包括了AHB(Advanced High performance Bus)系統(tǒng)總線和APB(Advanced Peripheral Bus)外圍總線。

AMBA片上總線

AMBA 2.0規(guī)范包括四個(gè)部分:AHB、ASB、APB和Test Methodology。AHB的相互連接采用了傳統(tǒng)的帶有主模塊和從模塊的共享總線

,接口與互連功能分離,這對(duì)芯片上模塊之間的互連具有重要意義。AMBA已不僅是一種總線,更是一種帶有接口模塊的互連體系。下面將簡(jiǎn)要介紹比較重要的AHB和APB總線。

AHB簡(jiǎn)介

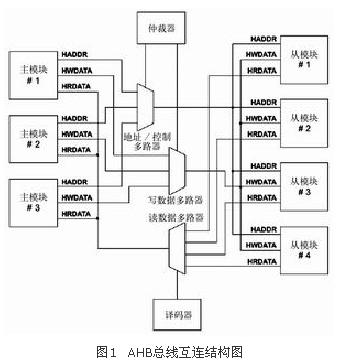

AHB主要用于高性能模塊(如CPU、DMA和DSP等)之間的連接,作為SoC的片上系統(tǒng)總線,它包括以下一些特性:?jiǎn)蝹€(gè)時(shí)鐘邊沿操作;非三態(tài)的實(shí)現(xiàn)方式;支持突發(fā)傳輸;支持分段傳輸;支持多個(gè)主控制器;可配置32位~128位總線寬度;支持字節(jié)、半字節(jié)和字的傳輸。AHB 系統(tǒng)由主模塊、從模塊和基礎(chǔ)結(jié)構(gòu)(Infrastructure)3部分組成,整個(gè)AHB總線上的傳輸都由主模塊發(fā)出,由從模塊負(fù)責(zé)回應(yīng)。基礎(chǔ)結(jié)構(gòu)則由仲裁器(arbiter)、主模塊到從模塊的多路器、從模塊到主模塊的多路器、譯碼器(decoder)、虛擬從模塊(dummy Slave)、虛擬主模塊(dummy Master)所組成。其互連結(jié)構(gòu)如圖1所示。

APB簡(jiǎn)介

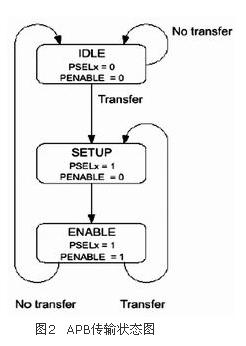

APB主要用于低帶寬的周邊外設(shè)之間的連接,例如UART、1284等,它的總線架構(gòu)不像AHB支持多個(gè)主模塊,在APB里面唯一的主模塊就是APB 橋。其特性包括:兩個(gè)時(shí)鐘周期傳輸;無需等待周期和回應(yīng)信號(hào);控制邏輯簡(jiǎn)單,只有四個(gè)控制信號(hào)。APB上的傳輸可以用如圖2所示的狀態(tài)圖來說明。

1)系統(tǒng)初始化為IDLE狀態(tài),此時(shí)沒有傳輸操作,也沒有選中任何從模塊。

2)當(dāng)有傳輸要進(jìn)行時(shí),PSELx=1,PENABLE=0,系統(tǒng)進(jìn)入SETUP狀態(tài),并只會(huì)在SETUP 狀態(tài)停留一個(gè)周期。當(dāng)PCLK的下一個(gè)上升沿時(shí)到來時(shí),系統(tǒng)進(jìn)入ENABLE 狀態(tài)。

3)系統(tǒng)進(jìn)入ENABLE狀態(tài)時(shí),維持之前在SETUP 狀態(tài)的PADDR、PSEL、PWRITE不變,并將PENABLE置為1。傳輸也只會(huì)在ENABLE狀態(tài)維持一個(gè)周期,在經(jīng)過SETUP與ENABLE狀態(tài)之后就已完成。之后如果沒有傳輸要進(jìn)行,就進(jìn)入IDLE狀態(tài)等待;如果有連續(xù)的傳輸,則進(jìn)入SETUP狀態(tài)。

基于AMBA的片上系統(tǒng)

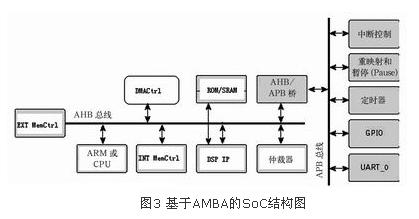

一個(gè)典型的基于AMBA總線的系統(tǒng)框圖如圖3所示。

大多數(shù)掛在總線上的模塊(包括處理器)只是單一屬性的功能模塊:主模塊或者從模塊。主模塊是向從模塊發(fā)出讀寫操作的模塊,如CPU,DSP等;從模塊是接受命令并做出反應(yīng)的模塊,如片上的RAM,AHB/APB 橋等。另外,還有一些模塊同時(shí)具有兩種屬性,例如直接存儲(chǔ)器存取(DMA)在被編程時(shí)是從模塊,但在系統(tǒng)讀傳輸數(shù)據(jù)時(shí)必須是主模塊。如果總線上存在多個(gè)主模塊,就需要仲裁器來決定如何控制各種主模塊對(duì)總線的訪問。雖然仲裁規(guī)范是AMBA總線規(guī)范中的一部分,但具體使用的算法由RTL設(shè)計(jì)工程師決定,其中兩個(gè)最常用的算法是固定優(yōu)先級(jí)算法和循環(huán)制算法。AHB總線上最多可以有16個(gè)主模塊和任意多個(gè)從模塊,如果主模塊數(shù)目大于16,則需再加一層結(jié)構(gòu)(具體參閱ARM公司推出的Multi-layer AHB規(guī)范)。APB 橋既是APB總線上唯一的主模塊,也是AHB系統(tǒng)總線上的從模塊。其主要功能是鎖存來自AHB系統(tǒng)總線的地址、數(shù)據(jù)和控制信號(hào),并提供二級(jí)譯碼以產(chǎn)生APB外圍設(shè)備的選擇信號(hào),從而實(shí)現(xiàn)AHB協(xié)議到APB協(xié)議的轉(zhuǎn)換。

使用DesignWare搭建

基于AMBA的SOC芯片

為了更有效地在有限時(shí)間內(nèi)完成復(fù)雜的系統(tǒng)級(jí)芯片設(shè)計(jì),越來越多的芯片開發(fā)中采用了可重復(fù)使用的IP。為了滿足日益成長(zhǎng)的IP需求,Synopsys提供了一系列已驗(yàn)證的IP,如Synopsys DesignWare,來幫助設(shè)計(jì)者加速系統(tǒng)級(jí)芯片的開發(fā)。

DesginWare里面包含了兩種IP:可實(shí)現(xiàn)

IP(Implement IP)以及VIP(Verification IP)。VIP是為了應(yīng)對(duì)系統(tǒng)級(jí)芯片設(shè)計(jì)帶來的驗(yàn)證挑戰(zhàn)而特別設(shè)計(jì)的,專為簡(jiǎn)化驗(yàn)證流程。可實(shí)現(xiàn)IP是指已通過驗(yàn)證、可物理實(shí)現(xiàn)的IP,分為Star IP、宏單元(Macro Cell)和 foundation IP。宏單元中包含與AMBA總線相關(guān)的IP,有DW_ahb (ARM AMBA2.0 AHB 總線 IP、DW_amba_ictl (ARM AMBA2.0 中斷IP)、DW_apb (ARM AMBA2.0 APB 總線IP)和DW_apb_uart ( ARM AMBA2.0 APB UART )等。

由此,可以借助Synopsys公司提供的AMBA總線IP構(gòu)建SoC,加速系統(tǒng)集成和驗(yàn)證。首先到 Synopsys的FTP或EST下載所需要的宏單元,借助coreConsultant在相應(yīng)的目錄下安裝coreKit并且創(chuàng)建一個(gè)工作環(huán)境.然后設(shè)定此宏單元的可變參數(shù),以符合系統(tǒng)要求,此外還必須設(shè)定綜合相關(guān)的參數(shù)。設(shè)定完參數(shù)后,還要驗(yàn)證所設(shè)定的參數(shù)是否符合系統(tǒng)規(guī)范。初步驗(yàn)證后,便可進(jìn)一步將宏單元綜合成所需的網(wǎng)表。產(chǎn)生網(wǎng)表之后,仍須利用宏單元內(nèi)的驗(yàn)證環(huán)境來確定綜合后網(wǎng)表的所有功能都能正常工作。如果所有功能都驗(yàn)證完成,就可以將這個(gè)IP放置到系統(tǒng)中。用DesignWare搭建的一個(gè)基于AMBA總線結(jié)構(gòu)的SoC系統(tǒng)如圖4所示,其中包括了用于驗(yàn)證AMBA總線協(xié)議的VIP。

結(jié)語

隨著復(fù)雜IP核在目前和下一代ASIC設(shè)計(jì)中的廣泛應(yīng)用,半導(dǎo)體公司開始采用片上總線標(biāo)準(zhǔn)化集成技術(shù)。ARM公司研發(fā)的AMBA總線規(guī)范提供了一種特殊的機(jī)制,可將RISC處理器集成在其他IP核和外設(shè)中。同時(shí),Synopsys提供的DesignWare中的IP可以加速基于AMBA總線結(jié)構(gòu)的SoC芯片設(shè)計(jì)。這種技術(shù)成功地應(yīng)用在TD-SCDMA系統(tǒng)終端基帶數(shù)字芯片的設(shè)計(jì)中,縮短了系統(tǒng)設(shè)計(jì)、IP集成和驗(yàn)證的時(shí)間。