在NiosⅡ系統(tǒng)的構(gòu)建過(guò)程中,SoPC Builder開(kāi)發(fā)環(huán)境集成了許多常用類型的設(shè)備模型,供開(kāi)發(fā)者調(diào)用。在日新月異的嵌入式系統(tǒng)設(shè)計(jì)中開(kāi)發(fā)環(huán)境所集成的接口設(shè)備是非常有限的,有時(shí)無(wú)法滿足開(kāi)發(fā)者的需要,SoPC Builder開(kāi)發(fā)工具允許用戶依據(jù)規(guī)則擴(kuò)展自己的所需設(shè)備,完成系統(tǒng)的設(shè)計(jì)和開(kāi)發(fā),開(kāi)發(fā)者按照Avalon總線規(guī)范將設(shè)備驅(qū)動(dòng)程序集成到SoPC Builder的硬件抽象層(HAL)中,在SoPC Builder環(huán)境下加載使用,方便了用戶開(kāi)發(fā)一個(gè)自定制的片上系統(tǒng)。本文通過(guò)在NiosⅡ嵌入式系統(tǒng)內(nèi)部集成了基于Avalon總線的脈沖寬度調(diào)制(PWM)從外設(shè),介紹了自定制Avalon設(shè)備的過(guò)程。將其應(yīng)用在嵌入式智能小車監(jiān)控系統(tǒng),為采用Nios II處理器的開(kāi)發(fā)者提供了一些方法和建議。

1定制基于Avalon總線的用戶外設(shè)介紹

NiosⅡ的Avalon總線不同于其他微處理器的固定外設(shè),Nios Ⅱ的外設(shè)是可以任意定制的,這使得用戶可以根據(jù)具體的應(yīng)用需求而定制。所有的Nios Ⅱ系統(tǒng)外設(shè)都是通過(guò)Avalon總線與NiosⅡ軟核相連,從而進(jìn)行數(shù)據(jù)交換。因此對(duì)于用戶定義的外設(shè)必須遵從該總線協(xié)議才可與Nios Ⅱ之間建立聯(lián)系。

Avalon信號(hào)接口定義了一組信號(hào)類型片選、讀使能、寫(xiě)使能、地址、數(shù)據(jù)等,用于描述主從外設(shè)上基于地址的讀寫(xiě)接口。外設(shè)使用準(zhǔn)確的信號(hào)與其內(nèi)核邏輯進(jìn)行接口,并刪除會(huì)增加不必要開(kāi)銷的信號(hào)。

在Nios Ⅱ系統(tǒng)中一個(gè)自定義設(shè)備由如下幾部分組成:

(1)硬件文件:用HDL語(yǔ)言編寫(xiě)的描述自定義設(shè)備元件邏輯的硬件描述文件。

(2)軟件文件:用C語(yǔ)言編寫(xiě)的設(shè)備寄存器文件以及設(shè)備的驅(qū)動(dòng)程序文件。

(3)設(shè)備描述文件(Ptf):本文件描述了設(shè)備的結(jié)構(gòu),包含SoPC Builder配置以及將其集成到系統(tǒng)中時(shí)所需要的信息。本文件由SoPC Builder根據(jù)硬件文件以及軟件文件自動(dòng)生成。

2基于NiosⅡ系統(tǒng)的PWM設(shè)計(jì)

PWM是利用數(shù)字輸出來(lái)對(duì)模擬電路進(jìn)行控制的一種非常有效的技術(shù),廣泛應(yīng)用于從測(cè)量、通信到功率控制與變換的許多領(lǐng)域中。實(shí)際上PWM是一種對(duì)模擬信號(hào)電平進(jìn)行數(shù)字編碼的方法,通過(guò)高分辨率計(jì)數(shù)器的使用,方波的占空比被調(diào)制用來(lái)對(duì)一個(gè)具體模擬信號(hào)的電平進(jìn)行編碼。PWM信號(hào)仍然是數(shù)字的,因?yàn)樵诮o定的任何時(shí)刻,滿幅值的直流供電或者完全有,或者完全無(wú)。電壓或電流源是以一種通或斷的重復(fù)脈沖序列被加到模擬負(fù)載上。通即是直流供電被加到負(fù)載上,斷即是供電被斷開(kāi)。只要帶寬足夠,任何模擬值都可以使用PWM進(jìn)行編碼。

2.1硬件設(shè)計(jì)

硬件文件指的是HDL文件,由以下幾個(gè)模塊組成:

邏輯模塊:描述設(shè)備的邏輯功能;

寄存器映射模塊:為內(nèi)部邏輯模塊和Avalon總線提供了通信接口;

Avalon總線接口模塊:使Avalon總線訪問(wèn)寄存器從而完成相應(yīng)的邏輯功能。

2.1.1 邏輯結(jié)構(gòu)

對(duì)于自定義的PWM也是由以上幾部分模塊組成。PWM按照以下要求設(shè)計(jì):

(1)任務(wù)邏輯按一個(gè)簡(jiǎn)單時(shí)鐘進(jìn)行同步操作。

(2)任務(wù)邏輯使用32位計(jì)數(shù)器為PWM提供一個(gè)一定范圍的周期和占空比,最大周期可設(shè)為232個(gè)clk。

(3)可以使用微控制器來(lái)設(shè)置PWM的周期和占空比的值,因此要提供一個(gè)可對(duì)寄存器進(jìn)行讀寫(xiě)的接口和控制邏輯。

(4)定義寄存器來(lái)存儲(chǔ)PWM周期和占空比的值。

(5)微控制器可以通過(guò)控制寄存器的禁止位關(guān)閉PWM輸出。

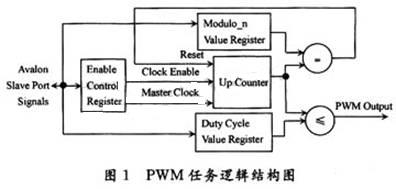

PWM任務(wù)邏輯的結(jié)構(gòu)圖如圖1所示。

PWM任務(wù)邏輯由輸入時(shí)鐘(clock)、輸出信號(hào)端口(pwm_out)、使能位、32位計(jì)數(shù)器以及一個(gè)32位比較電路組成。clk作為32位計(jì)數(shù)器的時(shí)鐘信號(hào),32路比較電路比較32位計(jì)數(shù)器的當(dāng)前值與占空比設(shè)定寄存器(Duty Cycle Value Register)中的值來(lái)決定pwm_out的輸出為高或低。當(dāng)當(dāng)前計(jì)數(shù)器中的值小于或等于占空比寄存器中的值時(shí),pwm_out輸出低電平,否則輸出高電平。PWM周期設(shè)定寄存器(Modulo_n ValueRegister)用來(lái)設(shè)置pwm_out的信號(hào)周期,當(dāng)當(dāng)前計(jì)數(shù)器的值等于周期設(shè)定寄存器中的設(shè)定時(shí),產(chǎn)生一個(gè)復(fù)位信號(hào)來(lái)清除計(jì)數(shù)器中的值。使能控制寄存器(EnableControl Register)能使時(shí)鐘信號(hào)有效或無(wú)效,即控制計(jì)數(shù)器是否計(jì)數(shù),從而保持pwm_out輸出保持當(dāng)前不變。

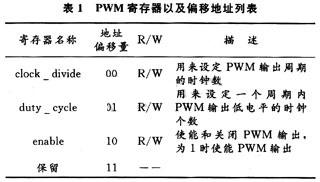

PWM內(nèi)部包括使能控制寄存器(Enable ControlRegister)、周期設(shè)定寄存器(Modulo_n Value Register)以及占空比設(shè)定寄存器(Duty Cycle Value Register),如圖1所示。設(shè)計(jì)中將各寄存器映射成Avalon從端口地址空間內(nèi)一個(gè)單獨(dú)的偏移地址。每個(gè)寄存器都能進(jìn)行讀/寫(xiě)訪問(wèn),軟件可以讀回寄存器中的當(dāng)前值。表1是PWM寄存器以及偏移地址列表。

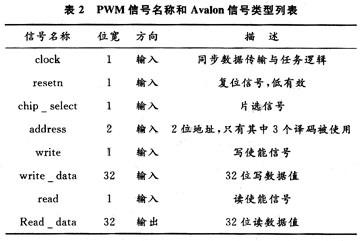

PWM的Avalon接口需要一個(gè)簡(jiǎn)單的從端口,該端口使用Avalon總線信號(hào)完成寄存器的讀/寫(xiě)傳輸。PWM與Avalon總線接口所需的信號(hào)如表2所示。

2.1.2 硬件設(shè)計(jì)文件與仿真

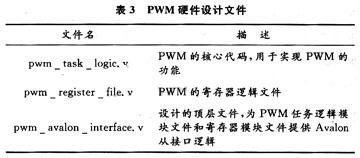

PWM硬件設(shè)計(jì)文件包含表3所示的三個(gè)Verilog編寫(xiě)的HDL文件。

pwm_tasK_logic.v完成PWM的邏輯功能,圖2是此文件在QuartusⅡ環(huán)境下的仿真波形。

圖2中:clock_divide信號(hào)設(shè)定PWM輸出周期的時(shí)鐘數(shù),dutv_cycle信號(hào)設(shè)定一個(gè)周期內(nèi)PWM輸出低電平的時(shí)鐘個(gè)數(shù),兩個(gè)信號(hào)設(shè)定值決定PWM信號(hào)的占空比和周期。

2.2軟件設(shè)計(jì)

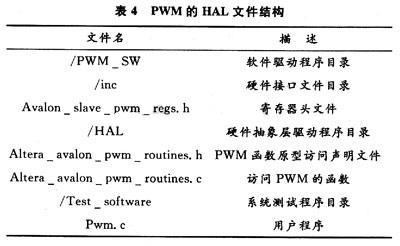

如果要使Nios軟核能夠訪問(wèn)自定義的設(shè)備,就必須根據(jù)先前的硬件設(shè)計(jì)按照硬件提取層的文件結(jié)構(gòu)編寫(xiě)設(shè)備驅(qū)動(dòng)程序。以PWM為例說(shuō)明HAL的文件結(jié)構(gòu),如表4所示。

2.3 將PWM設(shè)計(jì)封裝為SoPC Builder元件

當(dāng)硬件文件和軟件文件都已建立好后,便可以通過(guò)SoPC Builder中帶有的設(shè)備編輯器將自定義設(shè)備封裝到開(kāi)發(fā)環(huán)境內(nèi)部,在構(gòu)建NiosⅡ系統(tǒng)時(shí)可以對(duì)其直接調(diào)用。在SoPC Builder中單擊Creat New Component,創(chuàng)建新元件向?qū)砑親DL文件、設(shè)置信號(hào)和接口添加軟件,最終生成包含描述文件、用戶存放硬件描述文件的文件夾以及用來(lái)包含HAL軟件文件的HAL文件夾。

2.4 構(gòu)建Nios系統(tǒng)

構(gòu)建好的內(nèi)核文件在QuartusⅡ中編譯,生成pof配置文件下載到E2PROM芯片中,接下來(lái)就可以使用Nios IDE開(kāi)發(fā)環(huán)境編輯用戶程序,以及通過(guò)JTAGBlaster或者USB Blaster在目標(biāo)板上對(duì)應(yīng)用程序進(jìn)行調(diào)試。

3 自定制外設(shè)PWM在嵌入式智能小車監(jiān)控系統(tǒng)中的應(yīng)用

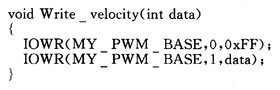

智能小車監(jiān)控系統(tǒng)設(shè)計(jì)應(yīng)用周立功公司SmartSoPC核心板,F(xiàn)PGA為Altera公司的EPlC12,NiosⅡ處理器作為嵌入式CPU,機(jī)器人車電機(jī)共有兩個(gè),左輪電機(jī)和右輪電機(jī)。該部分包括電機(jī)驅(qū)動(dòng)電路和電機(jī)控制電路,即左電機(jī)的驅(qū)動(dòng)與控制以及右電機(jī)的驅(qū)動(dòng)與控制。驅(qū)動(dòng)電路采用CTMicroelectronics公司的大功率直流電機(jī)驅(qū)動(dòng)芯片L289,調(diào)速控制采用PWM來(lái)控制汽車的前進(jìn)速度,由FPGA寫(xiě)入控制字,可得到不同占空比的PWM驅(qū)動(dòng)信號(hào),此PWM信號(hào)送人電機(jī)驅(qū)動(dòng)芯片的控制端來(lái)調(diào)節(jié)速度。調(diào)用電機(jī)驅(qū)動(dòng)程序,改變PWM占空比,輸出PWM波,實(shí)現(xiàn)電機(jī)的速度控制。用PWM信號(hào)控制直流電動(dòng)機(jī)速度,頻率較低時(shí),電動(dòng)機(jī)不會(huì)穩(wěn)定運(yùn)轉(zhuǎn),頻率較高時(shí),PWM信號(hào)的驅(qū)動(dòng)效率降低。經(jīng)過(guò)多次實(shí)際電路的測(cè)試,調(diào)試結(jié)果顯示當(dāng)頻率在500~1 000 Hz時(shí),效果較好。部分C語(yǔ)言控制代碼如下:

4結(jié) 語(yǔ)

NiosⅡ嵌入式處理器是用戶可配制的通用RISC嵌入式處理器,是一個(gè)非常靈活和強(qiáng)大的處理器。基于此種技術(shù)的嵌入式系統(tǒng)設(shè)計(jì)可以方便地將一般設(shè)備和自定義設(shè)備模塊集成到系統(tǒng)中,豐富了接口資源,從而能使用戶快速地開(kāi)發(fā)一個(gè)自定制片上系統(tǒng),提高了效率,縮短了開(kāi)發(fā)周期。本文通過(guò)自定制PWM外圍設(shè)備的方法,并通過(guò)硬件測(cè)試證明了方案的可行性和正確性,希望能夠?yàn)椴捎肗ios Ⅱ處理器的開(kāi)發(fā)人員提供一些方法和建議。