摘? 要: 介紹了基于PCI專用芯片S5933和DSP芯片TMS320C32的圖像處理" title="圖像處理">圖像處理平臺(tái)的硬件設(shè)計(jì)。該平臺(tái)使用專用視頻輸入處理芯片SAA7113和CPLD實(shí)現(xiàn)了高速連續(xù)的視頻幀采集,滿足了后繼圖像處理的需要。該平臺(tái)既可以作為視頻圖像采集使用,也可以進(jìn)行視頻壓縮、匹配等圖像處理的算法驗(yàn)證,并具有使用靈活的特點(diǎn)。

關(guān)鍵詞: 數(shù)字信號(hào)處理芯片? 視頻采集? 圖像處理

?

隨著計(jì)算機(jī)、多媒體和數(shù)據(jù)通信技術(shù)的高速發(fā)展,數(shù)字圖像技術(shù)近年來(lái)得到了極大的重視和長(zhǎng)足的發(fā)展,并在科學(xué)研究、工業(yè)生產(chǎn)、醫(yī)療衛(wèi)生、教育、娛樂(lè)、管理和通信等方面取得了廣泛的應(yīng)用。同時(shí),人們對(duì)計(jì)算機(jī)視頻應(yīng)用的要求也越來(lái)越高,從而使得高速、便捷、智能化的高性能數(shù)字圖像處理設(shè)備成為未來(lái)視頻設(shè)備的發(fā)展方向,這必然要求產(chǎn)生相適應(yīng)的新理論、新方法和新算法。為了在利用這些新技術(shù)的過(guò)程中檢驗(yàn)其可行性,研制了基于PCI總線和DSP芯片的圖像處理平臺(tái),該圖像處理平臺(tái)是利用PHILIPS公司的視頻輸入處理器SAA7113、TI公司的TMS320C32高速浮點(diǎn)DSP和AMCC公司的S5933 PCI總線接口芯片搭建的。利用高速的PCI總線和功能強(qiáng)大的DSP芯片,可以進(jìn)行視頻壓縮、圖像檢測(cè)、視覺(jué)定位等算法研究。

1 系統(tǒng)功能概述

根據(jù)實(shí)際應(yīng)用需要,該系統(tǒng)的主要功能有:

(1)可以在不同輸入制式PAL和NTSC之間進(jìn)行自動(dòng)切換和處理。

(2)能利用采集到的YUV圖像信號(hào)數(shù)據(jù)進(jìn)行壓縮算法的驗(yàn)證,或轉(zhuǎn)換成灰度圖像數(shù)據(jù)" title="圖像數(shù)據(jù)">圖像數(shù)據(jù)、RGB格式圖像數(shù)據(jù)等進(jìn)行檢測(cè)、定位等算法的檢驗(yàn)。

(3)能將處理后的數(shù)據(jù)通過(guò)PCI接口交給上層系統(tǒng)(PC機(jī))保存或進(jìn)行進(jìn)一步驗(yàn)證處理。???

(4)系統(tǒng)具有軟件修改、升級(jí)功能和靈活性,便于算法的改進(jìn)驗(yàn)證。

系統(tǒng)的設(shè)計(jì)難點(diǎn)主要是如何實(shí)現(xiàn)系統(tǒng)數(shù)據(jù)的高速傳輸。圖像數(shù)據(jù)由專用集成視頻解碼器SAA7113采集,經(jīng)A/D轉(zhuǎn)換處理后傳輸?shù)紻SP;再經(jīng)DSP處理后通過(guò)PCI接口傳輸?shù)絇C機(jī)。如何實(shí)現(xiàn)SAA7113與DSP之間和DSP與S5933之間的高效率數(shù)據(jù)通信是解決這個(gè)問(wèn)題的關(guān)鍵。通過(guò)分析研究,在SAA7113與DSP之間采用CPLD控制的兩幀輪換方式,實(shí)現(xiàn)圖像的隔行信號(hào)變逐行信號(hào)以及采集和處理的同步進(jìn)行;在DSP與S5933之間采用DMA傳輸方式" title="傳輸方式">傳輸方式,實(shí)現(xiàn)數(shù)據(jù)流在系統(tǒng)中的高速傳輸,以滿足圖像處理要求。

2 系統(tǒng)的硬件設(shè)計(jì)

整個(gè)系統(tǒng)由視頻解碼器、DSP和PCI總線專用芯片組成。系統(tǒng)框圖如圖1所示。

?

DSP芯片采用TMS320C32,該芯片是在TMS320C30的基礎(chǔ)上簡(jiǎn)化而來(lái)的,含有TMS320C30 CPU核心。它增加了一些常用的功能部件,使程序引導(dǎo)功能、串行接口傳輸和存儲(chǔ)器均可支持8、16、32位的數(shù)據(jù)。它可產(chǎn)生邊沿中斷和電平中斷,可由用戶編程設(shè)定中斷向量表的地址,具有空等待和低功耗兩種電源管理方式。它具有兩個(gè)DMA通道,功能強(qiáng)大的外部存儲(chǔ)器接口既可以滿足視頻解碼接口8位數(shù)據(jù)的要求,也可以實(shí)現(xiàn)PCI接口32位數(shù)據(jù)的的高速數(shù)據(jù)傳輸。TMS320C32靈活的程序加載可以實(shí)現(xiàn)在系統(tǒng)編程。

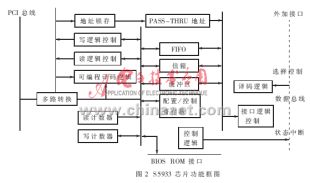

PCI總線專用接口芯片采用S5933,它是一種功能強(qiáng)且使用靈活的PCI總線控制器專用芯片,該芯片符合PCI局部總線規(guī)范2.1版本,既可作為PCI總線目標(biāo)設(shè)備,實(shí)現(xiàn)基本的傳送要求;也可作為PCI總線主控設(shè)備,訪問(wèn)其它PCI總線設(shè)備。S5933的峰值傳送速率為132Mbps(32位PCI數(shù)據(jù)線)。S5933提供了3個(gè)物理總線接口:PCI總線接口、外加總線接口(ADD-ON BUS);可選的NV存儲(chǔ)器接口。用戶可根據(jù)需要設(shè)計(jì)S5933與外加總線接口相連接的邏輯電路和配置空間的初始化,而不必考慮PCI總線規(guī)范眾多的協(xié)議,從而將復(fù)雜的PCI總線接口關(guān)系轉(zhuǎn)化為簡(jiǎn)單的8/16/32位外加總線(ADD-ON BUS)接口關(guān)系。S5933芯片功能框圖如圖2所示。

?

PCI總線與外加總線之間的數(shù)據(jù)傳輸可以通過(guò)內(nèi)部先入先出存儲(chǔ)器(FIFO)、郵箱寄存器(Mailbox)和數(shù)據(jù)直傳通道(Pass-Thru)三種通道進(jìn)行。各通道都包括兩組寄存器以分別完成PCI總線和ADD-ON總線接口雙向數(shù)據(jù)傳輸,為使用者提供較為寬松而靈活的設(shè)計(jì)空間。

可編程視頻解碼芯片采用SAA7113,該芯片是可編程視頻處理芯片,采用CMOS工藝。通過(guò)簡(jiǎn)單的I2C總線可以對(duì)其實(shí)現(xiàn)編程控制;內(nèi)部包含兩路模擬處理通道,能實(shí)現(xiàn)視頻源的選擇、抗混疊(去假頻)濾波、模/數(shù)變換、自動(dòng)嵌位、自動(dòng)增益控制、時(shí)鐘產(chǎn)生、多制式(PAL BGHI、PAL M、PAL N、NTSC M和NTSC N)解碼及亮度、對(duì)比度和飽和度控制。

????本系統(tǒng)采用軟件模擬I2C總線的控制方式,通過(guò)DSP的多功能口實(shí)現(xiàn)DSP對(duì)SAA7113的初始化等控制;根據(jù)SAA7113輸出的同步脈沖,通過(guò)使用可編程器件CPLD,產(chǎn)生圖像幀存儲(chǔ)器的地址信號(hào)、讀寫(xiě)信號(hào)以及幀切換等控制信號(hào)" title="控制信號(hào)">控制信號(hào),實(shí)現(xiàn)SAA7113和DSP之間的高速數(shù)據(jù)通訊。

3 DSP與SAA7113之間的無(wú)縫連接

SAA7113輸出的是隔行視頻信號(hào),一幀圖像需要傳送兩次,分別記為奇場(chǎng)圖像和偶場(chǎng)圖像;視頻處理的對(duì)象是逐行排列的圖像信號(hào),因此必須等待一幀圖像(連續(xù)的奇、偶兩場(chǎng)信號(hào))采集完后,合成到一個(gè)圖像幀中才能進(jìn)行后續(xù)處理。利用SAA7113的同步信號(hào),使用可編程邏輯器件CPLD構(gòu)建控制器,可將圖像數(shù)據(jù)寫(xiě)入幀存儲(chǔ)器,解決圖像幀合成問(wèn)題。為了向前端處理器(DSP)提供連續(xù)的圖像信號(hào),采用兩個(gè)圖像幀存儲(chǔ)器A和B交替存儲(chǔ)的方式,來(lái)暫存采集到的圖像數(shù)據(jù)和需要處理的圖像數(shù)據(jù),可實(shí)現(xiàn)圖像的實(shí)時(shí)連續(xù)采集處理。

DSP與SAA7113之間的硬件接口如圖3所示,整個(gè)接口的控制邏輯,包括兩個(gè)子模塊:幀圖像寫(xiě)入控制器和乒乓開(kāi)關(guān),由一塊CPLD來(lái)完成。CPLD芯片采用ALTERA公司的EPM9320RC208。兩組幀存儲(chǔ)器A和B采用CYPRESS公司生產(chǎn)的兩塊CY7C1049芯片,容量為512K×8bit,存取時(shí)間不超過(guò)15ns,能滿足圖像實(shí)時(shí)采集要求。

?

SAA7113由數(shù)字視頻輸出口VPO[7:0?]輸出視頻數(shù)據(jù)。系統(tǒng)設(shè)置SAA7113的輸出數(shù)據(jù)為標(biāo)準(zhǔn)的ITU 656 4:2:2 YUV格式,每一個(gè)象素的數(shù)據(jù)由兩個(gè)連續(xù)的字節(jié)表示。為了方便地存儲(chǔ)處理圖像,系統(tǒng)僅取一幀圖像中間的512×512個(gè)象素作為一幀,即所取圖像幀為連續(xù)奇偶兩場(chǎng)圖像的中央512行,且每行取中間的512個(gè)象素的圖像塊。

利用SAA7113的同步信號(hào),幀圖像寫(xiě)入控制器模塊產(chǎn)生幀存儲(chǔ)器的地址信號(hào)、寫(xiě)信號(hào)以及幀切換信號(hào)之一(RDY1)。SAA7113輸出的同步信號(hào)包括LLC、RTS0、RTS1。LLC是行鎖定系統(tǒng)時(shí)鐘輸出,為象素時(shí)鐘頻率的兩倍,即27MHz,用來(lái)同步數(shù)據(jù)采集,使得一個(gè)LLC周期輸出一個(gè)字節(jié)的圖像數(shù)據(jù)。在圖像數(shù)據(jù)有效時(shí),其上升沿" title="上升沿">上升沿反相后作為幀存儲(chǔ)器的WE#信號(hào)。RTS0、RTS1的功能是通過(guò)編程設(shè)置SAA7113功能寄存器確定的。RTS0被設(shè)置為水平輸出參考信號(hào)(行有效信號(hào)),RTS0高電平時(shí)表示采集一行有效象素,低電平時(shí)表示場(chǎng)消隱信號(hào),在RTSO上升沿后,幀圖像寫(xiě)入控制器控制采集一行中間的512個(gè)象素?cái)?shù)據(jù),將其余的象素?cái)?shù)據(jù)丟棄。RTS1被設(shè)置為垂直輸出參考信號(hào)和奇偶場(chǎng)信號(hào),RTS1高電平時(shí)表示采集奇場(chǎng)圖像所需要的有效數(shù)據(jù),在RTS1上升沿時(shí),開(kāi)始采集奇場(chǎng)圖像數(shù)據(jù),同時(shí)它也被用來(lái)作為幀圖像開(kāi)始的信號(hào);RTS1低電平時(shí)表示采集偶場(chǎng)中所需要的圖像數(shù)據(jù),在RTS1下降沿時(shí),開(kāi)始采集偶場(chǎng)圖像數(shù)據(jù)。在RTS1上升沿時(shí),幀圖像寫(xiě)入控制器控制采集256行象素?cái)?shù)據(jù)作為奇場(chǎng)圖像;在RTS1下降沿時(shí),順次采集下面的256行象素?cái)?shù)據(jù)作為偶場(chǎng)圖像,其余的圖像行數(shù)據(jù)丟棄。使用512K×8bit的靜態(tài)存儲(chǔ)器(SRAM),恰好可以存放一幀512×512×2×8bit的圖像。在合成一幀圖像時(shí),對(duì)應(yīng)的奇場(chǎng)圖像的第n個(gè)象素和偶場(chǎng)圖像的第n個(gè)象素在存儲(chǔ)器內(nèi)位置相差512×2×8bit,幀圖像寫(xiě)入控制器通過(guò)把RTS1(奇偶場(chǎng)有效)信號(hào)作為寫(xiě)入圖像數(shù)據(jù)的幀存儲(chǔ)器地址信號(hào)中的A1[11],把場(chǎng)中有效行的計(jì)數(shù)輸出信號(hào)作為幀存儲(chǔ)器地址信號(hào)中的A1[18:12],把行中有效象素的計(jì)數(shù)輸出信號(hào)作為幀存儲(chǔ)器地址信號(hào)中的A1[10:0],從而實(shí)現(xiàn)隔行信號(hào)變逐行信號(hào)存儲(chǔ)在一圖像幀存儲(chǔ)器中。圖4為圖像采集同步信號(hào)時(shí)序圖。當(dāng)采集完一幀圖像數(shù)據(jù)時(shí),幀圖像寫(xiě)入控制器產(chǎn)生RDY1信號(hào),通知乒乓開(kāi)關(guān)。

?

在CPLD內(nèi)部構(gòu)造一個(gè)乒乓開(kāi)關(guān)控制模塊,自動(dòng)完成幀間讀寫(xiě)兩個(gè)通道接口的切換。其中幀圖像寫(xiě)入控制器產(chǎn)生的寫(xiě)圖像幀的地址信號(hào)A1[18:0]、寫(xiě)控制信號(hào)WR#和SAA7113的VPO[7:0]組成了圖像幀寫(xiě)通道的始端接口;DSP讀圖像幀的地址線信號(hào)A2[18:0]、讀控制信號(hào)R/W#和數(shù)據(jù)線的低8位信號(hào)DI[7:0]組成了圖像幀讀通道的終端接口;RDY1、RDY2(FX0)作為幀切換就緒信號(hào)觸發(fā)通道的切換。開(kāi)始采集圖像數(shù)據(jù)時(shí),幀切換就緒信號(hào)RDY1、RDY2同時(shí)為假,圖像幀寫(xiě)通道的始端接口信號(hào)與圖像幀A的接口信號(hào)RD、WE#、A[18:0]和D[7:0]連接;SAA7113的當(dāng)前幀圖像數(shù)據(jù)寫(xiě)入幀存儲(chǔ)器A;同時(shí),圖像幀讀通道的終端接口與圖像幀B的接口信號(hào)連接,DSP從幀B中取出前一幀圖像數(shù)據(jù)進(jìn)行處理;當(dāng)前幀的圖像數(shù)據(jù)采集完時(shí),幀圖像寫(xiě)入控制器停止采集數(shù)據(jù),置RDY1為真;同理,當(dāng)DSP在處理完前一幀圖像時(shí),設(shè)置引腳FXO置RDY2為真。乒乓開(kāi)關(guān)模塊在檢測(cè)到RDY1、RDY2同時(shí)為真時(shí),切換通道的接口,此時(shí)圖像幀寫(xiě)通道的始端接口與圖像幀B的接口連接;SAA7113的當(dāng)前幀圖像數(shù)據(jù)寫(xiě)入幀存儲(chǔ)器B;圖像幀讀通道的終端接口與圖像幀存儲(chǔ)器A的接口信號(hào)連接,DSP從幀存儲(chǔ)器A中取出前一幀圖像數(shù)據(jù)進(jìn)行處理。這樣兩幀輪換進(jìn)行,實(shí)現(xiàn)了圖像的實(shí)時(shí)連續(xù)處理。

在DSP和SAA7113之間所有控制信號(hào)的接口邏輯和時(shí)序轉(zhuǎn)換都由CPLD來(lái)完成,增加了可靠性,簡(jiǎn)化了PCB的版面,并且可以編程修改,提高了使用的靈活性。

4 S5933與DSP之間的接口設(shè)計(jì)

S5933的三種數(shù)據(jù)傳輸方式有不同的特點(diǎn),應(yīng)用于不同的場(chǎng)合。

S5933信箱方式不支持猝發(fā)(Burst)傳輸,由8個(gè)32位信箱寄存器組成,可從兩個(gè)方向進(jìn)行訪問(wèn)。它們平均分為兩類,分別用于PCI接口和ADD-ON接口之間的雙向信息傳輸。主機(jī)和擴(kuò)展邏輯都可以通過(guò)查詢或中斷方式獲悉任一信箱寄存器的任一字節(jié)的空滿狀態(tài),并通過(guò)相應(yīng)地址訪問(wèn)該字節(jié)。S5933的信箱寄存器映射在DSP的I/O空間中,從而可以實(shí)現(xiàn)DSP對(duì)信箱的直接操作,數(shù)據(jù)速率較低,故系統(tǒng)中只使用這種方式傳輸命令和狀態(tài)信息,例如PC機(jī)通知DSP設(shè)備關(guān)閉;DSP通知上層已經(jīng)傳送完數(shù)據(jù)(處理完的數(shù)據(jù)的大小不是固定的)等。

S5933的FIFO方式主要由兩個(gè)接口共用的兩個(gè)32×8比特的FIFO、讀或?qū)懙刂芳拇嫫饕约白x或?qū)懹?jì)數(shù)器組成。兩個(gè)FIFO分別作為PCI和ADD-ON接口之間的雙向緩沖區(qū)。S5933提供了快捷方式:一組專門(mén)用于FIFO方式傳輸?shù)目刂萍盃顟B(tài)信號(hào),包括FIFO寄存器的直接讀、寫(xiě)以及狀態(tài)信號(hào)等,用以提高數(shù)據(jù)傳輸速度,但此信號(hào)組只能工作在S5933為主控設(shè)備的情況下。S5933作為目標(biāo)設(shè)備時(shí),內(nèi)部FIFO只是作為一般的寄存器,PCI總線如同訪問(wèn)信箱寄存器那樣訪問(wèn)它們,操作比較直觀,但不支持猝發(fā)傳輸,極大地限制了傳輸速度;S5933作為主控設(shè)備時(shí),FIFO方式可進(jìn)行DMA方式的猝發(fā)傳輸,S5933可以通過(guò)FIFO接口啟動(dòng)DMA傳輸周期,傳輸過(guò)程不需要CPU的干預(yù),傳輸?shù)乃俾逝c外部設(shè)備的數(shù)據(jù)傳輸速率有關(guān),可以得到很高的數(shù)據(jù)傳輸速率。S5933的DMA數(shù)據(jù)傳輸啟動(dòng)方式有兩種:PCI總線接口啟動(dòng)和ADD-ON總線接口啟動(dòng)。啟動(dòng)方式?jīng)Q定于由哪個(gè)接口設(shè)置讀或?qū)懙刂芳拇嫫饕约白x或?qū)懹?jì)數(shù)器:PCI總線接口啟動(dòng)方式是由PCI總線主設(shè)備(一般是PC機(jī)的客戶程序)設(shè)置DMA相關(guān)寄存器發(fā)起DMA傳輸?shù)?ADD-ON總線接口啟動(dòng)方式是由外部邏輯電路(一般是外部插卡上的CPU)設(shè)置DMA相關(guān)寄存器發(fā)起DMA傳輸?shù)摹?/FONT>

S5933的PASS-THRU方式使主機(jī)以內(nèi)存映射方式訪問(wèn)ADD-ON接口的存儲(chǔ)空間,只能工作在S5933是目標(biāo)設(shè)備的情況下,且外部接口需要邏輯電路的支持,故不常用。

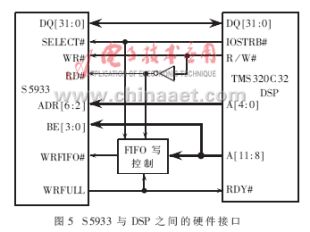

本系統(tǒng)是圖像處理的一個(gè)實(shí)驗(yàn)平臺(tái),既要求數(shù)據(jù)傳輸率高,又要求有一定的升級(jí)功能和靈活性。因此,系統(tǒng)采用FIFO數(shù)據(jù)傳輸方式。當(dāng)采集的圖像數(shù)據(jù)量大且要求傳輸速度高時(shí),可以采用FIFO方式中的PCI總線接口啟動(dòng)DMA方式,使用DMA傳輸;有一些應(yīng)用場(chǎng)合,要傳送的數(shù)據(jù)個(gè)數(shù)不明確,例如圖像壓縮后的數(shù)據(jù)量是不一定的,可以使用外加總線接口啟動(dòng)DMA的傳輸方式傳送壓縮圖像,而用信箱方式傳送命令和圖像狀態(tài)信息。在這種方式下,S5933的外加總線操作寄存器全部映射在TMS320C32 DSP的選通控制信號(hào)IOSTRB#控制的空間中,使DSP對(duì)PCI接口傳輸?shù)臄?shù)據(jù)的控制十分簡(jiǎn)單,就象操作自身的外圍接口一樣。S5933與DSP之間的硬件接口的具體連接方式如圖5所示。

?

S5933和DSP之間的硬件連接,就是利用DSP的讀寫(xiě)信號(hào)R/W#、地址選通控制信號(hào)IOSTRB#、外部設(shè)備就緒信號(hào)RDY#和部分地址信號(hào)以及S5933的FIFO狀態(tài)信號(hào)WRFULL進(jìn)行簡(jiǎn)單的時(shí)序和邏輯組合,生成對(duì)S5933的外加總線接口的讀寫(xiě)控制信號(hào):WR#、RD#、SELECT#、ADR[6:2]、BE[3:0]、WRFIFO#。S5933的數(shù)據(jù)總線與DSP的數(shù)據(jù)總線相連接,數(shù)據(jù)線寬度為32位,以便提供盡可能高的傳輸速率。

本文采用PCI接口芯片S5933、DSP芯片TMS320C32和視頻輸入處理芯片SAA7113設(shè)計(jì)實(shí)現(xiàn)的視頻圖像處理實(shí)驗(yàn)平臺(tái)系統(tǒng)可以實(shí)現(xiàn)圖像的高速連續(xù)采集,進(jìn)行圖像壓縮、圖像處理等算法的驗(yàn)證,達(dá)到了系統(tǒng)設(shè)計(jì)的目標(biāo)。本系統(tǒng)具有使用靈活、升級(jí)方便等特點(diǎn)。考慮到DSP芯片的內(nèi)部RAM有限,程序不能完全在片內(nèi)運(yùn)行,在進(jìn)行一些復(fù)雜的圖像處理運(yùn)算時(shí),速度會(huì)受到限制,故本系統(tǒng)僅適用于靜態(tài)圖像的處理算法研究。

?

參考文獻(xiàn)

1 陳利學(xué).微機(jī)總線與接口設(shè)計(jì).成都]電子科技大學(xué)出版社,1998.6

2 TMS320第三代數(shù)字信號(hào)處理器用戶指南.北京]北京聞亭科技發(fā)展有限公司,1998

3 TMS320C3X Users’ Guide.TI Inc,2001

4 S5933 32-bit PCI MatchMaker Data Sheet.AMCC,1998

5 SAA7113 9-bit Video Input Processor Data Sheet. Philips Semiconductors, 1999