摘? 要: 介紹了針對3/3相雙繞組感應(yīng)發(fā)電機(jī)" title="感應(yīng)發(fā)電機(jī)">感應(yīng)發(fā)電機(jī)設(shè)計(jì)的勵磁" title="勵磁">勵磁系統(tǒng),該系統(tǒng)由DSP和FPGA構(gòu)成。給出了控制系統(tǒng)" title="控制系統(tǒng)">控制系統(tǒng)的接口電路和實(shí)驗(yàn)結(jié)果。

關(guān)鍵詞: DSP? FPGA? 3/3相雙繞組感應(yīng)發(fā)電機(jī)

?

1 系統(tǒng)簡介

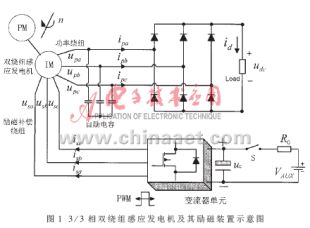

3/3相雙繞組感應(yīng)發(fā)電機(jī)帶有兩個繞組:勵磁補(bǔ)償繞組和功率繞組,如圖1所示。勵磁補(bǔ)償繞組上接一個電力電子變換裝置,用來提供感應(yīng)發(fā)電機(jī)需要的無功功率,使功率繞組上輸出一個穩(wěn)定的直流電壓。

?

圖1中各參數(shù)的含義如下:

isa, isb, isc——補(bǔ)償繞組中的勵磁電流;

usa, usb, usc——補(bǔ)償繞組相電壓;

ipa, ipb, ipc——功率繞組電流;

upa, upb, upc——功率繞組相電壓;

udc——二極管整流橋直流側(cè)輸出電壓;

????uc——變流器直流側(cè)電容電壓。

電力電子變換裝置由功率器件" title="功率器件">功率器件及其驅(qū)動電路和控制電路兩部分組成。功率器件選用三菱公司的智能功率模塊(IPM)PM75CSA120(75A/1200V),驅(qū)動電路使用光耦HCPL4502。控制電路由DSP+FPGA構(gòu)成。

2 EPM7128與TMS320C32同外設(shè)之間的接口電路

圖2所示為控制電路的接口電路。控制電路使用的DSP是TMS320C32,它是TI公司生產(chǎn)的第三代高性能的CMOS 32位數(shù)字信號處理器,其憑借強(qiáng)大的指令系統(tǒng)、高速數(shù)據(jù)處理能力及創(chuàng)新的結(jié)構(gòu),已經(jīng)成為理想的工業(yè)控制用DSP器件。其主要特點(diǎn)是:單周期指令執(zhí)行時間為50ns,具有每秒可執(zhí)行2200萬條指令、進(jìn)行4000萬次浮點(diǎn)運(yùn)算的能力;提供了一個增強(qiáng)的外部存儲器配置接口,具備更加靈活的存儲器管理與數(shù)據(jù)處理方式。控制電路使用的FPGA器件為ALTERA公司的EPM7128,它屬于高密度、高性能的CMOS EPLD器件,與ALTERA公司的MAXPLUS II開發(fā)系統(tǒng)軟件配合,可以100%地模仿高密度的集成有各種邏輯函數(shù)和多種可編程邏輯的TTL器件。采用類似器件作為DSP的專用外圍集成電路(ASIC)更為經(jīng)濟(jì)靈活,可以進(jìn)一步降低控制系統(tǒng)的成本。

?

電壓檢測使用三相變壓器,電流檢測使用HL電流傳感器。電平轉(zhuǎn)換電路用來將檢測到的信號轉(zhuǎn)換為0~5V的電平。A/D" title="A/D">A/D轉(zhuǎn)換器選用ADS7862。保護(hù)電路使用電壓比較器311得到過壓/過流故障信號。

DSP完成以下四項(xiàng)工作:數(shù)據(jù)的采集和處理、控制算法的完成、PWM脈沖值的計(jì)算和保護(hù)中斷的處理。

? FPGA完成以下三項(xiàng)工作:管理DSP和各種外部設(shè)備的接口;脈沖的輸出和死區(qū)的產(chǎn)生;保護(hù)信號的處理。

3 使用FPGA實(shí)現(xiàn)DSP和ADS7862之間的高速接口

ADS7862是TI公司專為電機(jī)和電力系統(tǒng)控制而設(shè)計(jì)的A/D轉(zhuǎn)換器。它的主要特點(diǎn)是:4個全差分輸入接口,可分成兩組,兩個通道可同時轉(zhuǎn)換;12bits并行輸出;每通道的轉(zhuǎn)換速率為500kHz。控制方法為:由A0線的值決定哪兩個通道轉(zhuǎn)換;由Convst線上的脈寬大于250ns的低電平脈沖啟動轉(zhuǎn)換;由CS和RD線的低電平控制數(shù)據(jù)的讀出,連續(xù)兩次讀信號可以得到兩個通道的數(shù)據(jù)。

系統(tǒng)中使用了兩片ADS7862,它們的控制線使用同樣的接口,數(shù)據(jù)線則分別和DSP的高/低16位數(shù)據(jù)線中的低12位相連接。這樣DSP可以同時控制兩片A/D轉(zhuǎn)換器:4通道同時轉(zhuǎn)換;每次讀操作可以得到兩路數(shù)據(jù)。

如圖3所示,將A/D轉(zhuǎn)換器的控制信號映射為DSP的三個外部端口:A0、ADCS(和ADRD使用一個端口)和CONVST。在FPGA中使用邏輯譯碼器對端口譯碼。利用AHDL語言編寫的譯碼程序如下:

TABLE

A[23..12], IS, RW=>A0, ADCS, CONVST, PWM1, PWM2,

PWM3, PWM, PRO, CLEAR;

H″810″,? 0,? 0=>? 0,? 1,? 1,? 1,? 1,? 1,? 1,? 1,? 1;

H″811″,? 0,? 1=> 1,? 0,? 1,? 1,? 1,? 1,? 1,? 1,? 1;

H″812″,? 0,? 0=> 1,? 1,? 0,? 1,? 1,? 1,? 1,? 1,? 1;

H″813″,? 0,? 1=> 1,? 1,? 1,? 0,? 1,? 1,? 1,? 1,? 1;

H″814″,? 0,? 0=>? 1,? 1,? 1,? 1,? 0,? 1,? 1,? 1,? 1;

H″815″,? 0,? 0=>? 1,? 1,? 1,? 1,? 1,? 0,? 1,? 1,? 1;

H″816″,? 0,? 0=>? 1,? 1,? 1,? 1,? 1,? 1,? 0,? 1,? 1;

H″817″,? 0,? 1=>? 1,? 1,? 1,? 1,? 1,? 1,? 1,? 0,? 1;

H″817″,? 0,? 0=>? 1,? 1,? 1, ?1,? 1,? 1,? 1,? 1,? 0;

END TABLE

?

其中,0表示低電平,1表示高電平。RW=1表示讀,RW=0表示寫。

DSP對這三個端口進(jìn)行操作就可以控制A/D轉(zhuǎn)換器:寫CONVST端口可以啟動A/D轉(zhuǎn)換器;讀ADCS端口可以從A/D轉(zhuǎn)換器中讀到數(shù)據(jù);寫數(shù)據(jù)到A0端口可以設(shè)置不同的通道。

使用上述方法可以實(shí)現(xiàn)DSP和A/D轉(zhuǎn)換器之間的無縫快速連接。

4 使用FPGA實(shí)現(xiàn)PWM脈沖的產(chǎn)生和死區(qū)的注入

FPGA除了管理DSP和外設(shè)的接口外,還完成PWM脈沖的產(chǎn)生和死區(qū)的注入。使用參考文獻(xiàn)[1]介紹的方法,將PWM芯片和死區(qū)發(fā)生器集成在FPGA中,就可以使DSP專注于復(fù)雜算法的實(shí)現(xiàn),而將PWM處理交給FPGA系統(tǒng),使系統(tǒng)運(yùn)行于準(zhǔn)并行處理狀態(tài)。

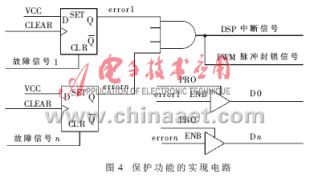

5 使用FPGA實(shí)現(xiàn)系統(tǒng)保護(hù)

為了保護(hù)發(fā)電機(jī)和IGBT功率器件,勵磁控制系統(tǒng)提供了多種保護(hù)功能:變流器直流側(cè)過壓保護(hù);變流器交流電流過流保護(hù);變流器過溫保護(hù);發(fā)電機(jī)輸出過壓保護(hù);IPM錯誤保護(hù)。

使用如圖4所示的硬件邏輯來實(shí)現(xiàn)保護(hù)功能。當(dāng)FPGA檢測到相應(yīng)的故障信號時,D觸發(fā)器輸出一個錯誤信號,使與門輸出一個低電平,此低電平封鎖住所有的PWM脈沖,并觸發(fā)一個DSP的外部中斷信號。當(dāng)DSP響應(yīng)外部中斷時,可以使用PRO端口讀到錯誤的狀態(tài)位。CLEAR端口用來清除D觸發(fā)器,系統(tǒng)因此可以重復(fù)啟動。

?

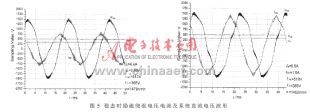

圖5給出了本控制系統(tǒng)的實(shí)驗(yàn)波形圖:變流器的輸出電流基本為正弦;變流器側(cè)電容電壓穩(wěn)定在365V;功率繞組側(cè)輸出電壓穩(wěn)定在510V。

?

?

參考文獻(xiàn)

1 張波濤, 肖 飛. 利用現(xiàn)場復(fù)雜可編程門陣列產(chǎn)生PWM控制脈沖的方法. 電工技術(shù), 2002(1):24~26