1 引言

隨著數(shù)字技術(shù)日益廣泛的應用,以現(xiàn)場可編程門陣列FPGA(Field Programmable Gate Array)[1]為代表的ASIC[2]器件得到了迅速的普及和發(fā)展,器件的集成度和速度都在高速增長。FPGA既具有門陣列的高邏輯密度和高可靠性,又具有可編程邏輯器件的用戶可編程性,可以減少系統(tǒng)的設(shè)計和維護的風險,降低產(chǎn)品成本,縮短設(shè)計周期。

目前,信號處理技術(shù)、通信技術(shù)和多媒體技術(shù)的迅猛發(fā)展都得益于DSP[3]技術(shù)的廣泛應用。但是對于便攜式和家用的語音系統(tǒng)而言,基于一般的DSP芯片的設(shè)計方案并不理想。首先DSP的芯片成本以及開發(fā)成本在現(xiàn)階段仍然是比較高的,尤其是芯片成本,遠遠不及大批量ASIC芯片成本之低。其次便攜式的設(shè)備對體積要求十分苛刻,限制了一部分DSP芯片的使用,而體積正是ASIC芯片的優(yōu)點之一。

本文提出了一種基于FPGA的音頻處理芯片的硬件電路實現(xiàn)方案。由于對FIR濾波器的算法進行了改良,所以很大程度上減小了芯片的體積和降低了芯片的功耗。

2 算法研究與改良

2.1 普通FIR濾波算法

N階FIR濾波器可以用下面的線性卷積表示:[4]

x(n)是輸入的音頻序列,而y(n)是經(jīng)過濾波后輸出的音頻序列,h(k)是N階濾波器的系數(shù)。

簡單的實現(xiàn)這個算法,需要N+1次的乘法和N次的加法。所以至少需要一個硬件乘法器和一個定點或者浮點加法器來實現(xiàn)這個功能。由于音頻處理芯片只需要做線性卷積,所以我們不需要采用乘法器的結(jié)構(gòu)。一般來說,由于乘法器龐大的結(jié)構(gòu),占用了芯片上的大部分面積,消耗用了大部分功率。而不使用乘法器的結(jié)構(gòu)將會節(jié)約可觀的芯片面積和功耗。為了實現(xiàn)這種結(jié)構(gòu),我們需要改良FIR濾波算法。

2.2 改良濾波算法

首先,將濾波的系數(shù)h(k)用二進制表示法(POT,Power of Two)表示:

例如:h(k)=0.1172=2-3-2-7-2-16

我們給出7階濾波器的一組系數(shù),使用POT表示(精度小于10-4):

h(0) = 0.3761 = 2-1-2-3+2-10+2-13-2-15

h(1) = 0.3083 = 2-2+2-4-2-8-2-12

h(2) = -0.9424*10-1 = -2-3+2-5-2-11

h(3) = 0.6439*10-1 = 2-4+2-9-2-14

h(4) = -0.3308*10-1 = -2-5-2-9+2-13

h(5) = 0.1663*10-1 = 2-6+2-10+2-15

h(6) = -0.4135*10-2 = -2-8-2-12+2-16

h(7) = 0.1877*10-2 = 2-9-2-14-2-16

n=7時濾波器的輸出值y如下:

y = (2-1-2-3+2-10+2-13-2-15) * x(7)

+(2-2+2-4-2-8-2-12) * x(6)

+(-2-3+2-5-2-11) * x(5)

+(2-4+2-9-2-14) * x(4)

+(-2-5-2-9+2-13) * x(3)

+(2-6+2-10+2-15) * x(2)

+(-2-8-2-12+2-16) * x(1)

+(2-9-2-14-2-16) * x(0)

很明顯,x(n)的系數(shù)全部都是2的負k次冪,所以我們可以把具有相同系數(shù)的x(n)合并起來。

y(n)=2-1(...2-1(2-1(2-1u1+u2)+u3)+...)+u16)

uj=xj(1)+ xj(2)+……+ xj(rj)

其中1≤j≤16, xj(i)∈{x(n-k)}, 1≤i≤rj

由前面的系數(shù),可以得到:

U1 = x(n-6)-x(n-7); U2 = -x(n)+x(n-5);

U3 = -x(n-3)-x(n-7); U4 = x(n)+x(n-4);

U5 = -x(n-1)-x(n-6); U6 = -x(n-2);

U7 = x(n)+x(n-5); U8 = x(n-3)-x(n-4)+x(n-7);

U5 = -x(n-1)-x(n-6); U10 = 0;

U11 = x(n-5); U12 = x(n-2)-x(n-4);

U13 = x(n-1)+x(n-3); U14 = -x(n)-x(n-2);

U15 = x(n-1); U16 = x(n);

按照這個算法,先求U1的值,然后將結(jié)果右移一位,再將結(jié)果與U2的值相加,依此類推,即可得到y(tǒng)(n)。我們使用若干次加法和16次移位操作即可完成FIR濾波,算法的復雜度和功耗都大大地降低。

3 音頻處理芯片的設(shè)計

3.1 結(jié)構(gòu)概述

在整個音頻處理芯片的結(jié)構(gòu)中,我們沒有采用任何乘法器,取而代之的是一個加法器和移位器。加法器的結(jié)果輸出到移位器,移位器的輸出再反饋到加法器的輸入端,循環(huán)運算實現(xiàn)濾波器的功能。

考慮7階的FIR濾波器,需要對x進行8次采樣,所以輸入的數(shù)據(jù)都應該保存在一個8*16的DataRAM之中(16bit的采樣精度)。系數(shù)RAM(ProgramRAM)的大小取決于操作的個數(shù),在上面提到的算法中,一共有28個操作,所以ProgramRAM的大小不能小于28,在這里我們使用了一個32*6的ProgramRAM,以滿足算法需要。

考慮到音頻處理芯片的可擴展性,我們在音頻處理芯片外設(shè)置一個EEPROM用來存放系數(shù),當芯片啟動的時候,從EEPROM中將數(shù)據(jù)轉(zhuǎn)存到ProgramRAM中,以適應不同F(xiàn)IR濾波器的系數(shù),極大地增強了音頻處理芯片的可編程性。

音頻處理芯片的模塊主要包括EEPROM, ProgramRAM, DataRAM,串并轉(zhuǎn)換模塊,并串轉(zhuǎn)換模塊,地址生成模塊,主控制器模塊。

3.2 尋址方式描述

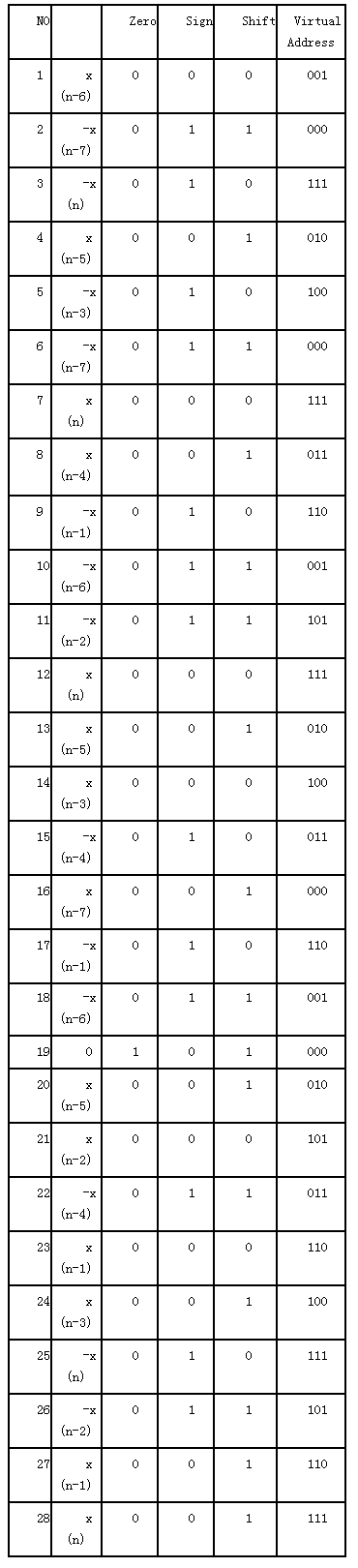

在系統(tǒng)啟動時,附加的EEPROM儲存的系統(tǒng)參數(shù)值,包括輸入信號在DataRAM中的地址值和相應的標志位(32*6bit) ,依次讀入ProgramRAM中去。

其中,Zero,Sign,Shift分別為操作控制

Zero表示不加任何操作數(shù)

Sign表示加上負的操作數(shù)

Shift表示移位操作

而Virtual Address表示操作數(shù)的虛擬地址。

Base Address總是指向DataRAM中最早寫入的值所在的地址,也就是x(n-7)的地址,而Virtual Address其他值相對于x(n-7)的地址,所以可以得出操作數(shù)在DataRAM中實際的地址:

Physical Address="BaseAddress"+VirtualAddress

以y(n)=2-1(...2-1(2-1(2-1u1+u2)+u3)+...)+u16)中的u1為例

U1 = x(n-6) - x(n-7);

參數(shù)設(shè)置:C1= x(n-6)=000001

C2=-x(n-7)=011000

※最低的三位表示存儲地址

※第4位表示移位標志,C2(4)為1表示計算出U1以后要右移得到2-1* U1

※第5位表示符號位,控制加減運算。C1(5)為0表示加, C2(5)為1表示減

※最高位,也就是第6位在Un=0時為1,這里只有C19(6)為1

3.3 端口描述

3.4 模塊設(shè)計

3.4.1 EEPROM [5]

·EEPROM用來存儲系統(tǒng)參數(shù)

·EEPROM是32*6bit的存儲陣列

·EEPROM的輸入是Enable,Address(4 downto 0)

·EEPROM的輸出是CoeffData(5 downto 0)

·EEPROM的首單元存放了操作的個數(shù);例如,首單元存放"011100"表示一共有28個操作。

3.4.2 ProgramRAM [6]

·ProgramRAM接收EEPROM中的系統(tǒng)參數(shù)

·ProgramRAM是32*6bit的存儲陣列

·ProgramRAM的輸入是Write,Read,DataIn(5 downto 0),Address(4 downto 0)

·ProgramRAM的輸出是Zero,Sign,Shift,DataAddr(2 downto 0)

3.4.3串并轉(zhuǎn)換模塊[7] (Serial2Parallel)

·Serial2Parallel接收來自ADC的串行數(shù)據(jù)、數(shù)據(jù)時鐘和幀同步信號

·Serial2Parallel將串行輸入信號轉(zhuǎn)化為16bit的并行信號

·Serial2Parallel的輸入是DataClk,DataIn,F(xiàn)rameSync

·Serial2Parallel的輸出是DataOut(15 downto 0),DataOutSync

3.4.4并串轉(zhuǎn)換輸出模塊[7] (Parallel2Serial)

•Parallel2Serial將并行信號轉(zhuǎn)化為串行信號

•Parallel2Serial的輸入是DataIn(15 downto 0),DataClk,F(xiàn)rameSync

•Parallel2Serial的輸出是DataOut

3.4.5主控制器模塊(Main Controller)

·主控制器模塊是整個設(shè)計的核心,它協(xié)調(diào)控制著其他各個模塊的工作

·主控制器模塊是根據(jù)操作流程圖設(shè)計的一個狀態(tài)機

3.4.6 地址生成模塊(AddressGen)

·PhysicalAddress實際上是一個加法器,將VirtualAddress與BaseAddress相加產(chǎn)生讀地址

·BaseAddress實際上是一個計數(shù)器,IncreaseBase信號控制加1,產(chǎn)生寫地址

·MUX選擇讀地址或者是寫地址到DataRAM

4 音頻處理芯片的仿真

4.1 仿真波形

4.2 仿真結(jié)果

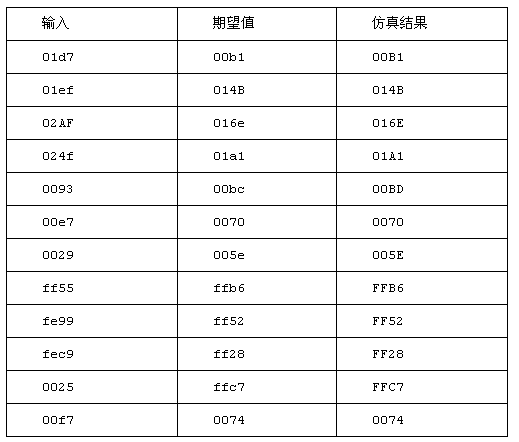

通過程序,對一組輸入序列進行了仿真結(jié)果比較,所獲得的結(jié)果如表1所示。

表1:仿真結(jié)果比較

通過表1可以看出音頻處理芯片達到了預期的設(shè)計目標,效果良好。

可以看到,期望值和仿真結(jié)果在最后一位會有±1的誤差,這是由于我們采用的移位算法將最后一位移出時不進行四舍五入造成的。經(jīng)過計算,這種誤差不會影響FIR的精度。

5 結(jié)束語

本文設(shè)計的音頻處理芯片主要實現(xiàn)FIR濾波器功能,可以滿足較為簡單的語音信號處理的需要。用POT系數(shù)表示方法來表示系統(tǒng)參數(shù),用一個加法器和一個移位寄存器實現(xiàn)乘法器的功能,這樣在面積功耗上就有相當大的優(yōu)勢。設(shè)計過程是采用自頂向下的設(shè)計方法。最終的仿真結(jié)果符合預期的要求。