Linux操作系統(tǒng)的全稱是GNU/Linux,它是由GNU工程和Linux內(nèi)核兩個(gè)部分共同組成的一個(gè)操作系統(tǒng)。該系統(tǒng)中所有組件的源代碼都是自由的,可以有效保護(hù)學(xué)習(xí)成果,因而在嵌入式領(lǐng)域得到了廣泛的應(yīng)用。

FPGA是英文Field Programmable Gate Array的縮寫(xiě),即現(xiàn)場(chǎng)可編程門(mén)陣列,該器件是作為專用集成電路ASIC (Application Specific Integrated Circuit)領(lǐng)域中的一種半定制電路而出現(xiàn)的,它的出現(xiàn)既解決了定制電路的不足,又克服了原有可編程器件門(mén)電路數(shù)有限的缺點(diǎn)。在通信行業(yè)、傳輸網(wǎng)、醫(yī)療儀器、各種電子儀器、安防監(jiān)控、電力系統(tǒng)、汽車(chē)電子以及消費(fèi)類電子中都大面積使用。隨著產(chǎn)品研發(fā)周期的逐步縮短,定制型產(chǎn)品的開(kāi)發(fā)使FPGA在后面的應(yīng)用面越來(lái)越廣。例如在2G和3G通信,以及以后的4G通信和wimax等等通信類設(shè)備中,它與DSP、MPU一起將大量出現(xiàn)在其中。

S3C2410微處理器是一款由Samsung為手持設(shè)備設(shè)計(jì)的低功耗、高度集成的微處理器,采用272腳FBGA封裝,內(nèi)含一個(gè)ARM920T內(nèi)核和一些片內(nèi)外圍設(shè)備。在時(shí)鐘方面,該芯片集成了一個(gè)具有日歷功能的RTC和具有PLL (MPLL和UPLL)的芯片時(shí)鐘發(fā)生器。MPLL產(chǎn)生的主時(shí)鐘能夠使處理器工作頻率最高達(dá)到203MHz。這個(gè)工作頻率能夠使處理器輕松運(yùn)行于Windows CE,Linux等操作系統(tǒng)并進(jìn)行較為復(fù)雜的信息處理。為此,本文以S3C2410上使用Altera公司的EP2S30F67214為例,系統(tǒng)地介紹了在Linux系統(tǒng)環(huán)境下的FPGA的驅(qū)動(dòng)方法。

1 基本原理

Linux下的設(shè)備驅(qū)動(dòng)程序通常是一個(gè)存在于應(yīng)用程序和實(shí)際設(shè)備間的軟件層。許多設(shè)備驅(qū)動(dòng)都是與用戶程序一起發(fā)行的,可以幫助配置和存取目標(biāo)設(shè)備。

在Linux下驅(qū)動(dòng)FPGA,其本質(zhì)上就是字符設(shè)備的驅(qū)動(dòng),慣例上它們位于/dev目錄。

1.1 主次編號(hào)

在內(nèi)核中,dev_t類型(在

建立一個(gè)字符驅(qū)動(dòng)時(shí),需要做的第一件事是獲取一個(gè)或多個(gè)設(shè)備編號(hào)。其必要的函數(shù)是regis-ter_chrdev_region,設(shè)計(jì)時(shí)可在

int register_chrdev_region(dev_t first,unsigned int count,char*name);

如同大部分內(nèi)核函數(shù)一樣,如果分配成功,register_chrdev_region的返回值將是0。出錯(cuò)時(shí),則返回一個(gè)負(fù)的錯(cuò)誤碼,但不能存取請(qǐng)求的區(qū)域。

1.2 重要數(shù)據(jù)結(jié)構(gòu)

注冊(cè)設(shè)備編號(hào)僅僅是驅(qū)動(dòng)代碼必須進(jìn)行的諸多任務(wù)中的第一個(gè)。驅(qū)動(dòng)操作包括三個(gè)重要的內(nèi)核數(shù)據(jù)結(jié)構(gòu),稱為file_operations、file和inode。其中,對(duì)于FPGA驅(qū)動(dòng)來(lái)說(shuō),最值得關(guān)注的是文件操作(file_operations)。

file_operation結(jié)構(gòu)是一個(gè)用字符驅(qū)動(dòng)方式建立設(shè)備編號(hào)和設(shè)備操作的連接結(jié)構(gòu),定義在

第一個(gè)file_operations元素根本不是一個(gè)操作,它是一個(gè)指向擁有這個(gè)結(jié)構(gòu)的模塊指針,或用來(lái)在操作使用時(shí)阻止模塊被卸載,它也是在

llseek主要用于改變文件中的當(dāng)前讀/寫(xiě)位置,同時(shí)可將新位置作為(正的)返回值。其定義如下:

loff_t(*llseek) (struct file*,loff_t,int);

ioctl可為系統(tǒng)調(diào)用提供一個(gè)發(fā)出設(shè)備特定命令的方法。如果設(shè)備不提供ioctl方法,那么,對(duì)于任何未事先定義的請(qǐng)求,系統(tǒng)調(diào)用將返回一個(gè)錯(cuò)誤。定義如下:

int(*ioctl) (struct inode*,struct file*,unsigned int,unsigned long):

1.3 設(shè)備注冊(cè)

內(nèi)核在內(nèi)部將使用struct cdev類型結(jié)構(gòu)來(lái)代表字符設(shè)備。在內(nèi)核調(diào)用設(shè)備操作前,代碼應(yīng)當(dāng)包含

void cdev_init(struct cdev*cdev,structfile_operations*fops);

1.4 open和release

open主要用于提供驅(qū)動(dòng)初始化,在大部分驅(qū)動(dòng)中,open應(yīng)當(dāng)檢查設(shè)備特定的錯(cuò)誤(例如設(shè)備沒(méi)準(zhǔn)備好,或者類似的硬件錯(cuò)誤),但是,其第一步常常是確定打開(kāi)哪個(gè)設(shè)備。open的原代碼為:

int(*open) (struct inode*inode,structfile*flip);

release是open的反操作。

1.5 讀/寫(xiě)操作

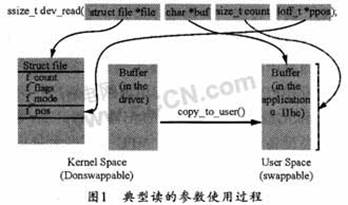

讀和寫(xiě)都是進(jìn)行類似的任務(wù),就是從設(shè)備到應(yīng)用程序代碼的數(shù)據(jù)拷貝。因此,它們的原代碼比較相似:

ssize_t read(struct file*flip,char__user*buff,size_t count,loff_t*offp);

ssize_t write(struct file*filp,const char__user*buff,size_t count,loff_t*offp);

read的任務(wù)是從設(shè)備拷貝數(shù)據(jù)到用戶空間(使用copy_to_user),而write方法則是從用戶空間拷貝數(shù)據(jù)到設(shè)備(使用copy_from_user)。

圖1所示是用read參數(shù)表示一個(gè)典型讀的實(shí)現(xiàn)過(guò)程。

2 硬件電路

通常在大容量存儲(chǔ)項(xiàng)目中,S3C2410處理器一般作為主CPU,可對(duì)EP2S30F67214進(jìn)行擴(kuò)展,以使系統(tǒng)具有拍攝、存儲(chǔ)、下載、I/O口擴(kuò)展的功能。由于FPGA的高速處理能力和易擴(kuò)展性,ARM與FPGA的結(jié)合使用,將在嵌入式系統(tǒng)領(lǐng)域占據(jù)主導(dǎo)地位。

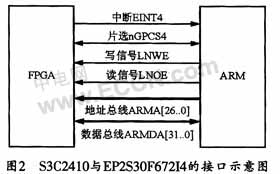

本項(xiàng)目中的ARM主要讀取FPGA的數(shù)據(jù),然后進(jìn)行數(shù)據(jù)處理并送給上位機(jī)。其ARM處理器與FPGA的連接關(guān)系如圖2所示,其主要連接有32位寬數(shù)據(jù)線、27位寬地址線以及讀、寫(xiě)、中斷和片選控制線等。

在S3C2410中,nGPCS4的物理地址為0x2000000—0x28000000,共計(jì)128MB的靜態(tài)物理空間。中斷方式為下降沿有效。

3 編程實(shí)現(xiàn)

3.1 設(shè)備驅(qū)動(dòng)初始化

初始化模塊在內(nèi)核啟動(dòng)時(shí)主要負(fù)責(zé)初始化FPGA工作。其實(shí)現(xiàn)由module_init () 和module_exit ()兩部分組成。其代碼如下:

3.2 異步中斷通知

在應(yīng)用程序中,可用如下代碼獲得中斷響應(yīng):

signal (SIGIO,test_handler);/*test_handler為函數(shù)名字*/

fcntl(fa,F(xiàn)_SETOWN,getpid ());

oflags=fcntl(fa,F(xiàn)_GETFL);/*fd為打開(kāi)設(shè)備返回值*/

fcntl (fd,F(xiàn)_SETFL,oflags∣FASYNC);/*fd為打開(kāi)設(shè)備返回值*/

應(yīng)當(dāng)注意的是,不是所有的設(shè)備都支持異步通知。應(yīng)用程序常常假定異步能力只對(duì)socket和tty可用。

3.3 地址映射

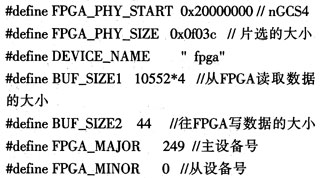

在Linux設(shè)備驅(qū)動(dòng)程序開(kāi)發(fā)過(guò)程中,由于驅(qū)動(dòng)程序操作的都是設(shè)備的虛擬地址,因此,要使驅(qū)動(dòng)程序?qū)μ摂M地址的操作反映到正確的設(shè)備上,還需要通過(guò)內(nèi)存管理單元MMU來(lái)將設(shè)備的虛擬地址映射到正確的物理地址上去,從而保證驅(qū)動(dòng)程序?qū)υO(shè)備的虛擬地址的操作,也就是要對(duì)其相應(yīng)的物理地址進(jìn)行操作。使用內(nèi)存映射的好處是處理大文件時(shí),其速度明顯快于標(biāo)準(zhǔn)文件I/O,這樣無(wú)論讀和寫(xiě),都少了一次用戶空間與內(nèi)核空間之間的復(fù)制。在用戶空間對(duì)FPGA設(shè)備的訪問(wèn)可通過(guò)內(nèi)存映射來(lái)實(shí)現(xiàn)。FPGA可以看作是硬件連接在S3C2410微處理器的片選信號(hào)nGPCS4上的一段物理地址的尋址。因此,必須先把物理地址映射到虛擬地址空間,然后才能對(duì)該段地址進(jìn)行讀/寫(xiě)。通常用戶可用如下代碼關(guān)聯(lián)FPGA的地址:

fpga_base=ioremap(FPGA_PHY_START,F(xiàn)PGA_PHY_SIZE);

4 結(jié)束語(yǔ)

本文系統(tǒng)的介紹了ARM基于Linux平臺(tái)下的FPGA的驅(qū)動(dòng)開(kāi)發(fā)方法,并通過(guò)開(kāi)發(fā)用戶程序,實(shí)現(xiàn)了數(shù)據(jù)的處理和傳輸,從而實(shí)現(xiàn)了FPGA在嵌入式領(lǐng)域的廣泛應(yīng)用。