1 前言

近年來,隨著半導(dǎo)體工藝技術(shù)和設(shè)計方法的迅速發(fā)展,系統(tǒng)級芯片SOC的設(shè)計得以高速發(fā)展,這已成為業(yè)界熱點。但是,由于SOC產(chǎn)品設(shè)計具有開發(fā)周期相對較長、高成本和高風(fēng)險等特點,對市場的變化非常敏感,這使得SOC在消費電子、汽車電子、工業(yè)設(shè)計領(lǐng)域的發(fā)展進(jìn)程仍然緩慢。與此同時,當(dāng)今的制造工藝能夠提供更多更高速的邏輯、更快的1/O和更低價位的新一代可編程邏輯器件,現(xiàn)場可編程門陣列(FPGA)己然進(jìn)入嵌入式應(yīng)用領(lǐng)域,高性能FPGA也不再局限于引進(jìn)系統(tǒng)粘合邏輯,也可作為SOC平臺,而在過去,由于性能緣故,只有專用集成電路(ASIC)或?qū)S脴?biāo)準(zhǔn)產(chǎn)品(ASSP)才能達(dá)到相應(yīng)的要求。不僅如此,由于FPGA的現(xiàn)場可編程特征,它己成為更具靈活性和廣泛性發(fā)展前景的工業(yè)設(shè)計平臺。

FPGA可輕易地被修改變更、修復(fù)缺陷,或在用戶需要升級和配合市場發(fā)展時去創(chuàng)制未來的衍生產(chǎn)品。這一趨勢在工業(yè)無線通信設(shè)計方面更加明顯。當(dāng)考慮到上市時間、實施靈活性及未來過時等問題時,采用FPGA作為專用芯片設(shè)計是一個最佳的項目實施方案。

基于摩爾斯信號的通信是人類最早的無線通信方式,它仍應(yīng)用在海事移動通信、航空移動通信、廣播、衛(wèi)星通信當(dāng)中。由于摩爾斯電碼信號通信的傳統(tǒng)性、經(jīng)濟(jì)性和有效性,它在海事移動通信中仍占主導(dǎo)地位,特別是船與船、船與岸、岸與船之間的摩爾斯通信更是占據(jù)通信業(yè)務(wù)總量的80%以上。

基于PC機(jī)的MORSE電碼信號自動處理己經(jīng)實現(xiàn),但在海事移動通信中,它還是受到一些客觀條件的約束,缺泛方便性和靈活性。本文從基于FPGA平臺的專用芯片設(shè)計技術(shù)入手,分析和設(shè)計了一種摩爾斯電碼的無線通信發(fā)射模塊設(shè)計方案,并對設(shè)計進(jìn)行了仿真驗證。

2 可編程邏輯電路設(shè)計方法

基于可編程邏輯電路的設(shè)計基本方法,一種是傳統(tǒng)的系統(tǒng)硬件電路設(shè)計方法,它是采用自下而上(bottom-up)的設(shè)計方法。另一種就是20世紀(jì)80年代開始興起的EDA(Electronic Design Automation)硬件電路設(shè)計方法。

隨著大規(guī)模專用集成電路的開發(fā)和研制,為了提高開發(fā)效率和增加己有開發(fā)成果的可繼承性,以及縮短開發(fā)時間,各種新興的EDA工具開始出現(xiàn),特別是硬件描述語言HDL(Hardware Description Language)的出現(xiàn),使得傳統(tǒng)的硬件電路設(shè)計方法發(fā)生了巨大的變革,新興的EDA設(shè)計方法采用了自上而下(top-down) 的設(shè)計方法。所謂自上而下的設(shè)計方法就是從系統(tǒng)總體要求出發(fā),自上而下地逐步將設(shè)計內(nèi)容細(xì)化,最后完成系統(tǒng)硬件的整體設(shè)計。利用語言對系統(tǒng)硬件電路的自上而下設(shè)計一般分為三個層次:第一個層次為行為描述,它是對整個系統(tǒng)的數(shù)學(xué)模型的描述;第二層次是寄存器傳輸描述RTL,又稱為數(shù)據(jù)流描述; 第三層是邏輯綜合。

利用邏輯綜合工具,可將RTL方式描述的程序轉(zhuǎn)換成為用基本邏輯元件表示的文件一門級網(wǎng)表,也可將綜合結(jié)果以邏輯原理圖方式輸出,也就是說邏輯綜合結(jié)果相當(dāng)于在人工設(shè)計硬件電路時,根據(jù)系統(tǒng)要求畫出了系統(tǒng)的邏輯電原理圖。再對邏輯綜合結(jié)果在門電路級上進(jìn)行仿真,并檢查定時關(guān)系,如果一切正常,那么系統(tǒng)的硬件設(shè)計基本結(jié)束。自上而下設(shè)計系統(tǒng)硬件的過程如圖一所示。

圖一:自上而下設(shè)計系統(tǒng)硬件的過程

由邏輯綜合工具產(chǎn)生門級網(wǎng)表后,在最終完成硬件設(shè)計時,還可以有兩種選擇:一種是由自動布線程序?qū)⒕W(wǎng)表轉(zhuǎn)換成相應(yīng)的ASIC芯片的制造工藝,定制ASIC芯片;第二種是將網(wǎng)表轉(zhuǎn)換成相應(yīng)的PLD編程碼點,利用PLD器件完成硬件電路的設(shè)計。

3 基于FPGA的摩爾斯碼功能結(jié)構(gòu)設(shè)計

摩爾斯電碼被視為一種開關(guān)鍵控的數(shù)據(jù)模式,摩爾斯電碼中的‘劃’比‘點’的時間長3~4倍,不同的‘點’和‘劃’組合形成長短不一的摩爾斯電碼,不同的摩爾斯電碼表示不同的電報符號。發(fā)信者先將所要傳遞的文字翻譯成電報符號,再利用電報機(jī)發(fā)送出去,收信者將收到的電報符號翻譯成報文,以此實現(xiàn)無線文字的傳播。目前通過微機(jī)模擬的方法實現(xiàn)摩爾斯碼信號的自動處理,使無線摩爾斯碼信號數(shù)據(jù)進(jìn)入計算機(jī)信息網(wǎng)的方案已得到解決,利用微機(jī)處理摩爾斯的方案是先通過軟件編程的方法將ASCLL碼進(jìn)行摩爾斯編碼,然后通過微機(jī)并口發(fā)送摩爾斯電碼信號,接收時,先通過聲頻卡來識別接收摩爾斯電碼信號,最后通過軟件解碼成ASCLL碼,此方法在成本相對較高,在實際應(yīng)用中缺乏方便性和靈活性。

根據(jù)海洋通信業(yè)務(wù)的要求,MORSE碼處理系統(tǒng)功能定義為:其一、根據(jù)指令自動編碼、串行發(fā)送MORSE碼。即根據(jù)指令可自動提取ASCLL碼,再將ASCLL碼自動編碼成摩爾斯編碼,將編好的MORSE碼自動串行發(fā)送輸出。其二、根據(jù)指令自動接收、解碼摩爾斯碼,并將ASCLL碼送入系統(tǒng)。即根據(jù)指令自動接收摩爾斯碼輸入,將接收的摩爾斯碼自動解碼成ASCLL碼。將ASCLL碼存儲至目標(biāo)地址或送入系統(tǒng)處理。

通過對摩爾斯碼特點的研究可知,在設(shè)計摩爾斯碼收發(fā)模塊中必須要有能接收和發(fā)送摩爾斯碼信息幀的串行異步通信模塊。首先,該串行通信模塊在指令的控制下,要具有摩爾斯碼的自動發(fā)送能力,同時具有MORSE碼的識別接收能力,因為摩爾斯碼串行異步幀的起始位和停止位都不同于ASCLL碼串行異步幀,并且不同的摩爾斯碼串行幀長度也不一樣。二是摩爾斯碼的解碼和編碼問題,因為計算機(jī)內(nèi)核是以ASCLL碼為信息交換碼的。

由此而來,只要設(shè)計出具有接收和發(fā)送MORSE碼串行信息幀功能,并且具有解碼和編碼摩爾斯碼功能的串行通信子模塊,并將其嵌入在系統(tǒng)總線上,則用計算機(jī)直接處理MORSE碼就成為可能。據(jù)此分析,可以得出摩爾斯碼收發(fā)模塊的設(shè)計要求,一方面能從串行接收端將摩爾斯碼解碼成并行的ASCLL碼,另一方面能將并行的ASCLL碼編碼成串行摩爾斯碼。由此,本文設(shè)計的基于FPGA的摩爾斯碼收發(fā)模塊內(nèi)部組成框圖如圖二所示。

圖 二:基于FPGA的摩爾斯碼收發(fā)模塊內(nèi)部組成框圖

該處理系統(tǒng)的主要功能模塊有:

- 核心控制模塊

- 總線控制模塊

- 可編程中斷處理模塊

- 可編程并行I/O接口(P0、P1、P2、P3)

- 可編程串行接口單元(SIU)

- 可編程定時計數(shù)器0~3(Timer0~Timer3)

- 可編程摩爾斯碼異步收發(fā)模塊

中斷處理模塊有4個外中斷源(int0~int3)和6個內(nèi)中斷源(TF0~TF3、T1/R1、mT1/mR1),SIU是系統(tǒng)的通用串行接口,它有4種工作模式,工作模式1~3是通用串行異步接收發(fā)送USART(Universal Serial Asynchronous Receiver/Transmitter)工作方式。當(dāng)SIU工作于工作模式1或3時,Timer1是其波特率發(fā)生器。

4 仿真與驗證

設(shè)計的驗證包括功能仿真、時序仿真和電路驗證。仿真驗證往往是借助第3方提供的EDA開發(fā)工具軟件包或?qū)S梅抡婀ぞ哕浖韺崿F(xiàn)的。電路驗證還需要開發(fā)驗證平臺,對于系統(tǒng)級芯片驗證平臺的設(shè)計也是一項艱巨而不能回避的任務(wù)。

本文選用的是Altera公司的MaxPlusII作EDA開發(fā)工具,MaxPlusII編譯器支持功能仿真(前仿真)和時序仿真(后仿真)。完成源代碼(VHDL)設(shè)計輸入之后,若要進(jìn)行功能仿真,則在MaxplusII/Compile下,通過選擇Processing菜單下的Functional SNF Extractor命令,打開功能仿真器網(wǎng)表文件(SNF)提取器,再進(jìn)行編譯仿真;若要進(jìn)行定時模擬(時序)仿真,則須在MaxPlusII/Compile下,選擇Processing菜單中的Timing SNF Extractor命令,打開定時模擬器網(wǎng)表文件提取器來進(jìn)行編譯仿真。

電路驗證就是器件編程測試過程。對于常規(guī)的芯片設(shè)計,時序仿真結(jié)束后,仿真軟件就可以產(chǎn)生供器件編程使用的數(shù)據(jù)文件。對EPLD/CPLD來說,是產(chǎn)生熔絲圖文件,即JED文件,對于FPGA來說,是產(chǎn)生位流數(shù)據(jù)文件(Bitstream Generation),然后將編程數(shù)據(jù)下載到對應(yīng)的具體可編程器件中去,然后對其進(jìn)行實際環(huán)境的電路測試。

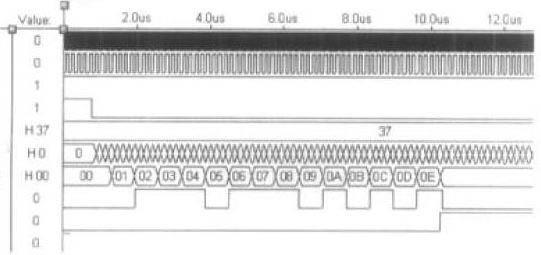

本文選擇CLK頻率為25MHZ,波特率為25M/16=1562500bps。當(dāng)發(fā)送字符‘7’,執(zhí)行發(fā)送命令后,將啟動數(shù)據(jù)發(fā)送的進(jìn)程,將字符‘7’的ASCLL碼值送入ASCLL碼發(fā)送緩存器,通過MaxPlusII的Simulator仿真器,進(jìn)行時序仿真驗證,研究結(jié)果如圖三所示。從圖中可看出,串行信號端子輸出的“2長劃”,“3點”,經(jīng)查表對應(yīng)的就是摩爾斯數(shù)字‘7’,證明數(shù)據(jù)發(fā)送是正確的。另外當(dāng)數(shù)據(jù)輸出結(jié)束后,立刻置高電平,即產(chǎn)生中斷信號mTI,字符‘7’的發(fā)送用時大約10us。

圖 三:仿真驗證數(shù)據(jù)

5 創(chuàng)新點總結(jié)

本文的創(chuàng)新點在于提出了一種基于FPGA的無線通信收發(fā)模塊,并以當(dāng)今海事通信中占重要地位的摩爾斯電碼為例,研究了摩爾斯電碼的數(shù)字化編碼方法,并通過大量的分析設(shè)計和實驗仿真,實現(xiàn)了基于FPGA處理摩爾斯電碼的收發(fā)模塊,仿真結(jié)果也驗證了本文所設(shè)計的摩爾斯電碼數(shù)字化編碼方法正確可行,工作運行可靠。