1 引言

隨著電子商務(wù)的發(fā)展,網(wǎng)絡(luò)安全越來(lái)越重要,。病毒和黑客攻擊造成的損失無(wú)法估算,,防火墻、殺毒軟件等防范措施都是基于軟件的保護(hù),,并不能完全可靠地阻止外界的攻擊,,因此迫切需要比傳統(tǒng)產(chǎn)品更為可靠的技術(shù)防護(hù)措施。GAP技術(shù)是一種基于硬件的保護(hù)技術(shù),。

2 系統(tǒng)工作原理

國(guó)內(nèi)外快速發(fā)展的GAP技術(shù)以物理隔離為基礎(chǔ),,在確保安全性的同時(shí),解決了網(wǎng)絡(luò)之間信息交換的困難,,從而突破了因安全性造成的應(yīng)用瓶頸,。GAP技術(shù)是通過(guò)專用硬件使2個(gè)或者2個(gè)以上的網(wǎng)絡(luò)在不連通的情況下實(shí)現(xiàn)安全數(shù)據(jù)傳輸和資源共享的技術(shù)。它采用獨(dú)特的硬件設(shè)計(jì),,保證在任意時(shí)刻網(wǎng)絡(luò)間的鏈路層斷開(kāi),,阻斷TCP/IP協(xié)議及其他網(wǎng)絡(luò)協(xié)議,能夠顯著地提高內(nèi)部用戶網(wǎng)絡(luò)的安全強(qiáng)度,,與防火墻,、入侵檢測(cè)有很大的區(qū)別:防火墻、IDS技術(shù)從正面抗擊黑客入侵,,而GAP產(chǎn)品以攻擊技術(shù)的物質(zhì)基礎(chǔ)即網(wǎng)絡(luò)介質(zhì)實(shí)現(xiàn)隔離,,使黑客技術(shù)無(wú)用武之地。2個(gè)網(wǎng)絡(luò)(內(nèi)部網(wǎng)絡(luò)和外部網(wǎng)絡(luò))物理斷開(kāi),,但邏輯相連,。GAP的結(jié)構(gòu)如圖1所示。

專用隔離硬件與內(nèi)外網(wǎng)處理單元構(gòu)成一個(gè)GAP系統(tǒng),,隔離硬件由純電路構(gòu)成,,隔離硬件中增加暫存區(qū)的設(shè)計(jì),,滿足了數(shù)據(jù)傳輸?shù)膶?shí)時(shí)性和傳

輸效率要求。筆者在GAP原理的基礎(chǔ)上提出基于FPGA的專用隔離硬件設(shè)計(jì)的新方案,,并對(duì)關(guān)鍵技術(shù)進(jìn)行了深入研究,。

3 系統(tǒng)方案設(shè)計(jì)

3.1 系統(tǒng)結(jié)構(gòu)

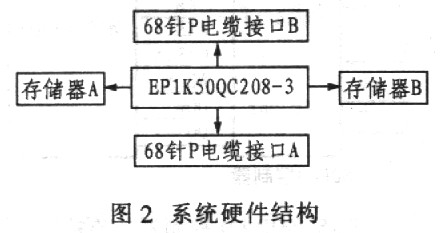

該系統(tǒng)主要由1個(gè)超大規(guī)模邏輯器件、2個(gè)68針P電纜SCSI接口和2個(gè)SDRAM構(gòu)成,,系統(tǒng)整體硬件結(jié)構(gòu)如圖2所示,。

在該系統(tǒng)中,F(xiàn)PGA要集成核心控制器,、SCSI協(xié)議控制器、SDRAM控制器模塊,,核心控制器從SCSI協(xié)議控制器獲得二端處理單元的命令,,執(zhí)行相應(yīng)的動(dòng)作,如檢查設(shè)備,、讀寫數(shù)據(jù)等,,而且將SCSI協(xié)議控制器與存儲(chǔ)器隔離,在任何時(shí)候,,1個(gè)SCSI協(xié)議控制器只能與1個(gè)存儲(chǔ)器構(gòu)成通路,。系統(tǒng)中的緩沖區(qū)由兩片SDRAM構(gòu)成,核心控制器通過(guò)調(diào)用SDRAM控制器IP核對(duì)其進(jìn)行同步操作,,從一片讀數(shù)據(jù)的同時(shí)向另一片寫數(shù)據(jù),,可以完成讀寫乒乓機(jī)制功能,,有助于提高傳輸速度,。專用隔離硬件進(jìn)行內(nèi)外網(wǎng)之間大量數(shù)據(jù)的傳輸,,為了保證高速和實(shí)時(shí),,選用68針的P電纜線,支持16位寬SCSI,。為了滿足功能的需要,,F(xiàn)PGA選用ALTERA公司的EPlK5OQC208-3,其邏輯門和引腳資源豐富,,速度大于50 MHz,。其主要特性如下:2.5 V核心電壓,低功耗設(shè)計(jì),;208引腳,,171個(gè)可用I/O口,;內(nèi)有l(wèi) 728個(gè)邏輯單元和6個(gè)嵌入式RAM塊。

3.2 SCSI協(xié)議控制器的設(shè)計(jì)

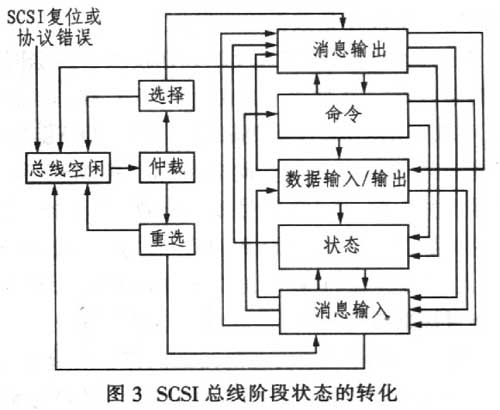

在SCSI總線上進(jìn)行任何處理都需要8個(gè)總線階段:空閑階段,、仲裁階段、選擇階段,、重選階段,、消息輸入/輸出階段、數(shù)據(jù)輸入/輸出階段,、命令階段、狀態(tài)階段,。在任何時(shí)候,,SCSI總線只能處于一個(gè)確定的總線階段,。階段之聞的前后關(guān)聯(lián)受到嚴(yán)格限制,,也就是說(shuō)并不是每個(gè)階段后面都可以跟著任何階段,。圖3示出了SCSI總線階段狀態(tài)的轉(zhuǎn)化,如命令和數(shù)據(jù)階段只能在消息階段之后出現(xiàn),,同樣,消息階段的后面必須緊跟這兩個(gè)階段,,而不是其他階段,。

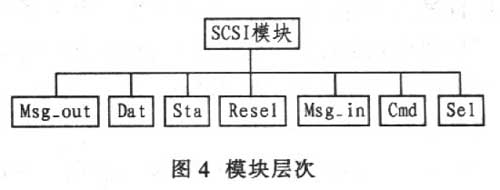

該協(xié)議控制器的設(shè)計(jì)嚴(yán)格按照SCSI總線階段轉(zhuǎn)化過(guò)程,,由以上分析提出SCSI協(xié)議控制器的FP-GA實(shí)現(xiàn)方案:由于空閑,、仲裁這兩個(gè)總線階段的機(jī)理簡(jiǎn)單,故將其直接放在SCSI模塊中實(shí)現(xiàn),,其余每個(gè)階段都有相對(duì)應(yīng)的模塊,整個(gè)系統(tǒng)軟件由1個(gè)頂層模塊和7個(gè)平行的底層模塊構(gòu)成,。模塊層次如圖4所示,。

- SCSI模塊有1個(gè)有限狀態(tài)機(jī),每個(gè)狀態(tài)對(duì)應(yīng)底層的1個(gè)模塊,,并用寄存器S_MODE的不同取指來(lái)表示不同模塊,,通過(guò)這個(gè)狀態(tài)機(jī)實(shí)現(xiàn)階段轉(zhuǎn)換、消息處理,、命令解釋,、數(shù)據(jù)處理和狀態(tài)處理等功能。

- Sel模塊處理選擇階段的時(shí)序,。啟動(dòng)器將信號(hào)BSY,、SEL、ATN和啟動(dòng)器的ID號(hào)以及目標(biāo)器的ID號(hào)置為有效,,啟動(dòng)器隨后釋放BSY信號(hào),經(jīng)過(guò)200ms之后目標(biāo)器將BSY信號(hào)置為有效,,再過(guò)2個(gè)延遲周期后啟動(dòng)器釋放SEL信號(hào)并進(jìn)入消息階段,。

- Resel模塊處理重新選階段的時(shí)序,。啟動(dòng)器將信號(hào)BSY、SEI I/O和啟動(dòng)器的ID號(hào)以及目標(biāo)器的ID號(hào)置為有效,,啟動(dòng)器隨后釋放BSY信號(hào),。最多200ms之后目標(biāo)器必須將BSY信號(hào)置為有效作為響應(yīng)。

- Msg_out模塊處理消息出階段的時(shí)序,。啟動(dòng)器將ATN置為有效,,目標(biāo)器將信號(hào)MSG和C/D信號(hào)置為有效,I/O信號(hào)為無(wú)效,。這意味著接下來(lái)要進(jìn)入的是消息出相序,,啟動(dòng)器將發(fā)出16位寬傳輸消息。發(fā)送完信息字節(jié)后,,啟動(dòng)器將釋放ATN信號(hào),,根據(jù)發(fā)出的信息確定下一個(gè)階段。

- Cmd模塊處理命令階段的命令接收時(shí)序,。目標(biāo)器在接收到啟動(dòng)器80H的消息后進(jìn)入命令階段,。目標(biāo)器需將MSG和I/O置為無(wú)效,將C/D置為有效,,接收完命令后,,將根據(jù)命令判斷接下來(lái)要進(jìn)入的是數(shù)據(jù)輸入階段還是數(shù)據(jù)輸出階段。

- Dat模塊處理數(shù)據(jù)階段的數(shù)據(jù)接收和發(fā)送時(shí)序,。數(shù)據(jù)接收時(shí),,在命令READ、TESI UNIT READY,、INQUIRY,、REQUEST、SENSE,、READ CAPACITY后都將進(jìn)入數(shù)據(jù)進(jìn)相序,。此時(shí)目標(biāo)器將MSG和C/D信號(hào)置為無(wú)效,將I/O信號(hào)置為有效,。目標(biāo)器將發(fā)送相應(yīng)的數(shù)據(jù),。在命令為WRITE后將進(jìn)入數(shù)據(jù)出階段,此時(shí)目標(biāo)器將MSG,、C/D和I/O都置為O,,啟動(dòng)器向目標(biāo)器發(fā)送數(shù)據(jù),之后進(jìn)入消息階段,。

- Status模塊處理狀態(tài)階段的時(shí)序,。在命令完成后將進(jìn)入狀態(tài)階段,目標(biāo)器將MSG信號(hào)置為無(wú)效,將C/D和I/O信號(hào)置為有效,,并發(fā)送命令執(zhí)行的情況是GOOD還是CHECK CONDITON,。狀態(tài)階段結(jié)束后將進(jìn)入消息進(jìn)階段,向啟動(dòng)器說(shuō)明一個(gè)COM-MAND COMPLETED,。至此一個(gè)SCSI訪問(wèn)結(jié)束,。目標(biāo)器將進(jìn)入空閑階段,啟動(dòng)器將可以通過(guò)1個(gè)80 H的消息觸發(fā)另外一個(gè)訪問(wèn),。

- Msg_in模塊處理消息進(jìn)階段的消息發(fā)送時(shí)序,。目標(biāo)器接收到16位寬傳輸?shù)南⒑髮⑦M(jìn)入消息進(jìn)時(shí)序。目標(biāo)器將MSG,、C/D以及I/O都置為有效,,并發(fā)送重復(fù)的信息。發(fā)送完后目標(biāo)器將釋放MSG信號(hào),,并根據(jù)消息確定下一個(gè)階段,。

3.3 SDRAM IP核的

應(yīng)用

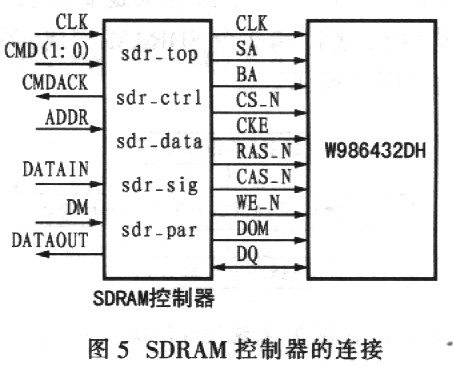

SDRAM是一種高速同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,在嵌入式系統(tǒng)中,,SDRAM因其價(jià)格低,、體積小、速度快,,容量大等優(yōu)點(diǎn)而逐漸成為一種主流器件,,但SDRAM的控制邏輯復(fù)雜,時(shí)序嚴(yán)格,,使用不便,需要控制器提供正確命令來(lái)完成其初始化,、讀寫和刷新等工作,。SDRAM控制器根據(jù)SDRAM的內(nèi)部狀態(tài)轉(zhuǎn)化圖進(jìn)行設(shè)計(jì),而且很多大公司都提供標(biāo)準(zhǔn)SDRAM控制器的IP核參考設(shè)計(jì),。筆者選用了WINBOND公司的W986432DH型SDRAM,,它采用512 Kx4x32位架構(gòu),由4個(gè)BANK構(gòu)成,,每個(gè)BANK對(duì)應(yīng)4 M字節(jié),,按行和列尋址,W986432DH的引腳分為控制,、地址和數(shù)據(jù)信號(hào)三類,。其控制器選用Lattice公司的標(biāo)準(zhǔn)SDR SDRAM IP核,由4個(gè)底層模塊sdr_ctrl,、sdr_sig,、sdr_data、sdr_par和頂層模塊sdr_top組成,如圖5所示。

8dr_ctrl模塊根據(jù)SDRAM內(nèi)部狀態(tài)轉(zhuǎn)化關(guān)系建立2個(gè)有限狀態(tài)機(jī)和1個(gè)計(jì)數(shù)器,能產(chǎn)生正確的中間狀態(tài)作為sdr_sig模塊輸入,。sdr_sig模塊產(chǎn)生面向SDRAM的控制,、地址信號(hào)。sdr_data模塊實(shí)現(xiàn)FPGA與SDRAM之間的數(shù)據(jù)傳輸,。sdr_par模塊完成猝發(fā)長(zhǎng)度,,延時(shí)節(jié)拍等參數(shù)設(shè)置,通過(guò)在該模塊中設(shè)置不同的參數(shù)來(lái)滿足不同的應(yīng)用系統(tǒng),。

sdr__top將底層4個(gè)模塊整合成1個(gè)可以調(diào)用的系統(tǒng),。整個(gè)IP核類似于黑匣子,不用詳細(xì)了解其內(nèi)部實(shí)現(xiàn)細(xì)節(jié),只需了解左邊控制信號(hào)的含義,對(duì)SDRAM的不同操作通過(guò)改變左邊控制信號(hào)的狀態(tài)即可。

4 結(jié)束語(yǔ)

本文提出了基于GAP技術(shù)的網(wǎng)絡(luò)保護(hù)設(shè)備設(shè)計(jì)新方案,,闡述了主要模塊的實(shí)現(xiàn)方法,,限于篇幅不能給出具體細(xì)節(jié)和源代碼。采用1個(gè)FPGA替代單片機(jī)和SCSI協(xié)議控制器,,可減少電路數(shù)量,,降低成本,便于升級(jí),。