數(shù)字中頻

所謂中頻,顧名思義,是指一種中間頻率的信號(hào)形式。中頻是相對(duì)于基帶信號(hào)和射頻信號(hào)來(lái)講的,中頻可以有一級(jí)或多級(jí),它是基帶和射頻之間過(guò)渡的橋梁。

數(shù)字中頻" border="0" height="184" hspace="0" src="http://files.chinaaet.com/images/20100816/5a6234b7-2e10-4fb4-9dc9-84ac8548be0f.jpg" width="400" />

如圖1所示,中頻部分用數(shù)字方式來(lái)實(shí)現(xiàn)就稱(chēng)之為數(shù)字中頻。數(shù)字中頻技術(shù)通常包括上下變頻(DUC/DDC)、波峰因子衰減(CFR)和數(shù)字預(yù)失真(DPD)。

DUC/DDC

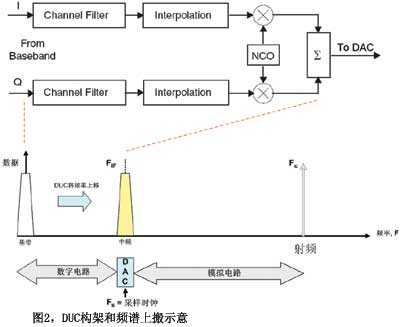

DUC實(shí)現(xiàn)了從“復(fù)”基帶(Baseband)信號(hào)到“實(shí)”帶通(Passband)信號(hào)的轉(zhuǎn)換。輸入的復(fù)基帶信號(hào)采樣率相對(duì)較低,通常是數(shù)字調(diào)制的符號(hào)率。基帶信號(hào)經(jīng)過(guò)濾波,然后被轉(zhuǎn)換成一個(gè)更高的采樣率,從而調(diào)制到NCO的中頻載波頻率。

DUC通常需要完成頻譜整型(Pulse shaping),然后調(diào)制到中頻載波,以便于經(jīng)由DAC驅(qū)動(dòng)后面的模擬轉(zhuǎn)換器。

在圖2中,通道濾波器(Channel Filter)完成基帶信號(hào)的頻譜整型,通常由FIR實(shí)現(xiàn)。插值(Interpolation)部分完成信號(hào)采樣率變換和濾波功能,可以采用CIC或者FIR實(shí)現(xiàn)。對(duì)于一個(gè)窄帶信號(hào),如果需要高倍采樣率變換,那么CIC將是非常合適的,無(wú)論是在實(shí)現(xiàn)性能或是資源節(jié)省方面,CIC都將優(yōu)

于FIR。

NCO是一個(gè)數(shù)控振蕩器,也叫DDS,可以用來(lái)產(chǎn)生一對(duì)相互正交的正弦和余弦載波信號(hào),與插值(增加采樣率)以后的基帶信號(hào)混頻,完成頻譜上搬。

與DUC相反,DDC基本上完成了以下幾個(gè)工作:

1. 頻譜下搬:將ADC送來(lái)的數(shù)字信號(hào)有用頻譜,從中頻搬移到基帶

2. 采樣率降低:將頻譜搬移后的數(shù)據(jù)從ADC的高速采樣率降低到一個(gè)合適的采樣速率水平,通過(guò)抽取(Decimation)實(shí)現(xiàn)。

3. 通道濾波:在將I/Q信號(hào)送入基帶處理以前,需要再對(duì)其進(jìn)行濾波

實(shí)際上,數(shù)字上下變頻技術(shù)應(yīng)用非常廣泛,其在無(wú)線(xiàn)通信、有線(xiàn)電視網(wǎng)絡(luò)(Cable Modem)、數(shù)字電視廣播(DVB)、醫(yī)學(xué)成像設(shè)備(超聲),以及軍事領(lǐng)域當(dāng)中,都是不可或缺的功能。

CFR

目前許多無(wú)線(xiàn)通信系統(tǒng),如WCDMA、WiMAX,其中頻信號(hào)通常由多個(gè)獨(dú)立的基帶信號(hào)相加而成。合成的中頻信號(hào)有較大的峰均比(Peak-to-Average Ratio),并符合高斯分布。而通常功放(PA)的線(xiàn)性區(qū)是有限的,較大PAR的中頻信號(hào)對(duì)應(yīng)的PA的工作范圍將被縮小,從而引起PA效率的降低。因此在PA之前減小中頻信號(hào)的PAR是非常重要的。波峰因子衰減(CFR)正是用來(lái)完成這一功能的,它將有利于保證PA輸出的線(xiàn)性度,降低帶外輻射,提高PA效率。

目前,中頻采用的CFR算法有:波峰箝位(Clip),波峰修整(Peak Windowing)和波峰消減(Peak Cancellation)。其中波峰修整方式的性能和可實(shí)現(xiàn)性都較為適中。波峰消減相對(duì)于波峰修整有較好的帶外特性,但需消耗更多的FPGA資源。

DPD

在無(wú)線(xiàn)通信系統(tǒng)中,往往需要PA的輸出具有很高的線(xiàn)性度以滿(mǎn)足空中接口標(biāo)準(zhǔn)的苛刻要求,而線(xiàn)性功放又非常昂貴。為了盡可能提升PA的輸出效率和降低成本,必須校正PA的非線(xiàn)性特性,而對(duì)PA的輸入信號(hào)進(jìn)行預(yù)失真處理是一個(gè)不錯(cuò)的選擇。

DPD實(shí)現(xiàn)方式分為查找表(LUT)和多項(xiàng)式(Polynomial)兩類(lèi)。兩種算法的優(yōu)缺點(diǎn)如表1所示。

FPGA實(shí)現(xiàn)優(yōu)勢(shì)

FPGA實(shí)現(xiàn)數(shù)字中頻

隨著WiMAX/LTE等寬帶無(wú)線(xiàn)通信技術(shù)的逐漸成熟,對(duì)無(wú)線(xiàn)設(shè)備數(shù)字中頻帶寬的要求也越來(lái)越高。同時(shí)如MIMO等多天線(xiàn)技術(shù)日漸廣泛應(yīng)用,數(shù)字中頻的通道數(shù)也在迅速增加。

對(duì)于如此大的運(yùn)算帶寬需求,許多DSP處理器難以滿(mǎn)足實(shí)際應(yīng)用,而專(zhuān)用芯片(ASSP)又缺乏相應(yīng)的靈活性。采用FPGA實(shí)現(xiàn)數(shù)字中頻,能夠很好的協(xié)調(diào)處理能力和靈活性之間的矛盾。同時(shí)Altera公司針對(duì)3G/4G等應(yīng)用開(kāi)發(fā)了大量的數(shù)字中頻參考設(shè)計(jì)和IP,簡(jiǎn)化了設(shè)計(jì)者的開(kāi)發(fā)難度,縮短了設(shè)計(jì)周期。

FPGA器件屬于硬件,它的特點(diǎn)是比較適合速度較高、邏輯關(guān)系不復(fù)雜的數(shù)據(jù)通路實(shí)現(xiàn)。

通過(guò)我們對(duì)前面DDC和DUC功能的分析,我們發(fā)現(xiàn)實(shí)現(xiàn)DDC/DUC的模塊和運(yùn)算主要有CIC/FIR濾波、NCO、插值/抽取、混頻。這些基本上屬于算法簡(jiǎn)單、但計(jì)算速度較高的處理,非常適合于FPGA的實(shí)現(xiàn)。

從另一個(gè)角度講,F(xiàn)PGA相比DSP處理器的優(yōu)勢(shì)是并行構(gòu)架。一個(gè)DDC/DUC模塊完成以后,只要做簡(jiǎn)單的復(fù)制,就可以擴(kuò)展到多路DDC/DUC。同時(shí),一個(gè)ADC/DAC器件可以連接多個(gè)通道的DDC/DUC,從而可以輕松支持多載波(Multi-carrier)系統(tǒng)。

而有時(shí)候FPGA內(nèi)部的資源有限,多路DDC/DUC甚至可以做時(shí)分復(fù)用,公用一塊DDC/DUC的電路,當(dāng)然電路工作時(shí)鐘也需要提高相應(yīng)的倍數(shù),只要在該FPGA性能允許范圍以?xún)?nèi)就可以了。Altera擁有支持包括WCDM A,TD-SCDMA,和WiMAX的參考設(shè)計(jì)。

CFR電路的計(jì)算量較大,例如TD-SCDMA,采樣率從61.44MHz~92.16MHz,基于FPGA的并行處理可以輕松完成。

多項(xiàng)式DPD分為前向和反向模塊,前向模塊為預(yù)失真器,由多個(gè)FIR濾波器組成,非常適合硬件FPGA實(shí)現(xiàn),Altera的IP核可以提供完善的FIR支持。反向模塊為特定的收斂算法,如LMS、RLS,Altera都可以提供相應(yīng)的參考設(shè)計(jì)。其中,對(duì)于RLS,Altera的參考設(shè)計(jì)采用QR分解方式,縮短了收斂時(shí)間,提高了算法的穩(wěn)定性。

Altera提供的資源

Altera公司除了在器件設(shè)計(jì)上考慮了數(shù)字中頻應(yīng)用的實(shí)際情況外,也在IP核、控制粘合邏輯、接口邏輯、設(shè)計(jì)工具和流程,以及參考設(shè)計(jì)方面做了大量的工作。

在FPGA器件資源上,Altera最新的Cyclone和Stratix系列在內(nèi)嵌存儲(chǔ)器和乘累加模塊方面,無(wú)論是數(shù)量還是速度都有較大程度的提高。

在DSP的IP核組件方面,Altera能提供包括FIR,NCO,CIC,CORDIC等功能組件。為了方便用戶(hù)的系統(tǒng)集成,同時(shí)還提供了用于這些模塊之間互聯(lián)的統(tǒng)一接口

:Avalon Streaming(Avalon-ST)接口。另外,為了多通道的復(fù)用和解復(fù)用,Altera還設(shè)計(jì)了Avalon-ST接口的包格式轉(zhuǎn)換器(Packet Format Converter),用于將輸入的單個(gè)或多個(gè)Avalon-ST通道與輸出的單個(gè)或多個(gè)Avalon-ST通道提供時(shí)間和空間接口,用于多通道的復(fù)用與解復(fù)用。

在一些需要靈活性的領(lǐng)域,比如DPD,Altera的Nios II嵌入式處理器正好可以發(fā)揮功用,例如,在DPD的反饋路徑上,它可以幫助用戶(hù)靈活增加自己的插值例程。Nios II嵌入式處理器還可幫助系統(tǒng)做一些數(shù)據(jù)統(tǒng)計(jì)、參數(shù)重配以及其它管理工作。

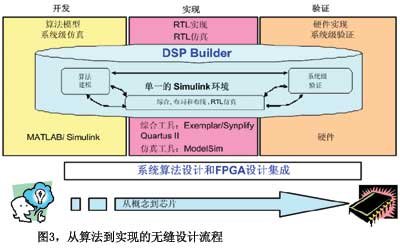

在設(shè)計(jì)驗(yàn)證工具和流程方面,Altera力推MATLAB/Simulink+DSP Builder+Quartus II的一體化設(shè)計(jì)流程。如圖3所示。

同時(shí)Simulink還可以集成ModelSim和FPGA內(nèi)嵌邏輯分析儀SignalTap-II來(lái)協(xié)助用戶(hù)做功能仿真、調(diào)試。另外,硬件在環(huán)(Hardware In Loop)功能方面可以幫助用戶(hù)在實(shí)際硬件上驗(yàn)證設(shè)計(jì)算法,同時(shí)也加速了驗(yàn)證的速度。

參考設(shè)計(jì)

WiMAX DUC/DDC

Altera的WiMAX DDC/DUC參考設(shè)計(jì)是基于1024點(diǎn)FFT的OFDM設(shè)計(jì)的,其工作帶寬是10MHz。基帶信號(hào)的采樣率是11.424MSps,也就是符號(hào)率(Symbol Rate)。中頻信號(hào)的采樣率是91.392MSps。從基帶到中頻,總共需要8倍的采樣率變化。

我們前面講過(guò),CIC適合于窄帶高倍變換領(lǐng)域,而這里只需要8倍變換,同時(shí)有用信號(hào)帶寬是10MHz,因此采用FIR做抽取或插值濾波是更好的選擇。

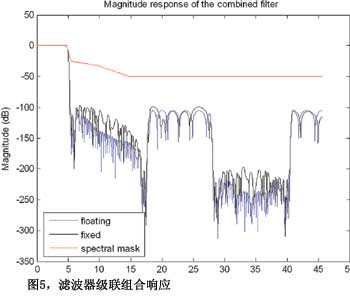

如圖4所示,在功能劃分時(shí),我們考慮實(shí)現(xiàn)的資源和效率,將整形濾波和抽取插值濾波分為3個(gè)FIR來(lái)設(shè)計(jì):G(z)負(fù)責(zé)頻譜整形,通常是根升余弦(RRC)濾波器;Q(z)負(fù)責(zé)2倍抽取或插值濾波;P(z)負(fù)責(zé)4倍抽取或插值濾波。

為了節(jié)省FPGA資源,提高性能,我們將工作頻率最低的G(z)設(shè)計(jì)成111階FIR,其過(guò)渡帶最窄;Q(z)其次,79階;而P(z)只有39階,其工作頻率最高。三個(gè)濾波器的組合響應(yīng)如圖5所示,完全滿(mǎn)足WiMAX所要求的模板(Mask)。

在具體FPGA實(shí)現(xiàn)上,我們考慮I/Q兩路的濾波特性完全一致,為了節(jié)省器件資源,我們將I/Q兩路的三級(jí)FIR作復(fù)用。請(qǐng)參考圖6。

在DDC上,我們首先將91.392MSps的中頻信號(hào)通過(guò)過(guò)采樣(Oversample)變?yōu)?82.784MSps的連續(xù)兩個(gè)時(shí)鐘周期的相同信號(hào),分別和NCO混頻,經(jīng)過(guò)三級(jí)FIR,最終得到兩路11.424MSps的I/Q信號(hào)。

在DUC上,F(xiàn)IR分別工作在 22.848MSps、45.696MSps和 182.784MSps。最后,將混頻的兩路IQ信號(hào)相加,得到一個(gè)帶通的實(shí)數(shù)信號(hào),采樣率為91.392MSps。

在多通道的復(fù)用/解復(fù)用上,我們使用Altera的Avalon-ST包格式轉(zhuǎn)換模塊(PFC)來(lái)做模塊互聯(lián)。

WiMAX基站中典型的要求為2個(gè)發(fā)送天線(xiàn)和4個(gè)接收天線(xiàn),而該參考設(shè)計(jì)也可以支持2個(gè)發(fā)送天線(xiàn)和4個(gè)接收天線(xiàn)的方式。

通過(guò)對(duì)參考設(shè)計(jì)的仿真驗(yàn)證,DUC的相對(duì)星座誤差(Relative Constellation Error)大大好于規(guī)定值。比如,在64QAM 3/4碼率時(shí),測(cè)量的RCE為-55.29dB。DDC的接受靈敏度和鄰道抑制(Adjacent Channel Rejection)指標(biāo)都遠(yuǎn)好于所要求的值。

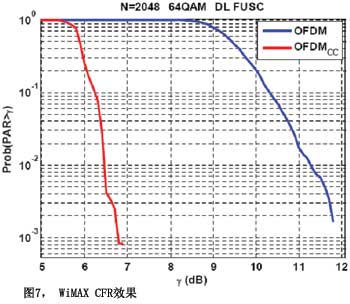

Wi MAX CFR

WiMAX系統(tǒng)對(duì)CFR提出了更高的要求。由于采用了64QAM調(diào)制方式,誤差矢量幅度(EVM)要求<3%,對(duì)峰均比(PAR)和鄰頻道泄漏比(ACLR)也有更嚴(yán)格的要求。Altera的WiMAX CFR方案采用美國(guó)喬治亞科技學(xué)院的約束鉗位算法(Constrained Clipping),其EVM<3%,PAR削減>5dB,而且信號(hào)帶外擴(kuò)散極小。參考圖7。

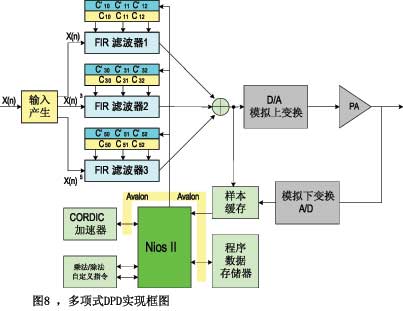

WiMAX DPD

WiMAX的中頻帶寬超過(guò)10MHz,同時(shí)需要引入LMS/RLS等自適應(yīng)算法,對(duì)整個(gè)DPD模塊的DSP處理能力和靈活度提出了很高的要求。采用Altera的“片內(nèi)處理器NIOS II+FPGA硬件協(xié)處理單元”方式可以很好的滿(mǎn)足設(shè)計(jì)要求。

如圖8所示,前向模塊為預(yù)失真器,由多個(gè)FIR濾波器組成。在反向鏈路中,我們收集一套64個(gè)樣本在“樣本緩存”中,Nios嵌入式處理器可以幫助計(jì)算CORDIC的輸入,CORDIC加速器完成QR分解工作。Nios然后進(jìn)行倒轉(zhuǎn)代換,更新前向鏈路中FIR濾波器的系數(shù)。采用軟處理器NIOS+CORDIC加速器的方式來(lái)完成QRD_RLS的

上三角矩陣運(yùn)算,具有很好的靈活性,我們可以調(diào)節(jié)CORDIC加速器的數(shù)目以提高反向模塊的數(shù)據(jù)吞吐率。

整個(gè)DPD參考設(shè)計(jì)的資源耗費(fèi)大致為2萬(wàn)個(gè)邏輯單元。

TD-SCDMA

TD-SCDMA網(wǎng)絡(luò)在國(guó)內(nèi)開(kāi)始大規(guī)模鋪設(shè),目前國(guó)內(nèi)廠(chǎng)商基站的數(shù)字中頻多采用大廠(chǎng)的專(zhuān)用芯片(ASSP)。對(duì)于6~8天線(xiàn)的應(yīng)用,完成DUC/DDC/CFR/DPD等功能,可能會(huì)使用到超過(guò)10片ASSP。無(wú)論是在成本、功耗和靈活性上,都非常不理想。

Altera的TD-SCDMA數(shù)字中頻方案可以在2片~3片F(xiàn)PGA上完成上述功能,從而在降低系統(tǒng)成本、功耗,提高集成度,以及可升級(jí)性上都有較大優(yōu)勢(shì)。

值得一提的是,目前Altera針對(duì)TD-SCDMA的CFR方案采用波峰修整算法,所需的FPGA資源較小(約3000邏輯單元+7乘法器+7塊存儲(chǔ)器),同時(shí)性能可以很好的滿(mǎn)足3G的需求。