1 引 言

可編程邏輯器件(PLD)是當(dāng)今國際上流行的新一代數(shù)字系統(tǒng)邏輯器件。它主要是一種“與-或”兩級(jí)式結(jié)構(gòu)器件,除了具有高速度、高集成度性能之外,其最大的特點(diǎn)就是用戶可定義其邏輯功能。因此PLD能夠適應(yīng)各種需求,大大簡化系統(tǒng)設(shè)計(jì),縮小系統(tǒng)規(guī)模,提高系統(tǒng)可靠性,受到廣大工程技術(shù)人員的青睞。

可編程邏輯器件種類繁多,性能各異,主要有以下幾種基本類型:可編程只讀存儲(chǔ)器(PROM),現(xiàn)場(chǎng)可編程邏輯陣列(FPGA),編程陣列邏輯(PAL),通用陣列邏輯(GAL)。通用陣列邏輯GAL(Generic ArrayLogic)是新一代的可編程邏輯器件,是采用先進(jìn)的E2CMOS工藝制造的大規(guī)模集成電路,是新產(chǎn)品設(shè)計(jì)的理想器件。用戶可將設(shè)計(jì)的邏輯電路通過IBM-PC機(jī)對(duì)GAL芯片編程。編程過程可分為三步:(1)根據(jù)設(shè)計(jì)要求寫出與或邏輯表達(dá)式的布爾方程;(2)利用編譯器,由計(jì)算機(jī)輔助編程,得到陣列的熔絲圖,并驗(yàn)證其正確性;(3)由于GAL的立即電可擦性,把編譯器的輸出送入編程器。編程器便按已確定的熔絲圖將新的內(nèi)部結(jié)構(gòu)信息存儲(chǔ)起來。這種編程方法簡單易行。

2 系統(tǒng)組成與系統(tǒng)設(shè)計(jì)

2.1 系統(tǒng)的組成

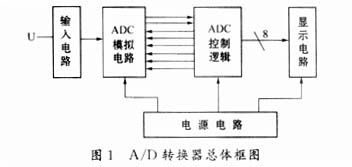

我們介紹的系統(tǒng)是一種基于兩次采樣的高準(zhǔn)確度A/D轉(zhuǎn)換器。它的計(jì)數(shù)容量可達(dá)兩百萬碼,相當(dāng)于六位半的A/D轉(zhuǎn)換器,是目前國內(nèi)所能做到的一種較高準(zhǔn)確度的A/D轉(zhuǎn)換器。它的工作原理是對(duì)被測(cè)信號(hào)進(jìn)行兩次采樣:第一次采樣由雙積分型A/D轉(zhuǎn)換器把被測(cè)信號(hào)高位轉(zhuǎn)換成對(duì)應(yīng)的數(shù)字量N2h。第二次采樣的定時(shí)積分時(shí)間要比第一次采樣的定時(shí)積分時(shí)間延長m倍,并用N2h來定時(shí)接通相應(yīng)的基準(zhǔn)電壓到求和積分器。定值積分時(shí)則改用小基準(zhǔn)電壓Es/n來進(jìn)行放電,從而獲得與被測(cè)信號(hào)低位相應(yīng)的讀數(shù)N2l。綜合兩次采樣結(jié)果,A/D轉(zhuǎn)換器的總計(jì)數(shù)值為:mnN2h+N2l。它的總體框圖如圖1所示。

由于系統(tǒng)正常工作時(shí)需要一個(gè)龐大的邏輯控制電路來完成兩次采樣過程,所以我們采用PLD來實(shí)現(xiàn)硬件控制邏輯。

2.2 系統(tǒng)的設(shè)計(jì)

在所有PLD中,由于GAL器件具有低功耗、高速度、可重復(fù)編程和輸出可重組態(tài)的特點(diǎn),加上它的性價(jià)比明顯優(yōu)于SSI/MSI器件,所以被選用來完成高準(zhǔn)確度A/D轉(zhuǎn)換器的硬件邏輯控制電路。

2.2.1 硬件邏輯控制電路

GAL16V8芯片主要有五種輸出配置功能。設(shè)計(jì)中采用了其寄存器型器件中的組合輸出結(jié)構(gòu)和寄存器型輸出結(jié)構(gòu)。我們采用的GAL16V8芯片如圖2所示。

它的各個(gè)管腳定義如下:

mT1:定時(shí)積分的定時(shí)時(shí)間信號(hào)(低電平有效),Th:反饋定時(shí)信號(hào)(低電平有效),ST:ADC轉(zhuǎn)換啟動(dòng)信號(hào)(正跳沿有效),Sc:二次采樣信號(hào)(高電平有效),INPUT:檢零信號(hào)輸入(Ux>0時(shí)為0,Ux<0時(shí)為1),Tx:結(jié)果計(jì)數(shù)輸出(高電平有效),Sg:極性輸出(Ux>0時(shí)為0,Ux<0時(shí)為1),INT1:中斷信號(hào)(正跳沿有效),Kc:放電回路控制(高電平有效),Kx:被測(cè)量接入控制(高電平有效),VrN:負(fù)基準(zhǔn)接入控制(高電平有效),Vr:正基準(zhǔn)接入控制(高電平有效),Vr-10:十分之一正基準(zhǔn)(高電平有效),Csg:釋放極性輸出寄存器(高電平有效),CLK:時(shí)鐘輸入端。

2.2.2 硬件邏輯控制電路工作過程

硬件邏輯電路工作時(shí),A/D轉(zhuǎn)換啟動(dòng)信號(hào)ST由“0”變“1”,標(biāo)志第一次采樣正式開始。同時(shí),Kx變?yōu)楦唠娖剑硎窘尤氡粶y(cè)量Ux;mT1變?yōu)榈碗娖剑到y(tǒng)進(jìn)入第一次采樣的定時(shí)積分時(shí)間。假設(shè)Ux>0,則檢零信號(hào)INPUT為“0”。當(dāng)mT1變?yōu)楦唠娖綍r(shí),第一次采樣的定時(shí)積分時(shí)間結(jié)束。接入VrN,進(jìn)入第一次采樣的定量積分階段。當(dāng)檢零信號(hào)發(fā)生變化時(shí),表明定量積分結(jié)束。在定量積分過程中,Tx有計(jì)數(shù)結(jié)果輸出,這是被測(cè)信號(hào)的高位值。中斷信號(hào)INT1由“1”變“0”,表示第一次采樣結(jié)束,系統(tǒng)進(jìn)入休止階段。當(dāng)ST和二次采樣信號(hào)Sc同時(shí)產(chǎn)生正跳沿時(shí),系統(tǒng)進(jìn)入第二次采樣階段。在第二次采樣過程中,邏輯控制過程與第一次采樣大致相同,只是定時(shí)積分時(shí)間變?yōu)榈谝淮尾蓸佣〞r(shí)積分時(shí)間的m倍,即mT1,而且在每一個(gè)T1時(shí)間內(nèi),都接通反饋定時(shí)信號(hào)Th。在定值積分階段,改用小基準(zhǔn)電壓Vr-10來進(jìn)行放電。從而Tx有計(jì)數(shù)結(jié)果輸出,這是被測(cè)信號(hào)的低位值。至此,兩次采樣A/D轉(zhuǎn)換結(jié)束。

2.2.3 硬件邏輯控制電路時(shí)序圖

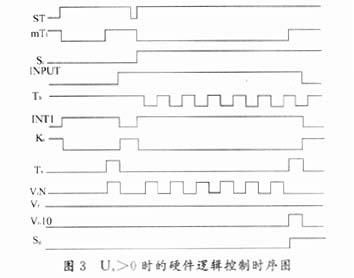

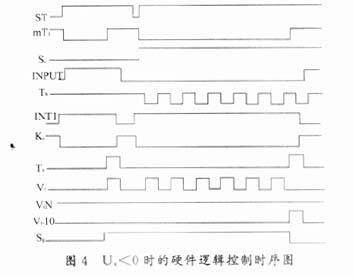

利用可編程邏輯器件設(shè)計(jì)控制電路的關(guān)鍵在于正確畫出邏輯電路的時(shí)序圖。通過準(zhǔn)確分析兩次采樣A/D轉(zhuǎn)換器的邏輯電路,畫出它的時(shí)序圖。

(1)被測(cè)電壓為正時(shí),GAL各管腳的時(shí)序圖如圖3所示。

(2)被測(cè)電壓為負(fù)時(shí),GAL各管腳的時(shí)序圖如圖4所示。

3 GAL可編程器件程序

根據(jù)硬件邏輯電路時(shí)序圖,現(xiàn)對(duì)GAL16V8芯片進(jìn)行編程,完成上述邏輯功能。

4 結(jié)束語

通過示波器對(duì)GAL16V8芯片各管腳輸出的波形進(jìn)行觀察,得到正確的波形輸出。把采用GAL后測(cè)得的數(shù)據(jù)與原有的邏輯電路測(cè)得的數(shù)據(jù)進(jìn)行比較,證明利用GAL所得的數(shù)據(jù)完全正確。因此,由GAL設(shè)計(jì)高準(zhǔn)確度A/D轉(zhuǎn)換器的硬件邏輯控制電路是可行的。此外,由于GAL只有一個(gè)時(shí)鐘控制端,在信號(hào)進(jìn)行動(dòng)作時(shí),為減少由于時(shí)鐘引起的誤差,使用的時(shí)鐘頻率要高于計(jì)數(shù)器使用時(shí)鐘頻率的兩倍以上。時(shí)鐘頻率越高,所帶來的誤差就越小。

與一般邏輯電路相比,GAL不僅保證了系統(tǒng)的正確性,更提高了系統(tǒng)的保密性和可靠性。

參考文獻(xiàn)

1 費(fèi)正生.六位半數(shù)字電壓表的研究鑒定材料.哈爾濱:哈爾濱理工大學(xué)儀表教研室,1999

2 李 元.?dāng)?shù)字電路與邏輯設(shè)計(jì).南京:南京大學(xué)出版社,1997

3 何立民.單片機(jī)應(yīng)用技術(shù)選編(3).北京:北京航空航天大學(xué)出版社,1995

4 曾繁泰.可編程邏輯器件應(yīng)用導(dǎo)論.北京:清華大學(xué)出版社,2001