引言

當(dāng)前,越來越多的通信系統(tǒng)工作在很寬的頻帶上,對(duì)于保密和抗干擾有很高要求的某些無線通信更是如此,隨著信號(hào)處理器件的處理速度越來越快,數(shù)據(jù)采樣的速率也變得越來越高,在某些電子信息領(lǐng)域,要求處理的頻帶要盡可能的寬、動(dòng)態(tài)范圍要盡可能的大,以便得到更寬的頻率搜索范圍,獲取更多的信息量。因此,通信系統(tǒng)對(duì)信號(hào)處理前端的A/D采樣電路提出了更高的要求,即希望A/D轉(zhuǎn)換速度快而采樣精度高,以便滿足系統(tǒng)處理的要求。

可編程門陣列FPGA的出現(xiàn)已經(jīng)顯著改變了數(shù)字系統(tǒng)的設(shè)計(jì)方式。應(yīng)用可編程門陣列FPGA,可使數(shù)字系統(tǒng)設(shè)計(jì)具有高度的靈活性,因此FPGA的應(yīng)用越來越廣泛,而新一代FPGA--Virtex Ⅱ-PRO的出現(xiàn)使FPGA的功能更加強(qiáng)大,但隨之而來的是要求提高數(shù)據(jù)的傳輸速率,過去人們總是關(guān)心如何提高處理器運(yùn)行速度,而現(xiàn)在關(guān)心的是怎樣才能更快地將數(shù)據(jù)從一個(gè)芯片傳輸?shù)搅硪粋€(gè)芯

片。可見,高速數(shù)據(jù)采集系統(tǒng)的輸入輸出接口設(shè)計(jì)就顯得尤為重要。

1 高速采集系統(tǒng)介紹

數(shù)據(jù)采集系統(tǒng)原理框圖如圖1所示,輸入的中頻信號(hào)經(jīng)A/D采樣電路采樣后,轉(zhuǎn)換成LVDS信號(hào)送入FPGA中,或通過FPGA的端口RocketIO從高速接口輸出,或通過FPGA的端口LVDS循環(huán)存儲(chǔ)于高速緩存中,再由低速接口輸出。其中,F(xiàn)PGA主要完成對(duì)外接口管理、高速緩存的控制和管理。時(shí)鐘控制電路對(duì)A/D數(shù)據(jù)轉(zhuǎn)換器和可編程門陣列FPGA起同步和均衡作用。

2 輸入輸出接口研究

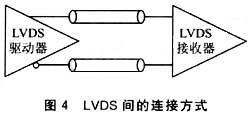

Virtex Ⅱ-PRO系列是在Virtex Ⅱ系列FPGA的基礎(chǔ)上,嵌入了高速I/O接口和IBM PowerPC處理器,它能實(shí)現(xiàn)超高帶寬的系統(tǒng)芯片設(shè)計(jì),支持LVDS,LVPECL等多種差分接口,適應(yīng)性很強(qiáng)。其中高速串行(MGT)技術(shù)采用了RocketIO技術(shù),在可編程邏輯器件中內(nèi)嵌了速率為3.125Gb/s的多端串行通信接口,該技術(shù)包括千Mb以太網(wǎng)、10千以太網(wǎng)、3GIO、SerialATA、Infiniband和Fibre Channel,為高性能接口提供了完成的解決方案。LVDS(Low Voltage Differential Signaling)信號(hào)標(biāo)準(zhǔn)是一種小振幅差分信號(hào)技術(shù),如圖2所示,它使用非常低的幅度信號(hào)(100-450mV),通過一對(duì)平行的PCB走線或平衡電纜傳輸數(shù)據(jù)。在兩條平行的差分信號(hào)線上流經(jīng)的電流方向相反,噪聲信號(hào)同時(shí)耦合到兩條線上,而接收端只關(guān)心兩信號(hào)的差值,于是噪聲被抵消。由于兩條信號(hào)線周圍的電磁場(chǎng)也互相抵消,故差分信號(hào)傳輸比單線信號(hào)傳輸電磁輻射小很多,從而提高了傳輸效率并降低了功耗。

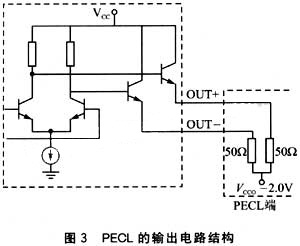

在高速數(shù)據(jù)采集系統(tǒng)中,使用了最新的A/D芯片MAX104A。該芯片是Maxim公司的最新產(chǎn)品,采樣頻率可以達(dá)到1GHz,采樣精度為8位。芯片輸出是PECL(Positive Emitter-Coupled Logic)電平輸出。PECL信號(hào)的擺幅相對(duì)ECL要小,適合于高速數(shù)據(jù)的串行或并行連接。PECL的輸出電路結(jié)構(gòu)如圖3所示。該電路包含一個(gè)差分對(duì)管和一對(duì)射隨器。輸出射隨器工作在正電壓范圍內(nèi),無信號(hào)時(shí)電流始終存在,這樣有利于提高開關(guān)速度,標(biāo)準(zhǔn)的輸出負(fù)載接50Ω電阻至VCCO-2V的電平上,如圖3所示,在這種負(fù)載條件下,OUT+與OUT-的靜態(tài)電平典型值為UCCO-1.3V,OUT+與OUT-輸出電流為14mA。PECL結(jié)構(gòu)的輸出阻抗很低,典型值為4-5Ω,這表明它有很強(qiáng)的驅(qū)動(dòng)能力。但當(dāng)負(fù)載與PECL的輸出端之間有一段傳輸線時(shí),低阻抗造成的失配將導(dǎo)致信號(hào)時(shí)域波形的振鈴現(xiàn)象。

3 RocketIO設(shè)計(jì)

Xilinx公司的Virtex Ⅱ-PRO FPGA采用具有時(shí)鐘恢復(fù)功能的全雙工串行I/O收發(fā)器,可高效地實(shí)施每通道帶寬達(dá)到3.125Gb/s的不同協(xié)議設(shè)計(jì)。收發(fā)器支持高達(dá)到每通道3.125Gb/s的數(shù)據(jù)速率,并可利用通道捆綁功能滿足各種應(yīng)用不斷增長(zhǎng)的數(shù)據(jù)傳輸速率的要求,Virtex Ⅱ-PRO的收發(fā)模塊由物理編碼子層(PCS)和物理介質(zhì)接入(PMA)構(gòu)成,其中物理編碼子層提供與FPGA邏輯內(nèi)的數(shù)字接口,內(nèi)部包括:循環(huán)冗余碼校驗(yàn)CRC、8B/10B編解碼器、先進(jìn)先出緩沖器FIFO;物理介質(zhì)接入提供與外部媒體的模擬接口,其中包括:20倍時(shí)鐘倍頻器、發(fā)送端時(shí)鐘生成器、發(fā)送緩沖器、串化器、接收端的時(shí)鐘恢復(fù)電路,接收緩沖器、解串器、可變速率的全雙工收發(fā)器、可編程的五級(jí)差分輸出幅度(擺率)控制和可編程的四級(jí)輸出預(yù)加重模塊。RocketIO的原始設(shè)計(jì)是比較復(fù)雜的,但幸運(yùn)的是,Xilinx公司提供了大量成熟的和高效的IP(Intellectual Property)核來使用。如果能夠很好地掌握該工具的使用,將會(huì)極大地縮短設(shè)計(jì)的進(jìn)度,減少開發(fā)和調(diào)試時(shí)間,由于IP核是根據(jù)Xilinx FPGA器件的特點(diǎn)和結(jié)構(gòu)設(shè)計(jì)的,直接用Xilinx FPGA底層硬件原語進(jìn)行描述,可充分地將FPGA的性能開發(fā)出來,其實(shí)現(xiàn)結(jié)果在面積和速度上都能達(dá)到令人滿意的效果。在設(shè)計(jì)中,還要考慮到以下方面。

(1)參考時(shí)鐘

高性能的通信質(zhì)量要求有高穩(wěn)定性和高精度的時(shí)鐘源。抖動(dòng)和頻偏是衡量時(shí)鐘源的兩個(gè)重要指標(biāo)。頻偏是指時(shí)鐘標(biāo)稱頻率與實(shí)際頻率的偏差,主要是受晶體精度的影響,由于RocketIO模塊內(nèi)部將輸入?yún)⒖紩r(shí)鐘20倍頻,而RocketIO模塊可容忍的輸入?yún)⒖紩r(shí)鐘抖動(dòng)公差為40ps,可見參考時(shí)鐘的抖動(dòng)對(duì)其性能有直接影響,所以必須選擇性能優(yōu)良的參考時(shí)鐘。抖動(dòng)一般是指一個(gè)實(shí)際情況下的周期信號(hào)每個(gè)周期的圖樣相對(duì)于該信號(hào)理想情況下一個(gè)周期圖樣的偏差。抖動(dòng)產(chǎn)生的原因包括:時(shí)鐘晶體本身的機(jī)械振動(dòng)、器件的熱噪聲和電源串入噪聲等。抖動(dòng)可以分為確定性抖動(dòng)和隨機(jī)抖動(dòng),確定性抖動(dòng)包括信號(hào)在傳輸中煤質(zhì)損耗、碼間串?dāng)_(ISI)等周期性因素導(dǎo)致的抖動(dòng);隨機(jī)抖動(dòng)是由半導(dǎo)體器件熱噪聲、電源波動(dòng)等共模隨機(jī)噪聲源導(dǎo)致的。在Virtex Ⅱ-PRO系列FPGA中,RocketIO模塊集中分布在上、下4個(gè)通道中,當(dāng)RocketIO工作在2.0 Gbaud以上時(shí),參考時(shí)鐘應(yīng)采用差分輸入方式(如LVDS、LVPECH),由上述4個(gè)通道的專用差分時(shí)鐘引腳輸入,至相同時(shí)鐘信號(hào)引入不必要的抖動(dòng),在2.0 Gbaud速率以下應(yīng)用時(shí),不要用FPGA內(nèi)部的DCM來生成RocketIO的輸入時(shí)鐘,因?yàn)榻?jīng)DCM倍頻的時(shí)鐘會(huì)引入較大的抖動(dòng),使RocketIO的接收鎖相環(huán)無法穩(wěn)定地鎖定發(fā)送時(shí)鐘,致使系統(tǒng)無法正常工作。

(2)復(fù)位

在Virtex Ⅱ-PRO系列FPGA中,RocketIO模塊的復(fù)位引腳分為發(fā)送(TX_RESET)和接收(RX_RESET)兩部分。由于DCM在輸出時(shí)鐘鎖定在設(shè)定值前,輸出時(shí)鐘處于不穩(wěn)定狀態(tài),不能用作內(nèi)部邏輯電路時(shí)鐘,所以要在DCM時(shí)鐘輸出鎖定有效,并經(jīng)過適當(dāng)延遲后才可將片內(nèi)邏輯復(fù)位。RocketIO模塊要求復(fù)位輸入至少保持2個(gè)USRCLK時(shí)鐘周期來完成內(nèi)部FIFO的初始化。

(3)PCB設(shè)計(jì)

在PCB的設(shè)計(jì)中,應(yīng)使差分線對(duì)內(nèi)的長(zhǎng)度相互匹配,以減少信號(hào)扭曲。為使設(shè)計(jì)傳輸速率達(dá)到2.0 Gbaud,在差分線對(duì)內(nèi)部每個(gè)走線區(qū)間內(nèi)的實(shí)際布線公差應(yīng)控制在5 mil內(nèi)。差分線對(duì)內(nèi)兩條線之間的距離應(yīng)盡可能小,以使外部干擾為共模特征。差分線對(duì)間的距離應(yīng)盡可能保持一致,以降低差分阻抗分布的不連續(xù)性。采用電源層作為差分線的信號(hào)回路,因?yàn)殡娫雌矫嬗凶钚〉膫鬏斪杩梗瑥亩鴾p少噪聲,由于每個(gè)過孔可帶來0.5-1.0dB的損耗,應(yīng)盡量減少過孔數(shù)目。過孔的通孔和焊盤應(yīng)有盡量小的物理尺寸,并且在通孔穿越的未連接不加焊盤,差分對(duì)內(nèi)的過孔不僅在數(shù)量上要匹配,而且在放置的位置上也要接近,以使阻抗分布盡量一致,避免導(dǎo)致阻抗不連續(xù)的90°走線,而要用圓弧或45°折線來代替。走線時(shí)應(yīng)使向左、向右折角的數(shù)量接近,這樣可減少信號(hào)經(jīng)差分線傳輸引起的扭曲。在模擬數(shù)字混合系統(tǒng)設(shè)計(jì)中,首先,應(yīng)在電源和地線之間加上去耦電容;其次,盡量加寬電源和地線寬度,最好是地線比電源線寬,使得地線寬度>電源線寬度>信號(hào)線寬度;第三,使用統(tǒng)一地,而將PCB分區(qū)為模擬部分和數(shù)字部分,模擬信號(hào)在電路板所有層的模擬區(qū)內(nèi)布線,而數(shù)字信號(hào)在數(shù)字電路區(qū)內(nèi)布線,在這種情況下,數(shù)字信號(hào)返回電流不會(huì)流入到模擬信號(hào)的地。經(jīng)過以上設(shè)計(jì),噪聲影響明顯降低。

4 接口解決方案

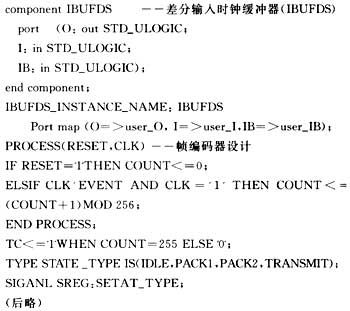

隨著高速數(shù)據(jù)傳輸業(yè)務(wù)需求的增加,如何高質(zhì)量地解決高速IC芯片的相互連接變得越來越重要,低功耗及高的信噪比是有待解決的主要問題。本文所介紹的高速采集系統(tǒng)中芯片間有兩種接口:PECL和LVDS,如何進(jìn)行兩接口相互連接就成為一個(gè)影響系統(tǒng)性能的關(guān)鍵因素,LVDS的輸入與輸出都是內(nèi)匹配的,所以LVDS間的連接可采用圖4所示的直接連接,在FPGA內(nèi),需對(duì)差分輸入時(shí)鐘緩沖器(IBUFDS),差分輸入的全局時(shí)鐘緩沖區(qū)(IBUFGDS)和差分輸出時(shí)鐘緩沖器(OBUFDS)例化,在本項(xiàng)目的應(yīng)用中,發(fā)送及接收FIFO的設(shè)計(jì)用了雙口塊內(nèi)存(Block RAM),時(shí)鐘倍頻器用了延遲鎖定環(huán)(DLL),幀解碼器由30位并行數(shù)據(jù)產(chǎn)生器、同步字檢測(cè)陣列和接收狀態(tài)機(jī)組成。

FPGA的部分代碼如下:

PECL間的連接一般常用直流耦合。在直流耦合情況下,PECL輸出設(shè)計(jì)驅(qū)動(dòng)50Ω負(fù)載至(VCC-2V),電路如圖5所示。

FPGA的部分代碼如下:

經(jīng)實(shí)際測(cè)試,輸入輸出指標(biāo)均符號(hào)系統(tǒng)要求,在硬件電路設(shè)計(jì)中,由于LVDS信號(hào)的偏置電壓為1.25V,電壓擺幅只有350mV,傳輸速率≥100Mb/s;因此,電路板制作至關(guān)重要,要求至少使用四層板。為使干擾信號(hào)以共模方式加到差分線對(duì)上(不影響數(shù)據(jù)正確性),要求差分線對(duì)間的距離盡可能小。電源方面,F(xiàn)PGA芯片上電時(shí)要求有大于500mA的驅(qū)動(dòng)電流,同時(shí),由于多個(gè)輸出引腳的電位速度變化,要求每對(duì)電源和地引腳都要良好旁路。

5 結(jié)論

本文給出了基于FPGA高速數(shù)據(jù)采集系統(tǒng)中的輸入輸出接口的實(shí)現(xiàn),介紹了高速傳輸系統(tǒng)中RocketIO設(shè)計(jì)以及LVDS接口、LVPECL接口電路結(jié)構(gòu)及連接方式,并在我們?cè)O(shè)計(jì)的高速數(shù)傳系統(tǒng)中得到應(yīng)用。RocketIO傳輸速度可以達(dá)到2.5Gbaud,LVDS總線上的傳輸速率可以達(dá)到120Mb/s,系統(tǒng)性能穩(wěn)定。