引言

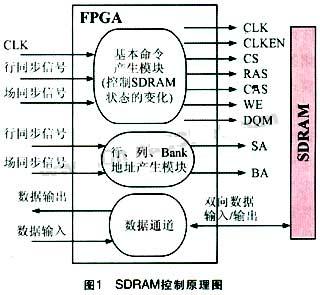

在信息處理中,特別是實(shí)時(shí)視頻圖像處理中,通常都要對實(shí)現(xiàn)視頻圖像進(jìn)行處理,而這首先必須設(shè)計(jì)大容量的存儲器,同步動(dòng)態(tài)隨機(jī)存儲器SDRAM雖然有價(jià)格低廉、容量大等優(yōu)點(diǎn),但因SDRAM的控制結(jié)構(gòu)復(fù)雜,常用的方法是設(shè)計(jì)SDRAM通用控制器,這使得很多人不得不放棄使用SDRAM而使用價(jià)格昂貴的SRAM。為此,筆者在研究有關(guān)文獻(xiàn)的基礎(chǔ)上,根據(jù)具體情況提出一種獨(dú)特的方法,實(shí)現(xiàn)了對SDRAM的控制,并通過利用FPGA控制數(shù)據(jù)存取的順序來實(shí)現(xiàn)對數(shù)字視頻圖像的旋轉(zhuǎn),截取、平移等實(shí)時(shí)處理。SDRAM的控制原理,如圖1所示。

SDRAM基本操作原理

本文以三星公司的SDRAM器件K4S561632C[4]為例來是說明SDRAM的工作原理。

SDRAM的結(jié)構(gòu)特點(diǎn)

存儲器的最初結(jié)構(gòu)為線性,它在任何時(shí)刻,地址線中都只能有一位有效。設(shè)容量為N×M的存儲器有S0-Sn-1條地址線;當(dāng)容量增大時(shí),地址選擇線的條數(shù)也要線性增多,利用地址譯碼雖然可有效地減少地址選擇線的條數(shù),但這種存儲器的長寬比太大,顯然,這在工業(yè)上是無法實(shí)現(xiàn)的。而且由于連線的延時(shí)與連線的長度成正比,這樣的設(shè)計(jì)會使存儲器的存取速度很慢。為了解決這個(gè)問題,現(xiàn)在常用的存儲器都是將存儲單元設(shè)計(jì)成陣列形狀,使其長寬比接近1:1。這樣,電路就必須增加一個(gè)列地址譯碼器,才能選出正確的存儲單元。這樣,整個(gè)存儲器的地址線被分為行地址線和列地址線,行地址線要將要選擇執(zhí)行讀或?qū)懖僮鞯男校械刂肪€則可從被選中的一行中再選出一個(gè)用于真正執(zhí)行讀或?qū)懖僮鞯拇鎯卧?br />

SDRAM的行地址線和列地址線是分時(shí)復(fù)用的,即地址線要分兩次送出,先送行地址線,再送列地址線。這樣可進(jìn)一步減少地址線的數(shù)量、提高器件的性能,但尋址過程會由此變得復(fù)雜,新型的SDRAM的容量一般比較大,如果還采用簡單的陣列結(jié)構(gòu),就會使存儲器的字線和位線的長度、內(nèi)部寄生電容及寄生電阻都變得很大,從而使整個(gè)存儲器的存取速度嚴(yán)重下降,實(shí)際上,現(xiàn)在SDRAM一般都以Bank(存儲體或存儲塊)為組織,來將SDRAM分為很多獨(dú)立的小塊,然而由Bank地址線BA控制Bank之間的選擇;SDRAM的行、列地址線貫穿所有的Bank;每個(gè)Bank的數(shù)據(jù)位寬同整個(gè)存儲器的相同。這樣,Bank內(nèi)的字線和位線的長度就可被限制合適的范圍內(nèi),從而加快存儲器單元的存取速度,另外,BA也可以使被選中的Bank處于正常工作模式,而使沒有被選中的Bank工作在低功耗模式下,這樣還可以降低SDRAM的功耗。

為了減少M(fèi)OS管的數(shù)量、降低功耗、提高集成度和存儲容量,SDRAM都是利用其內(nèi)部電容存儲信息,由于電容的放電作用,必須每隔一段時(shí)間給電容充電才能使存儲在電容里的數(shù)據(jù)信息不丟失,這就是刷新過程,這種機(jī)制使SDRAM的控制過程變的更加復(fù)雜,從而給應(yīng)用帶來難度。

三星公司的SDRAM(K4S561632C)的外部同步時(shí)鐘速率可在一定的頻率范圍內(nèi)連續(xù)變化,最高頻率可達(dá)到133MHz,每塊SDRAM內(nèi)含四個(gè)獨(dú)立的Bank;它的基本存儲單元都是按照陣列排列的,它的數(shù)據(jù)位寬和整個(gè)存儲器的位寬相同,同時(shí)支持多種讀寫模式;所有的輸入信號均以時(shí)鐘的上升沿為基準(zhǔn),這使得地址、控制和數(shù)據(jù)輸入到緩沖器的時(shí)間可保持一致且建立和保持的時(shí)間很小;該器件使用完全流水線型內(nèi)部結(jié)構(gòu);另外,它還具有突發(fā)長度可編程、延遲可編程等優(yōu)點(diǎn)。這些優(yōu)點(diǎn)使得K4S561632C能廣泛的應(yīng)用于寬頻帶、高性能存儲器應(yīng)用系統(tǒng)。

SDRAM的基本信號

SDRAM的基本信號可以分成以下幾類:

(1)控制信號:包括片選(CS)、同步時(shí)鐘(CLK)、時(shí)鐘有效(CLKEN)、讀寫選擇(WE)、數(shù)據(jù)有效(DQM)等;

(2)地址選擇信號:包括行地址選擇(RAS)、列地址選擇(CAS)、行/列地址線(SA0-SA12)分時(shí)復(fù)用、Bank塊地址線(BA0-BA1);

(3)數(shù)據(jù)信號:包括雙向數(shù)據(jù)端口(DQ0-DQ15)、接收數(shù)據(jù)有效信號(DQM)控制等。DQM為低時(shí),寫入/讀出有效。

對SDRAM的基本命令

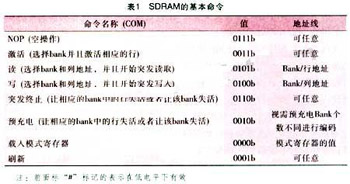

要正確的對SDRAM進(jìn)行操作,就需要輸入多種命令:包括模式寄存器設(shè)置、預(yù)充電、突發(fā)停止、空操作等命令。SDRAM內(nèi)部的狀態(tài)會根據(jù)表1的命令進(jìn)行轉(zhuǎn)移,其中,命令COM={CS#;RAS#;CAS#;WE#}。

模式寄存器的規(guī)定

利用模式寄存器(Mode Register)[5]可通過裝載模式寄存器命令(LOADMODE REGISTER)進(jìn)行

編程,這組信息將會一直保存在模式寄存器中,直到它再次被編程或器件掉電為止;它規(guī)定了SDRAM的操作模式,包括突發(fā)長度、突發(fā)類型、CAS延遲時(shí)間、運(yùn)行模式及寫突發(fā)模式、具體格式如圖2所示,模式寄存器M0-M2用于規(guī)定突發(fā)長度(Burst length)。M3用于規(guī)定突發(fā)類型BT(Burst Type),M3=0時(shí),突發(fā)類型是連續(xù)的;M3=1時(shí),突發(fā)類型是交錯(cuò)的,M4-M6用于規(guī)定CAS延遲的時(shí)鐘周期數(shù),M7-M8規(guī)定運(yùn)行模式,M9規(guī)定寫突發(fā)模式WB(Write Burst Mode),當(dāng)M9=0時(shí),按實(shí)際編程的突發(fā)長度存取,當(dāng)M9=1時(shí),則按單個(gè)存取單元寫入,但可按實(shí)際編程的突發(fā)長度讀出,M10和M11為保留位,可供未來使用。在模式寄存器裝載期間,地址A12(M12)必須被驅(qū)動(dòng)至低電平,本方案中,模式寄存器的值為ox220h。

初始化操作

SDRAM在上電以后必須先對其進(jìn)行初始化操作,而后才能對其進(jìn)行其他操作。出初始化操作具體步驟如下:

(1)SDRAM在上電以后需要等待100-200μs,在等待時(shí)間結(jié)束后還至少要執(zhí)行一條空操作命令;

(2)SDRAM執(zhí)行一條預(yù)充電命令后,要執(zhí)行一條空操作命令,這兩個(gè)操作會使所有的存儲單元進(jìn)行一次預(yù)充電,從而使所有陣列中的器件處于待機(jī)狀態(tài);

(3)SDRAM要執(zhí)行兩條自刷新命令,每一條刷新命令之后,都要執(zhí)行一條空操作命令,這些操作可使SDRAM芯片內(nèi)部的刷新及計(jì)數(shù)器進(jìn)入正常運(yùn)行狀態(tài),以便SDRAM為模式寄存器編程做好準(zhǔn)備;

(4)執(zhí)行加載模式寄存器(LOAD MODE REGISTER)命令,完成對SDRAM工作模式的設(shè)定。完成以上步驟后,SDRAM即可進(jìn)入正常工作狀態(tài),以等待外部命令對其進(jìn)行讀、寫、預(yù)充電和刷新等操作。

SDRAM的基本讀寫操作

SDRAM的基本讀操作[3]需要控制線和地址線相配合并發(fā)出一系列命令來完成。SDRAM的讀操作只有突發(fā)模式(Burst Mode);而寫操作則可以有突發(fā)寫和非突發(fā)寫兩種模式,具體如下:

(1)帶有預(yù)充電的突發(fā)讀寫模式,該模式一次能夠訪問的列地址的最大數(shù)為1、2、4、8;

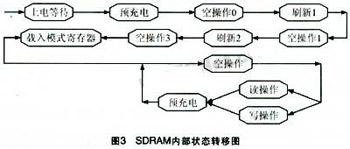

(2)不帶有機(jī)充電的全頁讀寫、此模式可任意控制一次能夠訪問的列地址的最大數(shù)。 根據(jù)實(shí)際情況,本設(shè)計(jì)只選取了與本方法相關(guān)的基本操作命令,并沒有設(shè)計(jì)通用的控制器,圖3是本方案的SDRAM內(nèi)部狀態(tài)轉(zhuǎn)移圖。

Bank乒乓操作

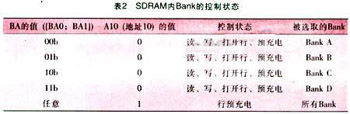

由于Bank內(nèi)的行與行之間具有關(guān)聯(lián)性,因此,當(dāng)其中一個(gè)Bank的讀或?qū)懖僮鹘Y(jié)束后,必須執(zhí)行一次預(yù)充電命令以關(guān)閉正在操作的行、預(yù)充電命令執(zhí)行后,會有一個(gè)tRP的延時(shí),延時(shí)完成后才能向同一Bank行(或其他行)發(fā)出新的激活命令。由于Bank之間是相互獨(dú)立的,因此,在一個(gè)Bank進(jìn)行正常的讀或?qū)懖僮鲿r(shí),可以對另外幾個(gè)Bank進(jìn)行預(yù)充電或空操作;當(dāng)一個(gè)Bank的進(jìn)行預(yù)充電期間也可以直接調(diào)用另一個(gè)已經(jīng)進(jìn)行預(yù)充電的Bank,而并不需要等待,具體的Bank控制過程要參考特定的器件數(shù)據(jù)手冊。三星公司的K4S561632內(nèi)的Bank控制狀態(tài)如圖2所列。

常用的三種尋址方式

K4S561632C器件的常用尋址方法有以下三種:

(1)頁命令中PH(Page Hit):若尋址的行與所在的Bank的空閑的,即該Bank內(nèi)所有的行是關(guān)閉的,那么此時(shí)便可直接發(fā)送行有效命令,這種情況下,數(shù)據(jù)讀取前的總耗時(shí)為tRCD+CL;(tRCD為RAS到CAS的延時(shí);CL為CAS latency)。

; (2)頁快速命中PFH(Page Fast Hit)或頁直接命中PDH(Page Direct Hit):如果要尋址的行正好是在正常讀或?qū)懀匆獙ぶ返男姓幱诒贿x通的有效狀態(tài),那么此時(shí)可直接發(fā)送列尋址命令,這種情況下,數(shù)據(jù)讀取前的總耗時(shí)僅為CL,這就是所謂的背靠背(Back to Back)尋址;

(3)頁錯(cuò)失PM(Bage Miss):若要尋址的行所在的Bank中已經(jīng)有一個(gè)行處于激活狀態(tài)(未關(guān)閉),這種現(xiàn)象而稱為尋址沖突,這樣,就必須要進(jìn)行預(yù)充電來關(guān)閉正在工作的行、然后再對其他的行發(fā)送行有效命令,其總耗時(shí)為:tRP+tRCD+CL。(tRP為Row precharge time)。

在以上三種尋址方式中,PFH是最理想的尋址方式,PM則是最糟糕的尋址方式,實(shí)際應(yīng)用中要盡量采用PFH尋址方式而應(yīng)避免采用PM尋址方式。

減少延遲的方法

自動(dòng)預(yù)充電技術(shù)是一種有效的減少延遲的方法,它通過自動(dòng)在每次行操作之后進(jìn)行預(yù)充電操作來減少對同一Bank內(nèi)的不同行尋址時(shí)發(fā)生沖突的可能性,但是,如果要在正在讀或?qū)懙男型瓿刹僮骱篑R上打開同一Bank的另一行時(shí),仍然存在tRP的延遲。 交錯(cuò)式控制是另一種更有效的減少延遲的方法,即在一個(gè)Bank工作時(shí),對另一個(gè)Bank進(jìn)行預(yù)充電或者尋址(此時(shí)要尋址的Bank是關(guān)閉的),預(yù)充電與數(shù)據(jù)的傳輸交錯(cuò)執(zhí)行,當(dāng)訪問下一個(gè)Bank時(shí),tRP已過,這樣就可以直接進(jìn)入行有效狀態(tài),如果配合得比較理想,那么就可以實(shí)現(xiàn)無間隔的Bank交錯(cuò)讀或?qū)懀虼耍珺ank之間的切換可使存儲效率成倍提高,并能夠大大地提高多組SDRAM協(xié)同工作時(shí)的性能。

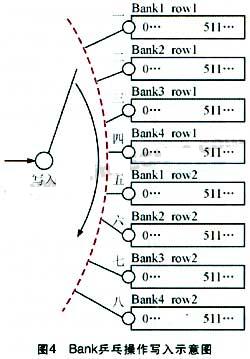

Bank乒乓操作寫入

一個(gè)由行、場同步信號控制的計(jì)數(shù)器在預(yù)定的時(shí)刻會產(chǎn)生一個(gè)控制信號,先發(fā)出激活相應(yīng)Bank的激活命令(ACTIVE),并鎖存相應(yīng)的Bank地址(由BA0、BA1給出)和行地址(由A0-A12給出)。一個(gè)周期后再給出列地址和寫入命令;在CL個(gè)周期后,便可將所需寫入的數(shù)據(jù)依次送到數(shù)據(jù)總線上,當(dāng)計(jì)數(shù)器的計(jì)數(shù)周期到達(dá)時(shí),系統(tǒng)會產(chǎn)生一個(gè)控制信號,并向SDRAM發(fā)送預(yù)充電(PRECHARGE)命令(如果使用了可編程長度,則在這前要使用突發(fā)終止命令),以關(guān)閉已經(jīng)激活的頁。在下一個(gè)視頻行同步信號來臨時(shí),系統(tǒng)將重復(fù)以上操作,并如此循環(huán)下去,具體操作如圖4所示,圖中左邊的一、二、三……為所對應(yīng)的視頻行同步信號,右邊1至511……則代表對應(yīng)的存儲器中的列地址(即是屏幕上對應(yīng)的像素的位置)。

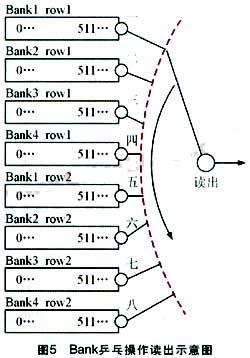

Bank乒乓操作讀出

由行、場同步信號控制的一個(gè)計(jì)數(shù)器可在預(yù)定的時(shí)刻產(chǎn)生一個(gè)控制信號,它首先發(fā)出相應(yīng)的Bank激活命令(ACTIVE),并鎖存相應(yīng)的Bank地址(由BA0、BA1給出)和行地址(由A0-A12)給出,然后在一個(gè)周期后給出列地址和讀命令,當(dāng)計(jì)數(shù)器的計(jì)數(shù)周期到達(dá)時(shí),系統(tǒng)會產(chǎn)生一個(gè)控制信號,并向SDRAM發(fā)出預(yù)充電(PRECHARGE)命令,以關(guān)閉已經(jīng)激活的頁(如果使用了可編程長度,則在這之前要使用突發(fā)終止命令)。之后,再在下一個(gè)視頻行同步信號來臨時(shí)重復(fù)以上操作,如此循環(huán)(具體操作如圖5),圖中左邊的一、二、三……為所對應(yīng)的視頻行同步信號,右邊1至511……代表對應(yīng)的存儲器中的列地址(即是屏幕上對應(yīng)的像素的位置。

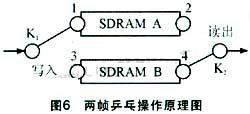

場乒乓操作

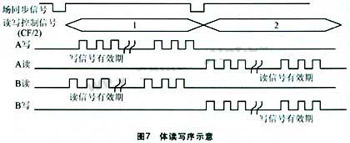

為了SDRAM能正確進(jìn)行讀和寫兩個(gè)操作,本方案選用兩場乒乓操作[6]來實(shí)現(xiàn)數(shù)據(jù)存取,實(shí)際上,就是在不同的時(shí)間對兩場輪換進(jìn)行讀或?qū)懀粓鲎x而另一場寫,其原理如圖6所示。當(dāng)開關(guān)K1在1位置,K2在4位置是時(shí),A寫B(tài)讀;反之,當(dāng)開關(guān)K1在3位置,K2在2位位置時(shí),A讀B寫。如此循環(huán)往復(fù)。

若以場同步信號的二分頻計(jì)數(shù)器F/2為讀寫控制信號,假設(shè)SDRAM A在F/2時(shí)為1寫、2讀,則SDRAM B在F/2時(shí)為2寫、1讀,兩場即為一個(gè)場乒乓操作周期,讀寫信號均在場同步信號為高電平時(shí)有效,由于存在消隱期,消音所以,將會有一段時(shí)間讀寫都無效(讀寫信號都是低電平,此時(shí)SDRAM進(jìn)入預(yù)充電狀態(tài)),其總體時(shí)序如圖7所示。

結(jié)束語

SDRAM的控制過程雖然很復(fù)雜,但如果根據(jù)實(shí)際情況進(jìn)行取舍以滿足實(shí)際系統(tǒng)要求,那么,SDRAM的控制過程還是比較簡單的,在實(shí)驗(yàn)中,使用ALTERA公司的Cyclone FPGA器件進(jìn)行設(shè)計(jì)時(shí),程序設(shè)計(jì)可采用Verilog語句來實(shí)現(xiàn)對實(shí)時(shí)視頻信號的采集,并通過改變計(jì)數(shù)器的周期及SDRAM的行、列地址線和時(shí)序就可以對任意位置的視頻圖像進(jìn)行平移、旋轉(zhuǎn)、截取等處理,此外,由于程序設(shè)計(jì)采用了化整為零和參數(shù)化設(shè)計(jì)思想,因而結(jié)構(gòu)透明、簡單;對于特定容量的SDRAM的特定工作模式而言,該方法只需根據(jù)器件重新設(shè)定參數(shù)而不要重新編寫程序,因而具有較強(qiáng)的通用性。