現(xiàn)代無線通信系統(tǒng)中,越來越大的業(yè)務量與越來越少的頻率資源之間的矛盾顯著,而且以視頻、數(shù)據(jù)為主的通信內(nèi)容使得在分配信道資源時留給話音業(yè)務的資源非常有限,采用G.729A低速率的話音編碼技術(shù)可降低編碼速率,提高頻率利用率。

ML7204專用語音處理器可提供多種速率的編解碼功能,包括A律和U律2種不同的PCM和G.729A低速壓縮話音編解碼。該器件內(nèi)置FIF0緩存器,具有合成語音質(zhì)量高、抗誤碼性能好等特點,并在語音通信,特別是VoIP系統(tǒng)中應用廣泛。基于8051構(gòu)架的開源微處理器內(nèi)核PicoBlaze配合FPGA解決常量編碼可編程狀態(tài)機(KCPSM)問題,可以使系統(tǒng)同時具備處理復雜控制和時序邏輯的能力。這里介紹了ML7204的基本性能和工作原理,微處理器內(nèi)核PicoBlaze的開發(fā)流程及其使用方法,并且給出通過PicoBlaze配置、控制ML7204實現(xiàn)單路G.729A語音編解碼的系統(tǒng)設(shè)計方案。

1 ML7204功能簡介

ML7204具有如下特點:內(nèi)置640字節(jié)FIF0,為數(shù)據(jù)收發(fā)提供緩存;支持ITU的G.711、G.729A等分組語音處理標準;回音抵消和抑制、靜音檢測和舒適噪音等提高分組語音處理性能;收、發(fā)增益控制;以數(shù)據(jù)、地址總線方式訪問控制寄存器。

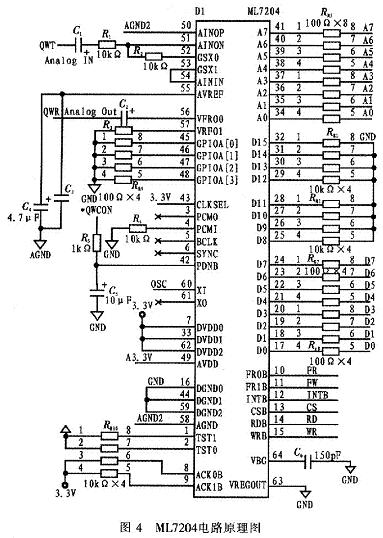

ML7204分組語音處理器件的接口是從硬件連接和功能兩方面考慮,包括語音、PCM、中斷、時鐘、處理器等接口。其中,語音接口(Voice I/F)模擬話音信號的輸入輸出,內(nèi)置可調(diào)增益放大器和A/D和D/A轉(zhuǎn)換器;PCM接口(PCM I/F)用于非壓縮語音信號的輸入輸出,為64 kb/s率或a率壓擴的PCM信號;中斷接口(INT I/F)提供異常狀況的信號指示;時鐘接口(CLK I/F)既可外置晶體,也可直接輸入時鐘信號,時鐘頻率12.288 MHz;處理器接口(MCU I/F)包括8位數(shù)據(jù)、地址總線以及讀、寫使能、片選信號,實現(xiàn)微處理器與ML7204的通信,并實現(xiàn)微處理器對ML7204的控制、以及ML7204的狀態(tài)檢測。ML7204有復位、初始化配置、運行3種工作模式,如圖1所示。ML7204上電后,復位信號有效(PDNB=0)時,內(nèi)核重啟,則ML7204進入復位模式(Power Down State);初始化配置模式(Initial State)是當復位信號釋放(PDNB=1)時,所有狀態(tài)重置等待處理器配置。處理器通過修改控制寄存器完成器件的初始化配置;初始化完成后器件進入運行模式(OperationState),開始正常運行,此時通過設(shè)置PDNB或控制寄存器的軟復位信號使ML7204重新進入復位模式等待初始化。

2 微處理器內(nèi)核PicoBlaze簡介

PicoBlaze的特點如下:Xilinx公司專為Virtex、Spartan系列FPGA和CoolRunner系列CPLD設(shè)計的嵌入式專用8位微處理器IP Core;占用邏輯資源少,只占96 slices(Sparta-3X(22S200E資源的5%):運行速度快,最高可達40 MI/s;指令集豐富,包括邏輯操作、輸入,輸出、算術(shù)運算等指令;開源、免費的編譯器kcpsm3。

PicoBlaze微處理器接口從數(shù)據(jù)和控制兩方面考慮,包括復位、時鐘、讀信號、寫信號、數(shù)據(jù)輸入、數(shù)據(jù)輸出等接口。如圖2所示。

復位接口(reset)是異步復位、高有效、清除PicoBlaze內(nèi)核所有狀態(tài),但不清除程序代碼;時鐘接口(clk)是輸入主時鐘,最高速率35 MHz;地址總線接口(port_id[7:0])為PicoBlaze內(nèi)核的地址總線,持續(xù)2個時鐘節(jié)拍有效;數(shù)據(jù)總線接口(out_port[7:0])是PicoBlaze內(nèi)核的數(shù)據(jù)總線,持續(xù)2個時鐘節(jié)拍有效;讀信號接口(read_strobe)是讀脈沖信號,當該信號為高時,port_id[7:0]輸出有效數(shù)據(jù);寫信號接口(write_strobe),寫脈沖信號,當該信號為高時,port_id[7:O]輸入有效數(shù)據(jù)。

3 系統(tǒng)硬件設(shè)計

圖3為基于PicoBlaze軟核處理器和ML7204編解碼器的單路低速話音編解碼系統(tǒng)的框圖。

該系統(tǒng)主要由話音信號處理、系統(tǒng)邏輯控制、傳輸復分接、時鐘處理4個單元組成。其中,話音信號處理單元主要由ML7204和簡單外圍器件組成,完成模擬話音信號與G.729A壓縮編碼信號之間的相互轉(zhuǎn)換;系統(tǒng)邏輯控制單元由PicoBlaze內(nèi)核組成,完成與ML7204的數(shù)據(jù)傳輸;傳輸復分接單元由FPGA片內(nèi)邏輯單元組成,完成拆、組幀及并、串轉(zhuǎn)換。時鐘處理單元為ML7204提供高穩(wěn)定時鐘信號。

由話機模擬電路輸出的模擬話音信號經(jīng)話音信號處理單元,實現(xiàn)PCM編碼、G.729A壓縮編碼,再通過并行MCU I/F接口輸出速率為8 kHz的G.729A壓縮編碼數(shù)據(jù),系統(tǒng)邏輯控制單元讀取壓縮編碼數(shù)據(jù),并送往傳輸復分接單元,進行組幀、并串轉(zhuǎn)換,最終輸出成幀的串行碼流。相應地成幀的串行碼流先進入傳輸復分接單元進行幀同步檢測,讀取真正的話音數(shù)據(jù),串并轉(zhuǎn)換后,再傳輸至系統(tǒng)邏輯控制單元,由PicoBl-aze內(nèi)核將并行話音數(shù)據(jù)發(fā)送至話音信號處理單元,話音數(shù)據(jù)經(jīng)解壓縮、PCM解碼,恢復模擬話音信號。

ML7204的數(shù)據(jù)傳輸采用總線方式,即A[7:0]、D[7:0]分別是8位數(shù)據(jù)、地址總線;FROB、FRlB、INTB、CSB、RDB、WRB分別為讀使能、寫使能、中斷、片選、讀信號、寫信號。ML7204有10 ms幀和20 ms幀兩種數(shù)據(jù)幀格式,這里采用10 ms幀格式。ML7204以10 ms為周期全雙工并行工作。每隔10 ms,ML7204拉低讀使能信號FROB,表示已經(jīng)準備好完整的一幀數(shù)據(jù),外部PicoBlaze微處理器通過連續(xù)10次拉低片選信號CSB、讀信號RDB讀出一幀數(shù)據(jù)。相應,每隔10 ms,ML7204拉低寫使能信號FRlB,表示解碼處理新的一幀數(shù)據(jù),外部PicoBlaze微處理器可以通過連續(xù)10次拉低片選信號CSB、寫信號WRB寫入一幀數(shù)據(jù)。圖4是ML7204電路原理圖。

4 系統(tǒng)軟件設(shè)計

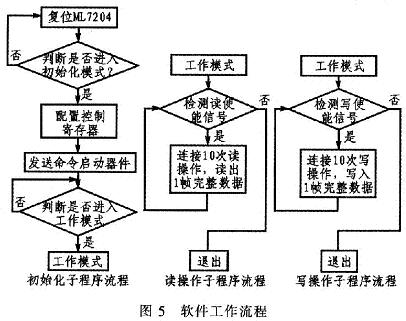

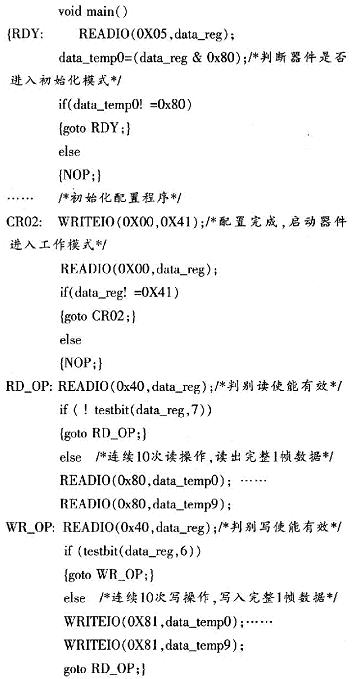

該系統(tǒng)軟件主要是對ML7204初始化配置、工作狀態(tài)控制.ML7204的配置方式是修改控制寄存器。工作時,F(xiàn)PGA內(nèi)嵌PicoBlaze內(nèi)核首先對ML7204復位,復位成功后,PicoBlaze內(nèi)核通過MCU I/F接口修改控制寄存器,設(shè)置其工作方式,包括語音編碼方式、語音信號幅度、數(shù)據(jù)幀長度等,最后FPGA內(nèi)部邏輯處理單元配合PicoBlaze內(nèi)核完成分組語音數(shù)據(jù)的讀寫及傳輸。ML7204共有48個控制寄存器CR0~CR47,分別對應于地址00H~2FH,每個控制寄存器有8 bit數(shù)據(jù),分別標識不同的配置選項。保留地址80H、81H分別對應分組話音編解碼數(shù)據(jù)的讀、寫地址。圖5為軟件工作流程。

以下給出軟件程序的核心代碼:

5 結(jié)束語

ML7204是一個功能強大的語音信號處理器,可提供多種速率語音編解碼功能,操作方便。PicoBlaze是一個典型的8位軟核處理器,便于在各種FPGA上實現(xiàn),設(shè)計靈活。本文采用PicoBlaze與ML7204協(xié)同工作。構(gòu)建低速率語音通信的編解碼系統(tǒng)。相比傳統(tǒng)的語音編解碼系統(tǒng)設(shè)計方案,此方案無需單獨微處理器、Flash、SDRAM、PCM編解碼等器件,只需單片ML7204和單片小容量FPGA即可完成全部功能,設(shè)計簡單、成本低廉、合成語音質(zhì)量高,能有效提高帶寬利用率,在頻帶有限的無線通信系統(tǒng)中具有較大優(yōu)勢。

電路設(shè)計時需特別注意:考慮模擬信號與數(shù)字信號的隔離,應減少數(shù)字噪聲對模擬話音的干擾,減少背景噪聲。PicoBlaze微處理器初始化配置ML7204的控制寄存器時會出現(xiàn)錯誤。為避免錯誤配置,應在每次修改控制寄存器后讀回此控制寄存器的值,并判別是否與預期一致。若一致則配置下一個控制寄存器,否則繼續(xù)配置,直到一致為止。