1 引言

隨著網(wǎng)絡(luò)和多媒體" title="多媒體">多媒體技術(shù)的發(fā)展,視覺(jué)通信的重要性和需求急劇增加,如桌面視頻會(huì)議、移動(dòng)終端、基于因特網(wǎng)的視頻通信等。這些視覺(jué)信息內(nèi)涵豐富,但數(shù)據(jù)量大,必須壓縮數(shù)據(jù)。但采用多種方法壓縮圖像數(shù)據(jù),其數(shù)據(jù)量仍然巨大,這就對(duì)計(jì)算機(jī)處理速度、傳輸介質(zhì)、傳輸方法和存儲(chǔ)介質(zhì)提出較高要求。因此,數(shù)據(jù)壓縮作為數(shù)據(jù)圖像處理的關(guān)鍵技術(shù)之一,對(duì)研究圖像壓縮編碼技術(shù)具有重要價(jià)值。

嵌入式微處理器中,DSP" title="DSP">DSP具有靈活、高速、便于嵌入式應(yīng)用等優(yōu)點(diǎn),特別適合復(fù)雜算法處理的應(yīng)用。數(shù)字視頻圖像壓縮系統(tǒng)利用DSP作為其嵌入式平臺(tái),充分發(fā)揮其性能優(yōu)勢(shì),較好地提高編碼效率,滿足圖像實(shí)時(shí)處理需要。因此,這里介紹一種基于TMS320VC5509A型DSP的視頻壓縮" title="視頻壓縮">視頻壓縮系統(tǒng)。

2 靜止圖像的壓縮編碼標(biāo)準(zhǔn)JPEG

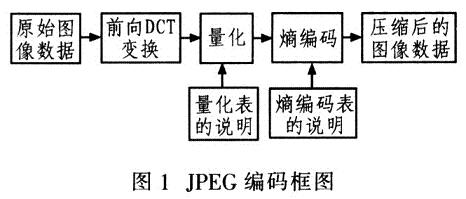

JPEG" title="JPEG">JPEG(Joint Photographic Experts Group)是由國(guó)際標(biāo)準(zhǔn)化組織(ISO)提出面向靜止圖像編碼的標(biāo)準(zhǔn),其處理方法依次使用離散余弦變換、量化、Z行掃描、游程編碼和不變字長(zhǎng)編碼。JPEG算法定義了以下4種運(yùn)行模式:

(1)基于DCT順序型模式按照從左到右、從上到下的順序?qū)D像進(jìn)行掃描和編碼,稱為基本系統(tǒng)。

(2)基于DCT遞增模式 按照從粗到細(xì)的順序?qū)σ环鶊D像進(jìn)行編碼,適用于傳輸時(shí)間長(zhǎng)、用戶喜歡圖像從粗糙到清晰的場(chǎng)合。

(3)無(wú)失真編碼模式保證重建圖像與原始圖像完全相同。

(4)分層編碼 采用各種分辨率對(duì)圖像進(jìn)行編碼。

該系統(tǒng)采用基本系統(tǒng)模式。圖1是JPEG的編碼框圖。

3 硬件系統(tǒng)設(shè)計(jì)

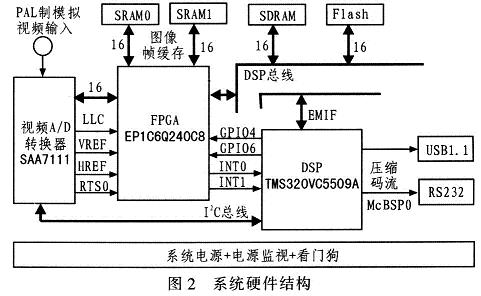

該視頻壓縮系統(tǒng)直接與PAL制攝像頭的輸出端相連,來(lái)采集、預(yù)處理和壓縮現(xiàn)場(chǎng)圖像,再以USB或RS232方式將處理后的圖像數(shù)據(jù)傳給上位機(jī)。圖2為視頻壓縮系統(tǒng)硬件結(jié)構(gòu)圖。

該系統(tǒng)硬件設(shè)計(jì)以TI公司的TMS320VC5509A型數(shù)字信號(hào)處理器為核心,包括視頻采集電路、FPGA預(yù)處理電路、存儲(chǔ)器擴(kuò)展、系統(tǒng)電源和看門狗電路等。系統(tǒng)中TMS320VC5509A為中央處理器;SDRAM為DSP外擴(kuò)數(shù)據(jù)存儲(chǔ)器;Flash為程序存儲(chǔ)器,用于系統(tǒng)上電自舉;模擬攝像頭與視頻 A/D轉(zhuǎn)換器負(fù)責(zé)視頻圖像采集;FPGA用于地址譯碼、隔行運(yùn)算,控制兩片SRAM用于緩存視頻A/D轉(zhuǎn)換器轉(zhuǎn)換后的數(shù)字圖像。從系統(tǒng)設(shè)計(jì)成本考慮,這里選用Altera公司的可編程邏輯器件EPIC6Q240C8型FPGA。該器件是Cyclone系列器件中一款非BGA封裝的可用I/O引腳最多的 FPGA。

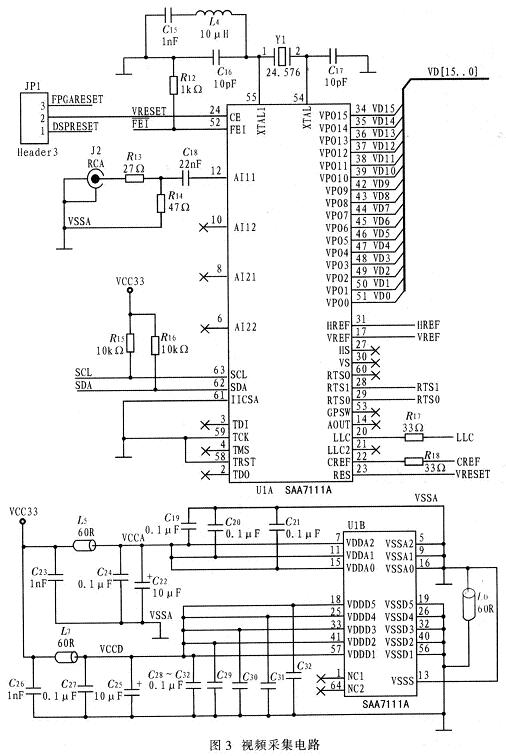

3.1 視頻采集電路

該系統(tǒng)選用的視頻解碼器為Philip公司的高性能視頻A/D轉(zhuǎn)換器SAA7111。該器件是一款廣泛應(yīng)用于桌面視頻、多媒體、數(shù)字電視、圖像處理、視頻電話的高性能視頻輸入處理器件。該器件采用3.3 V的CMOS電路,高度集成模擬前端和數(shù)字視頻編碼器;包括2路模擬視頻處理通道,1個(gè)時(shí)鐘產(chǎn)生電路,1個(gè)自動(dòng)箝位和自動(dòng)增益控制電路,1個(gè)多制式數(shù)字解碼器,1個(gè)亮度/對(duì)比度/飽和度控制電路,以及色彩空間矩陣。SAA7111輸出為16位VPO總線,支持不同位寬的數(shù)據(jù)輸出格式。SAA7111支持的輸出格式包括:12位YUV411,16位YUV4:2:2,8位CCIR-656、16位565RGB以及24位的888RGB。圖3為視頻采集電路。

3.2 存儲(chǔ)器選型

選擇存儲(chǔ)器應(yīng)從以下方面考慮:首先圖像壓縮算法中間數(shù)據(jù)量大,要求處理器的片上內(nèi)存盡可能大,盡量避免對(duì)外部存儲(chǔ)器讀寫(xiě)操作。VC5509A的片上存儲(chǔ)器包括32 Kx16位DARAM,96 Kx16位SARAM,共128 K位的存儲(chǔ)空間。其中DARAM為雙地址,在每個(gè)周期內(nèi)可以對(duì)其進(jìn)行兩次操作(2次讀,兩次寫(xiě),一次讀和一次寫(xiě)),這樣大大增加片上存儲(chǔ)器的利用率;其次,VC5509A片上資源豐富,包括I2C總線(多主從接口),3個(gè)McBSPs(1個(gè)與多媒體卡/數(shù)字加密卡MMC/SD串行接口復(fù)用引腳)。利用 FC總線對(duì)SAA7111的片內(nèi)控制寄存器進(jìn)行讀寫(xiě)操作,非常方便實(shí)時(shí)控制SAA711 1的工作狀態(tài);利用McBSP配合DMA,軟件編程實(shí)現(xiàn)UART功能,無(wú)需專門的硬件UART,從而節(jié)省電路板空間:VC5509A采用144引腳 LQFP封裝,便于安裝、調(diào)試;VC5509A功耗小,工作在200 MHz主頻下,功耗僅100 mW,非常適合嵌入式應(yīng)用。

3.3 DSP供電電源電路

DSP基本系統(tǒng)由獨(dú)立的電源系統(tǒng)供電,而硬件平臺(tái)的其他器件共用另一套電源供電系統(tǒng)。為了降低系統(tǒng)功耗,DSP一般采用低電壓供電.并且采用I/O和 CPU內(nèi)核分開(kāi)供電方式。VC5509A不同的工作頻率要求不同的核電壓,200 MHz為1.6 V,144 MHz為1.35 V,108 MHz為1.2 V。DSP的I/O電壓為3.3 V。

DSP供電電源電路如圖4所示。選用TI公司的兩款LDO電源器件TPS76801和TPS75833分別為DSP提供內(nèi)核電壓和I/O電壓。

TPS76801能給CPU內(nèi)核提供最大1 A的電流,電壓在1.2~3 V范圍內(nèi)可調(diào)。

調(diào)整TPS76801的輸入電阻值得到1.6 V,1.35 V,1.2 V的核電壓,DSP相應(yīng)工作在200 MHz,144 MHz,108 MHz的頻率下。而TPS75833能提供最高3 A的I/O電流,對(duì)于低功耗的TMS320VC5509A,這已足夠保證其工作在最大負(fù)荷狀態(tài)。

4 系統(tǒng)軟件設(shè)計(jì)

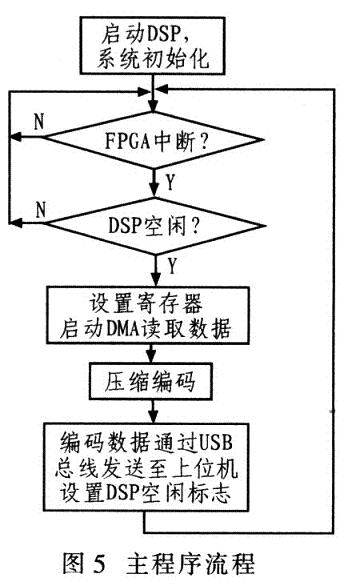

該系統(tǒng)軟件設(shè)計(jì)的主要功能是實(shí)時(shí)采樣現(xiàn)場(chǎng)的視頻信號(hào),然后對(duì)網(wǎng)像數(shù)據(jù)編碼壓縮并通過(guò)USB總線或RS232串口將圖像數(shù)據(jù)傳送給主機(jī)。系統(tǒng)主程序流程如圖5所示,該系統(tǒng)軟件設(shè)計(jì)可分為系統(tǒng)初始化、圖像采集、壓縮編碼和數(shù)據(jù)傳輸4個(gè)主要模塊。

系統(tǒng)上電后,DSP首先初始化,初始化主要包括:通過(guò)I2C總線初始化SAA7111,設(shè)置其工作模式;空間分配,EMIF的配置以保證外部存儲(chǔ)器的正常訪問(wèn);配置USB模塊;設(shè)定DMA通道以及設(shè)定外部中斷。然后DSP等待FPGA的中斷。當(dāng)DSP接收到FPGA的中斷后,DSP設(shè)定標(biāo)志寄存器,啟動(dòng) DMA讀取數(shù)據(jù),并進(jìn)行編碼。當(dāng)編碼結(jié)束后,DSP把數(shù)據(jù)交付USB模塊,通過(guò)USB總線傳送至上位機(jī),同時(shí)DSP向FPGA發(fā)送空閑信號(hào),通知FPGA 繼續(xù)發(fā)送下一幀。

5 JPEG優(yōu)化

JPEG算法在DSP上實(shí)現(xiàn)需要解決編碼速度問(wèn)題。片上內(nèi)存資源的有限性使得大部分的程序代碼和數(shù)據(jù)不得不放在片外,大量的圖像數(shù)據(jù)在慢速的SDRAM存儲(chǔ)器中,對(duì)其訪問(wèn)和算術(shù)運(yùn)算是影響系統(tǒng)性能的關(guān)鍵因素之一。因此,應(yīng)從內(nèi)存分配和代碼優(yōu)化兩個(gè)方面來(lái)優(yōu)化程序,提高編碼效率。

5.1 數(shù)據(jù)內(nèi)存優(yōu)化

由于VC5509A的片上存儲(chǔ)器包括32 Kx16位DARAM,96 Kx16位SARAM,共128 K位的存儲(chǔ)空間。其中DARAM為雙訪問(wèn)內(nèi)存,即在一個(gè)周期內(nèi)可完成兩次數(shù)據(jù)訪問(wèn),SARAM為單訪問(wèn)內(nèi)存,即在一個(gè)周期內(nèi)只能完成一次數(shù)據(jù)訪問(wèn),片外內(nèi)存為擴(kuò)展的SDRAM,訪問(wèn)其需要額外的等待時(shí)間,執(zhí)行效率比較低。因此在算法設(shè)計(jì)中應(yīng)合理安排內(nèi)存分配,盡量將訪問(wèn)頻繁的程序代碼和數(shù)據(jù)放在片內(nèi)內(nèi)存中,特別是DARAM中,可以提高編碼效率。

5.2 C代碼優(yōu)化

在JPEG的編碼中,根據(jù)VC5509A結(jié)構(gòu)特點(diǎn)及結(jié)合圖像數(shù)據(jù)量大的特點(diǎn),提高編碼效率,考慮程序編寫(xiě)和優(yōu)化如下:

(1)利用編譯器優(yōu)化,開(kāi)啟編譯器的優(yōu)化選項(xiàng),包括基本優(yōu)化、文件級(jí)優(yōu)化和程序級(jí)優(yōu)化。

(2)使用本征(intrinsics)函數(shù),C55x提供了一種特殊函數(shù)一本征函數(shù),可迅速優(yōu)化C代碼。本征甬?dāng)?shù)前有個(gè)下劃線“一”,調(diào)用方法和普通函數(shù)相同。

(3)使用圖像庫(kù),TI提供基于C55x的圖像庫(kù)IMGLIB,庫(kù)中都是圖像處理常用的函數(shù),而且可以用C語(yǔ)言調(diào)用,匯編優(yōu)化好,執(zhí)行效率高,因此盡量用庫(kù)函數(shù)。在JPEG編碼中比較關(guān)鍵的是DCT變換可調(diào)用庫(kù)函數(shù)中的IMG_sw_fdct_8x8(short*fdct_data,short, *inter_buffer),該函數(shù)完成一次DCT變換需用1 078個(gè)時(shí)鐘周期。大大提高JPEG的編碼效率。

(4)高效使用MAC硬件,C55x有專門的硬件高效執(zhí)行MAC運(yùn)算。一個(gè)周期中可以執(zhí)行一個(gè)單乘加或一個(gè)雙乘加(dual-MAC)運(yùn)算。

(5)使用特殊數(shù)據(jù)類型(register類型、volatile類型、const類型),對(duì)于需要多次重復(fù)訪問(wèn)的變量,如for循環(huán)中的變量值,一般可設(shè)置為register型變量。聲明變量為register型能提高效率,但必須小心使用。在某些編譯器中,優(yōu)化器會(huì)自動(dòng)分配一些變量為register 型。

(6)減少判斷循環(huán),在使用判斷方式選取控制語(yǔ)句時(shí)應(yīng)盡量減少判斷轉(zhuǎn)移。DSP多采用流水線結(jié)構(gòu)。由于TMS320C55X采用7級(jí)流水線結(jié)構(gòu),頻繁的轉(zhuǎn)移指令使得流水線難以發(fā)揮作用。

另外。DSP的大多數(shù)指令為單周期指令,但轉(zhuǎn)移類指令卻通常要耗費(fèi)較多的機(jī)器周期。因此,應(yīng)盡可能減少程序中的轉(zhuǎn)移分支,以提高程序的效率。

6 實(shí)驗(yàn)結(jié)果

6.1 壓縮效果實(shí)驗(yàn)結(jié)果

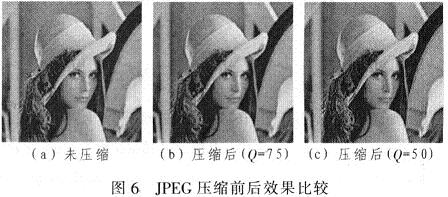

通過(guò)改變量化因子Q,改變圖像的壓縮比。壓縮比越大,壓縮過(guò)程中的視覺(jué)損失越大,壓縮后的圖片越不清晰。圖6為采用不同的量化因子Q的壓縮前后效果比較圖。其中,圖6a為未壓縮,大小57.4 KB的原始BMP圖像,圖6b為壓縮后大小為5.18 KB的圖像,圖6c為壓縮后大小5.18 KB的圖像。由圖知,壓縮后的圖像與原始圖像在視覺(jué)效果上相差不大。當(dāng)Q=50時(shí),壓縮后圖像所需存儲(chǔ)空間僅為原圖像的1/14。

6.2 壓縮耗時(shí)實(shí)驗(yàn)結(jié)果

對(duì)于一個(gè)8x8數(shù)據(jù)塊,各步耗時(shí)如下:分塊:1.335μs;DCT變換:5. 39μs;量化:1.355μs;哈夫曼編碼:3.375μs。說(shuō)明一個(gè)8x8數(shù)據(jù)塊總耗時(shí)為11.455μs,一幀720x576灰度圖像的壓縮總耗時(shí)為90x72x11.455=74 228.4μs,再加上其他輔助操作,實(shí)際耗時(shí)約75 ms。根據(jù)上述結(jié)果,在1 s內(nèi)向上位機(jī)發(fā)送13幀720x576的灰度圖像,基本滿足系統(tǒng)要求。

7 結(jié)束語(yǔ)

介紹基于TMS320VC5509A DSP的JPEG視頻壓縮系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn)方案,該系統(tǒng)硬件設(shè)計(jì)采用DSP+FPGA的方案,充分發(fā)揮了各自優(yōu)勢(shì);而軟件設(shè)計(jì)針對(duì)C55x的結(jié)構(gòu)進(jìn)行程序結(jié)構(gòu)和算法優(yōu)化,經(jīng)過(guò)驗(yàn)證達(dá)到較好的實(shí)時(shí)效果。由于該系統(tǒng)體積小、功耗低,適用于一些野外圖像采集、遠(yuǎn)程視頻監(jiān)控等需要連續(xù)傳輸圖像的場(chǎng)合。