引 言

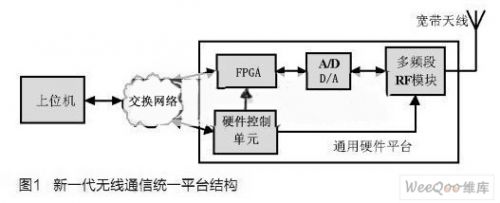

隨著通信技術(shù)的快速發(fā)展,無線通信體制呈現(xiàn)多樣化趨勢,各種通信系統(tǒng)之間互不兼容、升級能力有限等問題越來越突出。為了有效解決上述問題,清華大學(xué)無線與移動(dòng)通信技術(shù)研究中心在承擔(dān)的國家863項(xiàng)目“軟硬件可重構(gòu)的新一代無線通信統(tǒng)一平臺研究”中,以上位機(jī)、通用硬件平臺和寬帶天線等為基礎(chǔ),搭建一個(gè)可以兼容多種通信體制的新一代無線通信統(tǒng)一平臺,并通過運(yùn)行GSM、TD-SCDMA、WCDMA、CDMA2000、WiMAX等主流2G/3G/B3G無線通信系統(tǒng),驗(yàn)證平臺的可行性。該平臺結(jié)構(gòu)如圖1所示。其中,上位機(jī)提供人機(jī)界面,并完成基帶信號處理和系統(tǒng)整體控制;通用硬件平臺主要完成上下變頻、數(shù)模模數(shù)轉(zhuǎn)換、同步等信號預(yù)處理功能。

針對需要兼容多種通信體制的新一代無線通信統(tǒng)一平臺,傳統(tǒng)的時(shí)間同步算法由于對載波頻偏過于敏感、捕獲時(shí)間長等問題[2-4],無法滿足各種無線通信體制對時(shí)間同步算法的性能需求。介紹了一種基于前導(dǎo)字的快速位同步算法,但它只適用于在每個(gè)數(shù)據(jù)包前都插入前導(dǎo)字的突發(fā)通信系統(tǒng),且一般所需較長的前導(dǎo)字。介紹了一種可以減輕載波頻偏影響的幀同步算法,但它針對中國數(shù)字廣播電視系統(tǒng)設(shè)計(jì),不適用于其他通信體制,而且存在算法硬件實(shí)現(xiàn)復(fù)雜、沒有考慮位同步的實(shí)現(xiàn)等問題。

為了解決上述問題,本文提出了一種基于同步序列的時(shí)間同步算法,只需要修改本地同步序列就可以應(yīng)用于不同的通信系統(tǒng)。其中,幀同步分成檢測和確認(rèn)兩個(gè)步驟,并通過采用改進(jìn)的分段相關(guān)法解決幀同步對載波頻偏過于敏感以及硬件實(shí)現(xiàn)復(fù)雜度高等問題;而位同步同樣利用同步序列實(shí)現(xiàn),與幀同步同時(shí)完成,從而解決位同步算法收斂速度慢的問題,使算法滿足各種主流無線通信體制對時(shí)間同步算法的性能需求。

適用多體制通信的時(shí)間同步算法

為了解決傳統(tǒng)時(shí)間同步算法不適用于多種無線通信體制且不適于硬件實(shí)現(xiàn)等問題,本文提出了一種改進(jìn)的時(shí)間同步算法,如圖2所示。在改進(jìn)的時(shí)間同步算法中,本地同步序列分成和兩段,從而使幀同步和位同步都可以利用接收序列與本地同步序列的相關(guān)性實(shí)現(xiàn)。因此,只需要改變本地同步序列,改進(jìn)后的時(shí)間同步算法就可以適用于不同的通信體制。

在本地同步序列及其劃分方式確定后,時(shí)間同步算法的工作原理如下:首先,系統(tǒng)利用本地同步序列1完成幀同步的初始檢測。當(dāng)檢測結(jié)果認(rèn)為接收到數(shù)據(jù)幀時(shí),啟動(dòng)幀同步確認(rèn)和位同步等模塊,利用本地同步序列2完成幀同步確認(rèn)和位同步調(diào)整。其中,幀同步檢測使用改進(jìn)的分段相關(guān)法,可以有效提高幀檢測算法對載波頻偏的容忍度,降低幀同步的漏同步概率,并使算法便于硬件實(shí)現(xiàn)。幀同步確認(rèn)和位同步在幀同步檢測成功后啟動(dòng),通過本地同步序列2與接收序列的相關(guān)結(jié)果來確認(rèn)幀同步檢測結(jié)果是否正確,從而減少假同步概率,并同時(shí)利用接收序列與本地同步序列2之間的相關(guān)性完成位同步處理,大大加快了位同步的收斂速度。

幀同步檢測

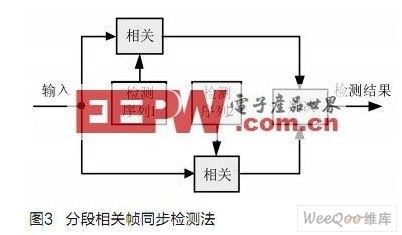

根據(jù)文獻(xiàn),基于互相關(guān)的幀同步算法對載波頻偏的容忍度與本地同步序列的長度成反比。所以,為了進(jìn)一步減少幀同步的漏同步概率,在將本地同步序列分成幀同步檢測和幀同步確認(rèn)兩部分的基礎(chǔ)上,本文的幀同步檢測采用如圖3所示的分段相關(guān)法。在分段相關(guān)的幀同步檢測算法中,用于幀同步檢測的本地同步序列1等分為檢測序列1和檢測序列2兩段,然后用這兩段檢測序列同時(shí)與輸入信號進(jìn)行相關(guān),只要一個(gè)相關(guān)結(jié)果大于門限,就認(rèn)為幀同步檢測成功。

為了使幀同步算法更適于在FPGA中實(shí)現(xiàn),本文對傳統(tǒng)相關(guān)器進(jìn)行了改進(jìn),實(shí)現(xiàn)方法如下:

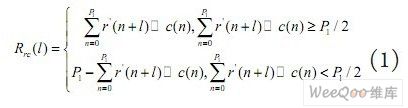

首先對接收信號進(jìn)行抽樣判決(即將大于0信號的判決為“1”,否則判決為“0”),將接收信號變換為由“0”和“1”組成的序列,然后再與用于本地同步序列(用于幀同步檢測的本地同步序列)進(jìn)行相關(guān)運(yùn)算。其中,相關(guān)函數(shù)可以定義為:

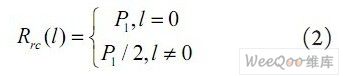

其中,表示同或,表示同步序列長度。考慮到接收信號中的數(shù)據(jù)塊與本地同步序列c(n)無關(guān),并忽略噪聲的影響,可以得到:

即,只有在時(shí),出現(xiàn)相關(guān)峰。

使用上述相關(guān)方法,載波頻偏引起的接收信號幅度變化不會(huì)影響相關(guān)峰幅度,只有在頻偏引起接收抽樣序列在發(fā)生反相時(shí),相關(guān)結(jié)果小(如當(dāng)在中間位置反相時(shí),前半段相關(guān)結(jié)果為,后半段相關(guān)結(jié)果為0,從而導(dǎo)致)。而由于本文的幀同步檢測使用分段相關(guān)的方法,通常情況下載波頻偏引起接收同步序列在每個(gè)分段都產(chǎn)生反相的可能性很小,所以可以有效防止載波頻偏引起漏同步發(fā)生的概率。

幀同步確認(rèn)

幀同步確認(rèn)的主要目的是判斷幀同步檢測結(jié)果是否屬于假同步,減少出現(xiàn)假同步的概率。它利用接收同步序列的后半部分與本地同步序列的后半部分(即圖2中的本地同步序列2)之間的相關(guān)性實(shí)現(xiàn)。由于幀同步確認(rèn)時(shí),位同步、載波同步等模塊同時(shí)工作,幀同步確認(rèn)受載波頻偏等因素的影響較小,可以采用接收序列與本地序列直接相關(guān)的算法實(shí)現(xiàn)。

位同步

位同步模塊在幀同步檢測成功后啟動(dòng)(與幀同步確認(rèn)同時(shí)進(jìn)行),利用接收同步序列的后半部分與本地同步序列的后半部分(即圖2中的本地同步序列2)之間相關(guān)性,通過利用比較時(shí)鐘與接收碼元之間的相關(guān)差來判斷本地時(shí)鐘是否需要進(jìn)行調(diào)整,從而實(shí)現(xiàn)位同步。當(dāng)最佳判決點(diǎn)處于接收信號碼元的中間位置時(shí),位同步算法原理如圖4示,其中超前時(shí)鐘和滯后時(shí)鐘作為比較時(shí)鐘。對于最佳判決點(diǎn)不處于碼元中間的情況,只要修改圖4中超前、滯后時(shí)鐘與本地時(shí)鐘之間的相位差即可。

相關(guān)器采用與幀同步檢測相同的相關(guān)方法式(1):當(dāng)最佳判決點(diǎn)處于碼元中間的情況,即本地時(shí)鐘相位與最佳判決點(diǎn)一致時(shí),超前時(shí)鐘和滯后時(shí)鐘相位都在最佳判決點(diǎn)附近,其相關(guān)結(jié)果基本相同,本地時(shí)鐘產(chǎn)生器不需要進(jìn)行調(diào)整;當(dāng)本地時(shí)鐘相位超前于最佳判決點(diǎn)時(shí),超前時(shí)鐘遠(yuǎn)離最佳判決點(diǎn),其控制下相關(guān)器的輸出減小為(P1-1)/2,而滯后時(shí)鐘控制下相關(guān)器的輸出仍為(P1-1),判決模塊通知本地時(shí)鐘產(chǎn)生器進(jìn)行滯后處理。同理,當(dāng)本地時(shí)鐘相位滯后于最佳判決點(diǎn)時(shí),產(chǎn)生器進(jìn)行超前處理。

FPGA實(shí)現(xiàn)與仿真驗(yàn)證

根據(jù)新一代無線通信統(tǒng)一平臺的特點(diǎn),同步功能需要在FPGA內(nèi)實(shí)現(xiàn)。本文利用Altera的quartus設(shè)計(jì)軟件,采用自頂向下的模塊化設(shè)計(jì)方法,用VHDL語言完成時(shí)間同步相關(guān)的各個(gè)模塊的編程設(shè)計(jì),并利用仿真軟件modelsim完成仿真驗(yàn)證。測試系統(tǒng)如圖5。其中,發(fā)端主要包括成幀(frame)和上變頻(duc)兩個(gè)模塊,將信源數(shù)據(jù)按一定標(biāo)準(zhǔn)組成幀,并調(diào)制到一定的中心頻率發(fā)出;收端主要包括下變頻(ddc)、低通濾波(lpf)、時(shí)鐘生成(clk_gen)和同步處理(recv)等模塊。其中,recv包含了幀同步、位同步和載波同步等模塊,duc和ddc模塊為了測試存在載波頻偏時(shí)的同步算法性能而加入。測試系統(tǒng)相關(guān)參數(shù)如下。

clk_s1:發(fā)端碼元時(shí)鐘,1.25MHz,即發(fā)端碼元速率為1.25MHz。

clk_s2:發(fā)端duc模塊時(shí)鐘,80MHz(根據(jù)新一代無線通信統(tǒng)一平臺實(shí)際參數(shù)設(shè)定)。

clk_r1:收端本地時(shí)鐘產(chǎn)生器模塊輸入時(shí)鐘,19.98MHz,通過可控時(shí)鐘生成器(16倍分頻)產(chǎn)生1.24875MHz的本地抽樣時(shí)鐘(與發(fā)送端碼元速率相差1.25KHz)。

clk_r2:收端ddc模塊時(shí)鐘,與clk_s2同頻,80MHz。

另外,發(fā)端duc輸出信號中心頻率為20MHz,收端ddc的本地載波頻率為20.04MHz(即收發(fā)兩端存在40KHz的載波頻偏)。

假設(shè)幀同步序列為7階m序列(長度為127),其仿真結(jié)果如圖6示。其中,圖6(a)顯示了幀時(shí)間同步的過程。在幀同步檢測階段,載波頻偏引起輸入信號幅度的較大范圍變化,并發(fā)生反相,通過采用分段相關(guān)法,幀同步檢測可以正確完成;而在幀同步確認(rèn)階段,載波同步等模塊開始工作,頻偏等對接收信號的影響基本消除,幀同步確認(rèn)模塊可以正確完成預(yù)定功能,從而實(shí)現(xiàn)幀同步。而圖6(b)顯示了位同步調(diào)整過程。在位同步前,本地時(shí)鐘上升沿處于接收序列碼元的邊緣(本地時(shí)鐘相位不處于最佳判決時(shí)刻),超前或滯后時(shí)鐘控制下的相關(guān)器輸入序列只有一路與本地同步序列對齊,位同步模塊根據(jù)兩個(gè)相關(guān)器的結(jié)果對本地時(shí)鐘進(jìn)行調(diào)整,直到本地時(shí)鐘相位與最佳判決時(shí)刻對齊。綜上所述,本文的時(shí)間同步算法可以在存在載波頻偏的情況下,很好完成幀同步功能,并同時(shí)利用同步序列完成位同步功能,大大縮短了位同步收斂所需的時(shí)間。

結(jié)語

本文根據(jù)新一代無線通信統(tǒng)一平臺需要兼容多種無線通信體制以及采用FPGA完成預(yù)處理功能的特點(diǎn),提出了一種適用于多種無線通信系統(tǒng)且硬件實(shí)現(xiàn)簡單的時(shí)間同步算法。該算法由幀同步和位同步組成,幀同步和位同步都利用同步序列實(shí)現(xiàn),適用于各種主流無線通信系統(tǒng)。在FPGA上實(shí)現(xiàn)了該算法,仿真結(jié)果證明了該算法是可行而且有效的,可以滿足平臺對主流無線通信體制的兼容性需求。