摘 要: 利用現(xiàn)有802.11b無線網(wǎng)卡" title="無線網(wǎng)卡">無線網(wǎng)卡的物理層部分和Altera公司的EPXA1開發(fā)板" title="開發(fā)板">開發(fā)板實現(xiàn)可以收發(fā)802.11b無線網(wǎng)絡(luò)信號的軟件無線電平臺,在此平臺基礎(chǔ)上可自由開發(fā)各種無線局域網(wǎng)媒體訪問控制協(xié)議。

關(guān)鍵詞: 802.11b網(wǎng)卡 媒體訪問控制 EPXA1 開發(fā)平臺

無線局域網(wǎng)媒體訪問控制(MAC)協(xié)議的開發(fā)是目前各種無線應(yīng)用研究的熱點。同時MAC協(xié)議的開發(fā)、調(diào)試和實現(xiàn)離不開物理層(PHY)的支持。很多MAC協(xié)議的開發(fā)者由于沒有物理層的支持,只能停留在協(xié)議仿真的階段。本文提出了一個可以通過無線鏈路收發(fā)信號(可以與基于802.11b的無線局域網(wǎng)AP以及無線網(wǎng)卡通信)的無線MAC開發(fā)平臺。該平臺利用現(xiàn)有802.11b無線網(wǎng)卡的物理層部分(包括天線、射頻芯片、中頻芯片和基帶處理器" title="基帶處理器">基帶處理器),再加上EPXA1開發(fā)板構(gòu)成。利用該平臺,可以在EPXA1開發(fā)板上進(jìn)行各種MAC協(xié)議的開發(fā)和調(diào)試。

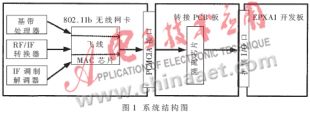

1 系統(tǒng)架構(gòu)

系統(tǒng)主要由三部分構(gòu)成:802.11b無線網(wǎng)卡、EPXA1開發(fā)板以及兩者之間轉(zhuǎn)接PCB板,如圖1所示。

系統(tǒng)中使用的802.11b無線網(wǎng)卡通過標(biāo)準(zhǔn)的PCMCIA接口與筆記本相連。該無線網(wǎng)卡最大的特點是MAC控制芯片和基帶處理芯片以及前端中頻射頻芯片是分離的,只有這樣才能將其MAC芯片替換成EPXA1開發(fā)板。在無線網(wǎng)卡啟動之前必須給基帶處理芯片以及前端中頻、射頻芯片的控制寄存器" title="控制寄存器">控制寄存器設(shè)置合適的值。這是控制邏輯PLCI部分要做的工作。該網(wǎng)卡的主要組成芯片有:

(a)HFA3841(Wireless LAN Medium Access Controller)是該無線網(wǎng)卡的MAC部分,在本設(shè)計中,將其替換成筆者的開發(fā)板。

(b)HFA3861B (Baseband processor)是無線網(wǎng)卡的基帶處理器[3],在網(wǎng)卡啟動過程中,需要通過相應(yīng)的串行配置口對其進(jìn)行配置。

(c)HFA3683A (RF/IF converter and synthesizer)芯片進(jìn)行射頻到中頻的變換[4],需要通過相應(yīng)配置口進(jìn)行控制寄存器的配置。

(d)HFA3783 芯片進(jìn)行中頻到基帶的變換[5],也需要通過相應(yīng)配置口進(jìn)行寄存器的配置(工作模式和工作頻率等)。

Altera公司的EPXA1開發(fā)板集成了ARM922T嵌入式微處理器以及相應(yīng)外設(shè),其外設(shè)中擁有10萬等效系統(tǒng)門的可編程邏輯器件以及相應(yīng)的擴展I/O" title="I/O">I/O口,不需要再另外設(shè)計FPGA電路,更方便了軟件和硬件的協(xié)同設(shè)計。同時,Altera公司提供的QuartusII軟件,也提供了對硬件和軟件協(xié)同設(shè)計的良好支持。

轉(zhuǎn)接PCB板用于連接EPXA1開發(fā)板的擴展I/O口和802.11b無線網(wǎng)卡上有用的信號線。板上設(shè)計了一個PCMCIA插槽,用來固定無線網(wǎng)卡,轉(zhuǎn)接板使用了隔離芯片SN74CBTD3384進(jìn)行電平轉(zhuǎn)換和保護EPXA1開發(fā)板,同時也通過該板給無線網(wǎng)卡供電。

2 設(shè)計過程

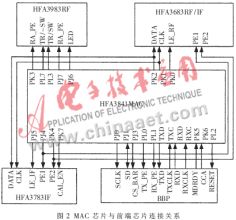

2.1對802.11b無線網(wǎng)卡的處理

首先拿掉無線網(wǎng)卡的MAC芯片,然后將MAC芯片上與基帶處理器、前端射頻以及中頻芯片相連的線引出,因為在網(wǎng)卡啟動過程中,需要通過這些線對前端芯片進(jìn)行相應(yīng)配置。圖2是無線網(wǎng)卡的MAC芯片與其他芯片之間的連接關(guān)系,在設(shè)計過程要確保將這些線引出到EPXA1開發(fā)板上。

2.2 轉(zhuǎn)接PCB板的設(shè)計

可以參照PCMCIA接口標(biāo)準(zhǔn),將其中的電源線、地線以及有用的地址線和數(shù)據(jù)線連接到EPXA1的擴展I/O口(邏輯高電平為5V),連接過程使用了SN74CBTD3384進(jìn)行電平轉(zhuǎn)換(5V到3.3V的轉(zhuǎn)換)。另外在EPXA1的擴展I/O口中,有提供3.3V和5V電源的引腳,可以作為無線網(wǎng)卡的電源,PCB板上還可以加上測試引腳,方便硬件的調(diào)試。

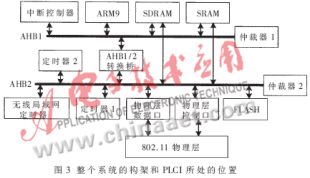

2.3 PLCI部分的設(shè)計

整個系統(tǒng)的構(gòu)架和PLCI所處的位置如圖3所示。PLCI(物理層控制接口)和PLDI(物理層數(shù)據(jù)接口)是設(shè)計的重點,是利用EPXAl的可編程邏輯實現(xiàn)的,主要編程語言是Verilog HDL。PLCI是MAC與物理層的控制接口,它實現(xiàn)了對前端芯片(包括HFA3861B、HFA3683以及HFA3783)的控制寄存器的配置,包括產(chǎn)生配置所需的串行數(shù)據(jù)、時鐘及片選信號。PLDI是MAC與物理層的數(shù)據(jù)接口,是MAC與PHY交換數(shù)據(jù)的通路;而ARM9嵌入式微處理器則運行C語言代碼實現(xiàn)各種無線MAC協(xié)議。ARM9與外圍設(shè)備之間通過AHB總線連接。

在寫程序之前,首先要弄清楚各個控制寄存器的讀寫過程。

BBP(基帶處理器)的控制接口是一個典型的三線接口,即只有時鐘(SCLK)、數(shù)據(jù)(SD)和片選(CS_BAR)三個信號,沒有單獨的讀/寫使能信號,而利用了地址的最高位來標(biāo)識讀或?qū)懖僮鳌C看巫x/寫操作時,數(shù)據(jù)線(SD)上先后出現(xiàn)串行的地址和數(shù)據(jù),其中地址位的MSB(A7)=1時為寫操作,表明將數(shù)據(jù)寫入該地址對應(yīng)的寄存器中;地址位MSB(A7)=0時為讀操作,表面后面的數(shù)據(jù)是從該地址指示的寄存器中讀取出來的。

HFA3683與HFA3783的讀寫時序相同,通過LE_RF和LE_IF的有效(低有效)來決定對哪塊芯片進(jìn)行讀寫。

DATA線上的串行數(shù)據(jù)是在時鐘的上升沿寫入芯片中的一個20位的移位寄存器,然后在LE的上升沿寫入根據(jù)LSB1和LSB2兩位對應(yīng)的地址。

上述的串行輸出數(shù)據(jù)(SD)和時鐘(SCLK)由PLCI邏輯產(chǎn)生。各前端芯片利用時鐘的上升沿來采集數(shù)據(jù)的,所以數(shù)據(jù)與時鐘的上升沿要嚴(yán)格對齊,有足夠的建立時間和保持時間。

在PLCI的設(shè)計中,定義了一些寄存器與CPU通信,這些寄存器根據(jù)相應(yīng)芯片讀寫時序的要求,有不同的寬度,例如BBP的寫寄存器有17位,低8位為要寫入的數(shù)據(jù),高8位為要寫入的寄存器的地址,最高位用來表明寫入操作是否完成。以便啟動下一次讀寫操作。

ESS (Excalibur Stripe Simulator)是一個Stripe仿真模型,它可以仿真CPU指令的執(zhí)行,并用來觀察PLD-to-Stripe和Stripe-to-PLD的總線時序。ADS 1.2 帶的AXD調(diào)試器可以模擬CPU執(zhí)行指令的情況,并觀察每條指令執(zhí)行之后系統(tǒng)的狀態(tài)。

通過AXD Debugger與ESS的結(jié)合,可以觀察一條PLD-to-Stripe或者Stripe-to-PLD總線操作指令執(zhí)行后相應(yīng)總線上的時序,再結(jié)合ModelSim進(jìn)行仿真,方便了程序的調(diào)試。圖4是ModelSim中對BBP進(jìn)行配置時的仿真波形,該波形與要求的BBP的寫入邏輯是一致的。

3 系統(tǒng)的啟動和驗證

在啟動系統(tǒng)前,還必須寫一個PLCI.C文件,在其中利用c函數(shù)對PLCI.V中定義的寄存器進(jìn)行讀寫操作。

//BBP的寫操作函數(shù)

void BBP_wr(long val)

{

*BBP_WRITE=val|0x8000;

//val的高八位是地址,低八位為數(shù)據(jù),最高位置1表明為寫寄存器操作

while(((*BBP_WRITE)&0x10000)==0x10000){}//讀取標(biāo)志位,一直到操作完成

}

RF以及IF芯片的寫操作函數(shù)類似。

BBP總共有49個寄存器要進(jìn)行寫入操作[1]。

HFA3683有三個控制寄存器需要寫入[4],HFA3783有四個控制寄存器[5]。后面兩個芯片共同的寄存器有:模式寄存器M(用于控制芯片的工作模式)、R counter寄存器和A/B counter寄存器(用于控制頻率綜合器的綜合頻率),R counter和A/B counter的具體值需要對無線網(wǎng)卡工作時的射頻和中頻頻率進(jìn)行測量得到。按照802.11b協(xié)議的規(guī)定之一,無線網(wǎng)卡工作時共有14個信道[2],所以得到的射頻芯片(HFA3683A)工作頻率共有14個(即有14種不同的R、A、B值),中頻(HFA3783)芯片的工作頻率有一個。

使用的編程工具是Quartus II,它可以分別編譯硬件部分(PLCI.V主要是或者verilog HDL語言)和軟件部分(PLCI.C),然后再一起編譯生成.hex文件下載到開發(fā)板上。

驗證過程:將無線網(wǎng)卡設(shè)置成接收狀態(tài)(RX_PE置高、TX_PE置低、RADIO_PE置低、PE1置高、PE2置高、RESET置高、TR/SW置低)。另外需要設(shè)置好一個802.11b的AP(Access Point),將其設(shè)置在一個固定的工作頻道上,同時設(shè)置RF/IF Converter 的控制寄存器,使網(wǎng)卡也工作在該頻道上。此時用邏輯分析儀監(jiān)測來自BBP的三個信號:RXC、RXD、MD_RDY信號,可以在邏輯分析儀上得到如圖5所示波形。

本系統(tǒng)提供了一條至MAC的最高速率為22Mbps的串行數(shù)據(jù)鏈路,結(jié)合EPAX1開發(fā)板上的嵌入式微處理器可以構(gòu)建各種無線局域網(wǎng)演示系統(tǒng)。利用現(xiàn)有的無線網(wǎng)卡作為物理層,可以給那些專注于上層協(xié)議開發(fā)的人更多的方便。只要有相應(yīng)的控制邏輯,這種系統(tǒng)構(gòu)建方式也適用于其它的開發(fā)板,給想驗證和實現(xiàn)自己開發(fā)MAC協(xié)議的人帶來了一條捷徑。筆者目前正在利用此平臺開發(fā)802.11e媒體訪問控制協(xié)議。

參考文獻(xiàn)

1 IEEE Std 802.11-1999:Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications[S].USA:IEEE, 1999

2 IEEE Std 802.11b: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) specifications-Higher-Speed Physical Layer Extension in the 2.4GHz Band.[S]. USA:IEEE,1999

3 Direct Sequence Spread Spectrum Baseband Processor datasheet

4 2.4GHz RF/IF Converter and Synthesizer datasheet

5 I/Q Modulator/Demodulator and Synthesizer datasheet