引言

DP83848C是美國(guó)國(guó)家半導(dǎo)體公司生產(chǎn)的一款魯棒性好、功能全、功耗低的10/100 Mbps單路物理層(PHY)器件。它支持MII(介質(zhì)無關(guān)接口)和RMII(精簡(jiǎn)的介質(zhì)無關(guān)接口),使設(shè)計(jì)更簡(jiǎn)單靈活;同時(shí),支持10BASE~T和100BASE-TX以太網(wǎng)外設(shè),對(duì)其他標(biāo)準(zhǔn)以太網(wǎng)解決方案有良好的兼容性和通用性。

MII(Medium Independent Interface)是IEEE802.3u規(guī)定的一種介質(zhì)無關(guān)接口,主要作用是連接介質(zhì)訪問控制層(MAC)子層與物理層(PH-Y)之間的標(biāo)準(zhǔn)以太網(wǎng)接口,負(fù)責(zé)MAC和PHY之間的通信。由于MII需要多達(dá)16根信號(hào)線,由此產(chǎn)生的I/O口需求及功耗較大,有必要對(duì)MII引腳數(shù)進(jìn)行簡(jiǎn)化,因此提出了RMII(Reduced Medium Independent Interface,精簡(jiǎn)的介質(zhì)無關(guān)接口),即簡(jiǎn)化了的MII。

1 硬件設(shè)計(jì)

1.1 電路設(shè)計(jì)

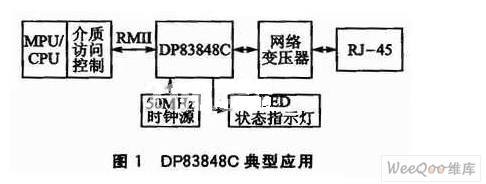

DP83848C的收發(fā)線路各是一對(duì)差分線,經(jīng)過變比為1:1的以太網(wǎng)變壓器后與網(wǎng)線相連。以太網(wǎng)變壓器的主要作用是阻抗匹配、信號(hào)整形、網(wǎng)絡(luò)隔離,以及濾除網(wǎng)絡(luò)和設(shè)備雙方面的噪音。典型應(yīng)用如圖1所示。

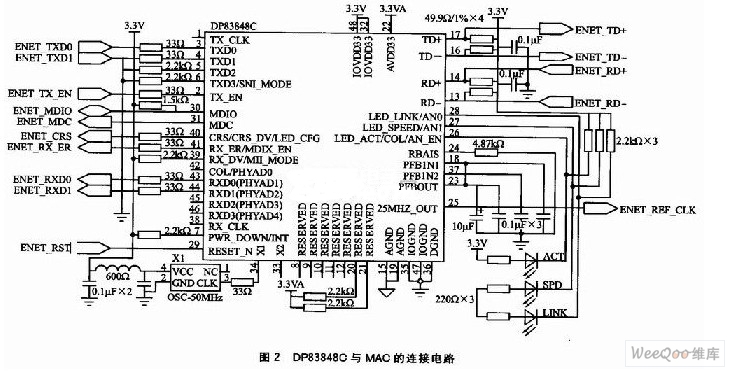

圖2是DP83848C與MAC的連接電路。其中,Xl為50 MHz的有源振蕩器。

1.2 PCB布局布線

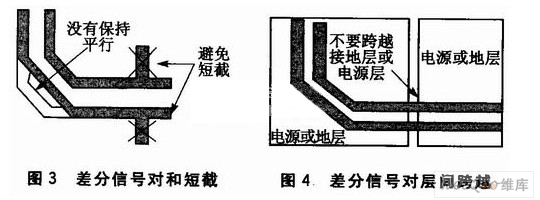

布局方面,精度為1%的49.9 Ω電阻和100 nF的去耦電容應(yīng)靠近PHY器件放置,并通過最短的路徑到電源。如圖3所示,兩對(duì)差分信號(hào)(TD和RD)應(yīng)平行走線,避免短截,且盡量保證長(zhǎng)度匹配,這樣可以避免共模噪聲和EMI輻射。理想情況下,信號(hào)線上不應(yīng)有交叉或者通孔,通孔會(huì)造成阻抗的非連續(xù)性,所以應(yīng)將其數(shù)目降到最低;同時(shí),差分線應(yīng)盡可能走在一面,且不應(yīng)將信號(hào)線跨越分割的平面,如圖4所示。信號(hào)跨越一個(gè)分割的平面會(huì)造成無法預(yù)測(cè)的回路電流,極可能導(dǎo)致信號(hào)質(zhì)量惡化并產(chǎn)生EMI問題。注意,圖3和圖4中,陰影部分為錯(cuò)誤方法。

2 RMll模式描述

RMII模式在保持物理層器件現(xiàn)有特性的前提下減少了PHY的連接引腳。

RMII由參考時(shí)鐘REF_CLK、發(fā)送使能TX_EN、發(fā)送數(shù)據(jù)TXD[1:0]、接收數(shù)據(jù)RXD[1:0]、載波偵聽/接收數(shù)據(jù)有效CRS_DV和接收錯(cuò)誤RX_ER(可選信號(hào))組成。在此基礎(chǔ)上,DP83848C還增加了RX_DV接收數(shù)據(jù)有效信號(hào)。

2. 1 REF_CLK——參考時(shí)鐘

REF_CLK是一個(gè)連續(xù)時(shí)鐘,可以為CRS_DV、RXD[1:O]、TX_EN、TXD[1:O]、RX_DV和RX_ER提供時(shí)序參考。REF_CLK由MAC層或外部時(shí)鐘源源提供。REF_CLK頻率應(yīng)為50 MHz±50×10-6,占空比介于35%和65%之間。在RMII模式下,數(shù)據(jù)以50 MHz的時(shí)鐘頻率一次傳送2位。因此,RMII模式需要一個(gè)50 MHz有源振蕩器(而不是晶振)連接到器件的X1腳。

2.2 TX_EN——發(fā)送使能

TX_EN表示MAC層正在將要傳輸?shù)碾p位數(shù)據(jù)放到TXD[1:O]上。TX_EN應(yīng)被前導(dǎo)符的首個(gè)半字節(jié)同步確認(rèn),且在所有待傳雙位信號(hào)載入過程中都保持確認(rèn)。跟隨一幀數(shù)據(jù)的末2位之后的首個(gè)REF_CLK上升沿之前,MAC需對(duì)TX_EN取反。TX_EN的變化相對(duì)于REF_CLK是同步的。

2.3 TXD[1:0]——發(fā)送數(shù)據(jù)

TXD[1:O]的變換相對(duì)于REF_CLK是同步的。TX_EN有效后,PHY以TXD[1:0]作為發(fā)送端。

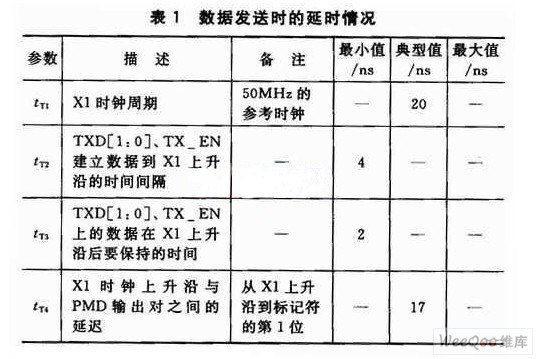

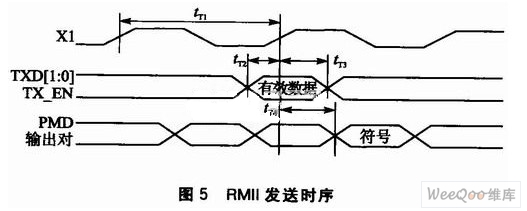

在10 Mbps模式下,由于REF_CLK的頻率是在10Mbps模式中數(shù)據(jù)速率的10倍。因此TXD[1:0]上的值必須在10個(gè)脈沖期間保持穩(wěn)定,確保DP83848C能夠每隔10個(gè)周期進(jìn)行采樣。發(fā)送時(shí)序如圖5所示,發(fā)送延時(shí)情況如表l所列。其中,PMD為物理介質(zhì)關(guān)聯(lián)層(physical media depen-dent)接口。

2.4 RXD[1:0]——接收數(shù)據(jù)

RXD[1:0]轉(zhuǎn)換是與REF_CLK同步的。在CRS_DV有效后的每個(gè)時(shí)鐘周期里,RXD[1:O]接收DP83848C的兩位恢復(fù)數(shù)據(jù)。在某些情況下(如數(shù)據(jù)恢復(fù)前或發(fā)生錯(cuò)誤),則接收到的是RXD[1:O]的預(yù)確定值而不是恢復(fù)數(shù)據(jù)。CRS_DV解除確認(rèn)后,RXD[1:O]為“00”,表示進(jìn)入空閑狀態(tài)。CRS_DV確認(rèn)后,在產(chǎn)生正確的接收解碼之前,DP83848C將保證RXD[1:0]=“00”。

DP83848C提供的恢復(fù)數(shù)據(jù)總是半字節(jié)或成對(duì)雙位信號(hào)的形式,這對(duì)于由前導(dǎo)符開始的所有數(shù)據(jù)值都成立。因?yàn)镃RS_DV是異步確認(rèn)的,不能假設(shè)先于前導(dǎo)符的“00”數(shù)據(jù)會(huì)是雙位信號(hào)形式。

100 Mbps模式下,在CRS_DV確認(rèn)之后的正常接收過程中,RXD[1:O]將會(huì)保持“00”,直到接收器檢測(cè)到正確的起始串分界符(STart St-ream Delimiter,SSD)。一旦檢測(cè)到SSD,DP83848C將會(huì)驅(qū)動(dòng)前導(dǎo)符(“01”),后面緊跟著起始幀分界符(Start of Frame. Delimiter,SFD)(“01”“01”“01”“11”)。MAC應(yīng)該開始SFD之后的數(shù)據(jù)。如果檢測(cè)到接收錯(cuò)誤,在載波活動(dòng)結(jié)束前,RXD[1:0]將會(huì)替換為接收字符串“01”。而由于幀中剩余數(shù)據(jù)被替換,MAC的奇偶校驗(yàn)將會(huì)拒絕錯(cuò)誤的信息包。如果檢測(cè)到錯(cuò)誤的載波(壞的SSD),RXD[1:O]將會(huì)替換為“10”,直到接收事件結(jié)束。這種情況下,RXD[1:O]將會(huì)從“00”變?yōu)?ldquo;10”,而無需標(biāo)明前導(dǎo)符(“01”)。

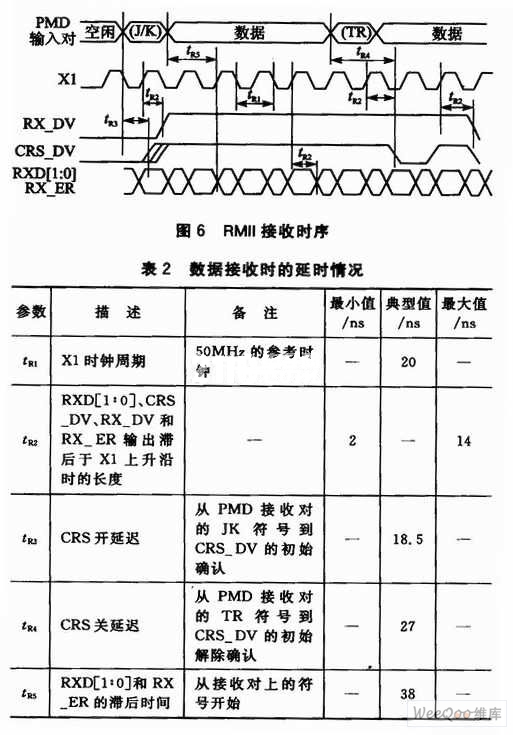

10 Mbps模式下,CRS_DV確認(rèn)后,RXD[1:O]將會(huì)一直保持“00”,直到DP83848C有恢復(fù)脈沖并能對(duì)接收數(shù)據(jù)進(jìn)行解碼為止。當(dāng)存在有效接收數(shù)據(jù)時(shí),RXD[1:O]以“01”為前導(dǎo)符接收恢復(fù)的數(shù)據(jù)值。因?yàn)镽EF_CLK頻率是10 Mbps模式下數(shù)據(jù)速率的10倍,MAC對(duì)RXD[1:0]上的值每隔10個(gè)周期采樣一次。接收時(shí)序如圖6所示,接收延時(shí)情況如表2所列。

2.5 RX_DV——接收數(shù)據(jù)有效

盡管RMII并不要求,DP83848C還是提供了一個(gè)RX_DV信號(hào)。RX-DV是沒有結(jié)合CRS的接收數(shù)據(jù)有效信號(hào)(Receive Data Valid)。第一個(gè)正確的恢復(fù)數(shù)據(jù)(前導(dǎo)符)或偽載波檢測(cè)到來時(shí),RX_DV被確認(rèn),在恢復(fù)數(shù)據(jù)的末兩位傳送之后解除確認(rèn)。通過使用該信號(hào),全雙工MAC不必再?gòu)腃RS _DV信號(hào)中恢復(fù)RX_DV信號(hào)。

2.6 CRS_DV——載波偵聽/接收數(shù)據(jù)有效

當(dāng)接收介質(zhì)處于非空閑狀態(tài)時(shí),由PHY來確認(rèn)CRS_DV。在載波檢測(cè)中,CRS_DV依據(jù)與工作模式相關(guān)的標(biāo)準(zhǔn)異步確認(rèn)。10BASE_T模式下,靜噪通過時(shí)發(fā)生該事件。在100BASE-TX模式,當(dāng)10位中檢測(cè)到2個(gè)非相鄰的零值時(shí),發(fā)生該事件。

在RMII規(guī)范(1.2版)中提到,載波丟失將導(dǎo)致與REF_CLK周期同步的CRS_DV解除確認(rèn),這在RXD[1:O]半字節(jié)的首兩位出現(xiàn)(即CRS_DV僅在半字節(jié)邊界解除確認(rèn))。在CRS_DV首次解除確認(rèn)后,如果DP83848C還有數(shù)據(jù)位要加在RXD[1:O]上,則在REF_CLK周期中,DP83848C應(yīng)在每半個(gè)字節(jié)的第2個(gè)雙位上確認(rèn)CRS_DV,并在一個(gè)半字節(jié)的第1個(gè)雙位解除確認(rèn)。這樣,從半字節(jié)邊界開始,到CRS(載波偵聽/接收信號(hào))在RX_DV前結(jié)束時(shí),CRS_DV以25 MHz(100 Mbps模式)或2.5MHz(10 Mbps模式)的頻率翻轉(zhuǎn)(假設(shè)當(dāng)載波事件結(jié)束時(shí)DP83848C還有待傳送的數(shù)據(jù)位)。

通過編程DP83848C能夠與RMII規(guī)范(1.0版)很好地兼容。在該模式下,CRS_DV將會(huì)異步地與CRS進(jìn)行確認(rèn),但是要等傳送完最后的數(shù)據(jù)時(shí)才會(huì)解除確認(rèn),CRS_DV在數(shù)據(jù)包的末端不會(huì)被翻轉(zhuǎn)。該模式雖然不能對(duì)來自CRS_DV的CRS信號(hào)進(jìn)行精確的恢復(fù),但是卻可以使MAC層的設(shè)計(jì)更簡(jiǎn)單。

在出錯(cuò)的載波活動(dòng)時(shí)間中,CRS_DV保持確認(rèn)。一旦確認(rèn)CRS_DV,則可以認(rèn)為在RXD[1:O]上的數(shù)據(jù)是有效的。然而,由于CRS_DV的確認(rèn)相對(duì)于REF_CLK是異步的,因而在正確解碼接收信號(hào)之前,RXD[1:0]上的數(shù)據(jù)應(yīng)為“00”。

2.7 RX_ER——接收錯(cuò)誤

遵照IEEE802.3標(biāo)準(zhǔn)的規(guī)定,DP83848C提供一個(gè)RX_ER輸出端。RX_ER可以維持一個(gè)或更多的REFCLK周期,來標(biāo)識(shí)一個(gè)在當(dāng)前PHY到幀的傳輸過程中曾出現(xiàn)的錯(cuò)誤(MAC子層不一定能檢測(cè)到,但PHY可以檢測(cè)到的編碼錯(cuò)誤或其他錯(cuò)誤)。RX_ER的變化相對(duì)于REF_CLK是同步的。

由于DP83848C是通過以固定數(shù)據(jù)代替原來數(shù)據(jù)的方式干擾到RXD[1:O],所以MAC不需要RX_ER,而只需CRC校驗(yàn)(即奇偶校驗(yàn))就可以檢測(cè)到錯(cuò)誤。

2.8 沖突檢測(cè)

RMII不向MAC提供沖突標(biāo)志。對(duì)于半雙工操作,MAC必須從CRS_DV和TX_EN信號(hào)中產(chǎn)生它自己的沖突檢測(cè)。為了實(shí)現(xiàn)這一點(diǎn)MAC必須從CRS-DV信號(hào)中恢復(fù)CRS信號(hào),并和TX_EN進(jìn)行邏輯與。注意,不能直接使用CRS_DV,因?yàn)镃RS_DV可能在幀的末端觸發(fā)以標(biāo)志CRS解除確認(rèn)。

3 RMII模式配置

DP83848C的RMII模式配置包括硬件和軟件兩個(gè)方面。

3.1 硬件配置

如圖2所示,DP83848C的X1(34)腳上提供50 MHzCMOS電平的振蕩信號(hào)。在上電和復(fù)位時(shí),強(qiáng)制DP83848C進(jìn)入RMII模式。方法是通過在RX_DV/MII_MODE(39腳)接入一個(gè)上拉電阻。

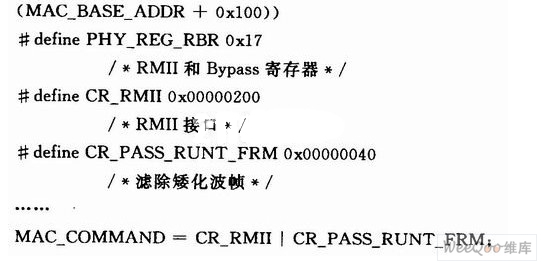

3.2 軟件配置

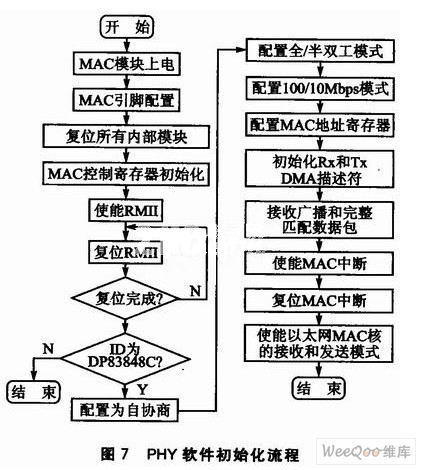

PHY的軟件初始化流程如圖7所示。

結(jié)語(yǔ)

DP83848C配合RMII標(biāo)準(zhǔn)接口提供了一種連接方案,可以減少M(fèi)AC至PHY接口所需要的引腳數(shù)目。該方案使得設(shè)計(jì)工程師在保持IEEE802.3規(guī)范中所有特性的同時(shí),降低系統(tǒng)設(shè)計(jì)成本。正因?yàn)槿绱耍珼P83848C能夠更好地適應(yīng)工業(yè)控制和工廠自動(dòng)化,以及通用嵌入式系統(tǒng)等應(yīng)用場(chǎng)合。