引 言

USB(Universal Serial Bus)具有以下特點(diǎn):即插即用、廣泛的軟硬件支持、低功耗、可選擇的多種速度模式、完備的總線拓?fù)浣Y(jié)構(gòu)。隨著半導(dǎo)體工藝技術(shù)的發(fā)展,集成電路設(shè)計(jì)者能夠?qū)⒂鷣?lái)愈復(fù)雜的功能集成到單硅片上。SoC是將系統(tǒng)集成在一塊芯片上,包括微處理器、模擬IP核、數(shù)字IP核和存儲(chǔ)器(或片外存儲(chǔ)控制接口)等。SoC的一項(xiàng)關(guān)鍵技術(shù)即為IP(Intellectual Property)復(fù)用技術(shù)。IP核是指在電子設(shè)計(jì)中預(yù)先開(kāi)發(fā)的用于系統(tǒng)芯片設(shè)計(jì)的可復(fù)用構(gòu)件,系統(tǒng)設(shè)計(jì)者在進(jìn)行一個(gè)復(fù)雜設(shè)計(jì)時(shí)將眾多IP核在一個(gè)芯片上有效集成,從而構(gòu)成一個(gè)功能強(qiáng)大的系統(tǒng)。IP技術(shù)在SoC的開(kāi)發(fā)中可以充分利用已有的開(kāi)發(fā)成果,從而縮短系統(tǒng)芯片的設(shè)計(jì)周期,提高效率。

在設(shè)計(jì)IP核時(shí)應(yīng)注意其可重用性,為了增強(qiáng)IP核的可能重用性,使IP核能更好地適應(yīng)不同總線結(jié)構(gòu)的SoC平臺(tái),可以為IP核設(shè)計(jì)一個(gè)總線接口模塊。該模塊主要完成片上總線的協(xié)議轉(zhuǎn)換和實(shí)現(xiàn),稱之為總線適配器(BusAdapter)。其特點(diǎn)為:IP核與外部的片上總線標(biāo)準(zhǔn)無(wú)關(guān),其邏輯相對(duì)固定,只需對(duì)相應(yīng)的總線適配器進(jìn)行配置就能夠有效地集成于不同片上總線的SoC平臺(tái)。當(dāng)前SoC中常用的總線協(xié)議有三種分別是:ARM公司的AMBA、Silicore公司的WISHBONE SoC Interconnection Archi—tecture和Ahera的Avalon總線。

本文實(shí)現(xiàn)的USB IP核中,設(shè)計(jì)了總線適配器,在綜合前針對(duì)WishBone總線或AMBA ASB總線通過(guò)宏定義進(jìn)行設(shè)置,從而使USB IP核能夠直接集成于WishBone或AMBA ASB總線的SoC系統(tǒng)中。

2 USB系統(tǒng)組成部分

系統(tǒng)主要分為三個(gè)部分:主機(jī)、設(shè)備和互連。在任何的系統(tǒng)中,只有一個(gè)主機(jī),與主機(jī)系統(tǒng)的接口稱作主機(jī)控制器。他可由硬件、固件和軟件綜合實(shí)現(xiàn)。設(shè)備可以分為功能性設(shè)備即外設(shè)和集線器,前者作為系統(tǒng)的功能擴(kuò)展設(shè)備而后者作為設(shè)備的擴(kuò)展連接點(diǎn)。互連定義了主機(jī)和外設(shè)的連接和通信方式。包括總線拓?fù)浣Y(jié)構(gòu)、內(nèi)部分層關(guān)系、數(shù)據(jù)傳輸模型和總線訪問(wèn)控制等幾個(gè)部分。一個(gè)簡(jiǎn)單的系統(tǒng)可以由一臺(tái)主機(jī)和一個(gè)外設(shè)構(gòu)成。

3 USB的模塊設(shè)計(jì)

3.1 模塊劃分

USB IP核主要是實(shí)現(xiàn)了USBl.1協(xié)議,在對(duì)整個(gè)協(xié)議分析的基礎(chǔ)上,整個(gè)IP核共分成五大模塊:串行接口引擎模塊、協(xié)議層模塊、端點(diǎn)控制模塊、端點(diǎn)存儲(chǔ)模塊和總線適配器模塊。串行接口引擎主要是支持最底層的USB協(xié)議,由于USB協(xié)議中為了增加抗干擾對(duì)比特流進(jìn)行了“不歸零碼(Non Return to Zero Invert)”的編解碼,同時(shí)為了可以從比特流中提取同步信號(hào)用了“位填充”和“位剔去”。串行接口主要完成比特流方面的處理。協(xié)議層模塊則主要是完成解包和打包。在USB協(xié)議中,數(shù)據(jù)緩沖區(qū)用了端點(diǎn)(Endpoint)這個(gè)概念,不同的緩沖區(qū)用了不同的端點(diǎn)號(hào)來(lái)區(qū)分,端點(diǎn)存儲(chǔ)模塊就是相應(yīng)的數(shù)據(jù)緩沖區(qū)。端點(diǎn)控制模塊主要是端點(diǎn)控制寄存器和端點(diǎn)狀態(tài)寄存器,對(duì)端點(diǎn)進(jìn)行相應(yīng)的控制。總線適配器模塊主要是在不同總線結(jié)構(gòu)的SoC中,對(duì)USB IP核總線接口進(jìn)行相應(yīng)的配置,從而可以進(jìn)行無(wú)縫連接到相應(yīng)的SoC中。USB IP核模塊劃分如圖1所示。

3.2 串口接口引擎

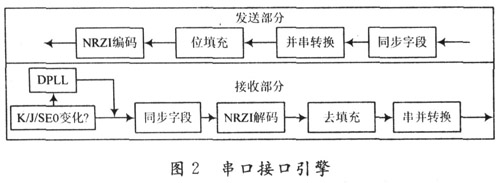

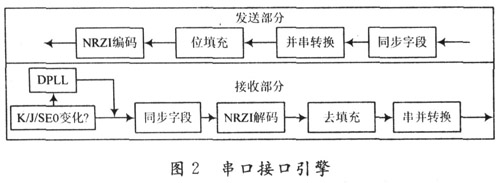

串口接口引擎主要是完成USB協(xié)議中比特流的處理。根據(jù)數(shù)據(jù)的傳輸方向可分為發(fā)送部分和接收部分。發(fā)送部分即為USB設(shè)備給USB主機(jī)發(fā)送數(shù)據(jù),接收部分則為USB設(shè)備從USB主機(jī)那里接收數(shù)據(jù)。如圖2所示。

接收部分:從同步域中恢復(fù)出12 MHz的時(shí)鐘信號(hào),接收主機(jī)過(guò)來(lái)的比特流對(duì)其進(jìn)行不歸零碼(NRZI)解碼,剔除位填充然后進(jìn)行串并轉(zhuǎn)換,最后將轉(zhuǎn)換后的數(shù)據(jù)以字節(jié)的形式傳給協(xié)議層。接收部分還要能判斷出一個(gè)包的開(kāi)始,在USB傳輸過(guò)程中,是以包為單的,因此接收部分首先要測(cè)包的開(kāi)始SOP(Start of Packet),所有包都是從同步字段(SYNC)開(kāi)始的,同步字段是產(chǎn)生最大的邊緣轉(zhuǎn)換密度(Endge Transition Density)的編碼序例。以NR—ZI編碼的二進(jìn)制串“KJKJKJKK”同步字段最后2位是同步字段結(jié)束的標(biāo)記,同時(shí)標(biāo)志了包標(biāo)識(shí)符(Pacekt Iden一tiler,PID)的開(kāi)始。只有當(dāng)檢測(cè)到包SOP才開(kāi)始后面的NRZI解碼、去位填充和串并操作,否則就繼續(xù)處于等待階段。

在接收部分還需要有檢錯(cuò)部分,在檢查到傳輸過(guò)來(lái)的數(shù)據(jù)有錯(cuò)誤時(shí),要進(jìn)行相應(yīng)的錯(cuò)誤處理。如在NRZI解碼后,在對(duì)數(shù)據(jù)進(jìn)行去位填充時(shí)發(fā)現(xiàn)了有連續(xù)7個(gè)“1”則可以認(rèn)為數(shù)據(jù)在傳輸過(guò)程中出現(xiàn)了錯(cuò)誤,數(shù)據(jù)包已經(jīng)損壞,必須通知協(xié)議層。在接收部分需要特別注意的是:在接收USB主機(jī)過(guò)來(lái)數(shù)據(jù)時(shí),是不同的時(shí)鐘域,因此必須考慮到亞穩(wěn)態(tài)問(wèn)題。在本設(shè)計(jì)中,由于只處理單個(gè)比特信號(hào),因此用了兩級(jí)寄存器來(lái)消除亞穩(wěn)態(tài)。

發(fā)送部分:將協(xié)議層打包好的加上同步字段,然后進(jìn)行并串轉(zhuǎn)換,將字節(jié)形式轉(zhuǎn)換成比特流形式,接著根據(jù)協(xié)議將數(shù)據(jù)進(jìn)行位填充和NRZI編碼,通過(guò)D+和D一信號(hào)傳送給USB主機(jī)。這個(gè)同步字段也是告訴USB主機(jī)有一個(gè)新數(shù)據(jù)包發(fā)送過(guò)來(lái)了,在發(fā)送部分還要產(chǎn)生包結(jié)束EOP(End of Packet)的信號(hào)。

3.3 USB協(xié)議層

協(xié)議層主要分成三個(gè)子模塊:解包模塊、打包模塊和協(xié)議引擎模塊。這一層主要是將經(jīng)過(guò)串口接口引擎模塊過(guò)來(lái)的數(shù)據(jù)進(jìn)行解包,剔除USB協(xié)議中的信息。同時(shí)將端點(diǎn)中要發(fā)送的數(shù)據(jù),在協(xié)議引擎控制下進(jìn)行相應(yīng)的打包,然后通過(guò)SIE模塊傳送給USB主機(jī)。 3.3.1 解包模塊

本模塊主要將接收到的信息包數(shù)據(jù)進(jìn)行解析,解析出包標(biāo)識(shí)(PID),端點(diǎn)地址和USB設(shè)備地址以及包含在包中的有效數(shù)據(jù)。在解包時(shí),對(duì)令牌包進(jìn)行CRC5校驗(yàn),對(duì)數(shù)據(jù)包進(jìn)CRCl6檢驗(yàn),若出錯(cuò)則進(jìn)行相應(yīng)的出錯(cuò)處理。從上面所述可知,任何包都有同步字段而同步字段在串口接口引擎模塊中已經(jīng)除去了,因此本模塊不用關(guān)心同步字段。整個(gè)解包數(shù)據(jù)流如圖3所示。

引 言

USB(Universal Serial Bus)具有以下特點(diǎn):即插即用、廣泛的軟硬件支持、低功耗、可選擇的多種速度模式、完備的總線拓?fù)浣Y(jié)構(gòu)。隨著半導(dǎo)體工藝技術(shù)的發(fā)展,集成電路設(shè)計(jì)者能夠?qū)⒂鷣?lái)愈復(fù)雜的功能集成到單硅片上。SoC是將系統(tǒng)集成在一塊芯片上,包括微處理器、模擬IP核、數(shù)字IP核和存儲(chǔ)器(或片外存儲(chǔ)控制接口)等。SoC的一項(xiàng)關(guān)鍵技術(shù)即為IP(Intellectual Property)復(fù)用技術(shù)。IP核是指在電子設(shè)計(jì)中預(yù)先開(kāi)發(fā)的用于系統(tǒng)芯片設(shè)計(jì)的可復(fù)用構(gòu)件,系統(tǒng)設(shè)計(jì)者在進(jìn)行一個(gè)復(fù)雜設(shè)計(jì)時(shí)將眾多IP核在一個(gè)芯片上有效集成,從而構(gòu)成一個(gè)功能強(qiáng)大的系統(tǒng)。IP技術(shù)在SoC的開(kāi)發(fā)中可以充分利用已有的開(kāi)發(fā)成果,從而縮短系統(tǒng)芯片的設(shè)計(jì)周期,提高效率。

在設(shè)計(jì)IP核時(shí)應(yīng)注意其可重用性,為了增強(qiáng)IP核的可能重用性,使IP核能更好地適應(yīng)不同總線結(jié)構(gòu)的SoC平臺(tái),可以為IP核設(shè)計(jì)一個(gè)總線接口模塊。該模塊主要完成片上總線的協(xié)議轉(zhuǎn)換和實(shí)現(xiàn),稱之為總線適配器(BusAdapter)。其特點(diǎn)為:IP核與外部的片上總線標(biāo)準(zhǔn)無(wú)關(guān),其邏輯相對(duì)固定,只需對(duì)相應(yīng)的總線適配器進(jìn)行配置就能夠有效地集成于不同片上總線的SoC平臺(tái)。當(dāng)前SoC中常用的總線協(xié)議有三種分別是:ARM公司的AMBA、Silicore公司的WISHBONE SoC Interconnection Archi—tecture和Ahera的Avalon總線。

本文實(shí)現(xiàn)的USB IP核中,設(shè)計(jì)了總線適配器,在綜合前針對(duì)WishBone總線或AMBA ASB總線通過(guò)宏定義進(jìn)行設(shè)置,從而使USB IP核能夠直接集成于WishBone或AMBA ASB總線的SoC系統(tǒng)中。

2 USB系統(tǒng)組成部分

系統(tǒng)主要分為三個(gè)部分:主機(jī)、設(shè)備和互連。在任何的系統(tǒng)中,只有一個(gè)主機(jī),與主機(jī)系統(tǒng)的接口稱作主機(jī)控制器。他可由硬件、固件和軟件綜合實(shí)現(xiàn)。設(shè)備可以分為功能性設(shè)備即外設(shè)和集線器,前者作為系統(tǒng)的功能擴(kuò)展設(shè)備而后者作為設(shè)備的擴(kuò)展連接點(diǎn)。互連定義了主機(jī)和外設(shè)的連接和通信方式。包括總線拓?fù)浣Y(jié)構(gòu)、內(nèi)部分層關(guān)系、數(shù)據(jù)傳輸模型和總線訪問(wèn)控制等幾個(gè)部分。一個(gè)簡(jiǎn)單的系統(tǒng)可以由一臺(tái)主機(jī)和一個(gè)外設(shè)構(gòu)成。

3 USB的模塊設(shè)計(jì)

3.1 模塊劃分

USB IP核主要是實(shí)現(xiàn)了USBl.1協(xié)議,在對(duì)整個(gè)協(xié)議分析的基礎(chǔ)上,整個(gè)IP核共分成五大模塊:串行接口引擎模塊、協(xié)議層模塊、端點(diǎn)控制模塊、端點(diǎn)存儲(chǔ)模塊和總線適配器模塊。串行接口引擎主要是支持最底層的USB協(xié)議,由于USB協(xié)議中為了增加抗干擾對(duì)比特流進(jìn)行了“不歸零碼(Non Return to Zero Invert)”的編解碼,同時(shí)為了可以從比特流中提取同步信號(hào)用了“位填充”和“位剔去”。串行接口主要完成比特流方面的處理。協(xié)議層模塊則主要是完成解包和打包。在USB協(xié)議中,數(shù)據(jù)緩沖區(qū)用了端點(diǎn)(Endpoint)這個(gè)概念,不同的緩沖區(qū)用了不同的端點(diǎn)號(hào)來(lái)區(qū)分,端點(diǎn)存儲(chǔ)模塊就是相應(yīng)的數(shù)據(jù)緩沖區(qū)。端點(diǎn)控制模塊主要是端點(diǎn)控制寄存器和端點(diǎn)狀態(tài)寄存器,對(duì)端點(diǎn)進(jìn)行相應(yīng)的控制。總線適配器模塊主要是在不同總線結(jié)構(gòu)的SoC中,對(duì)USB IP核總線接口進(jìn)行相應(yīng)的配置,從而可以進(jìn)行無(wú)縫連接到相應(yīng)的SoC中。USB IP核模塊劃分如圖1所示。

3.2 串口接口引擎

串口接口引擎主要是完成USB協(xié)議中比特流的處理。根據(jù)數(shù)據(jù)的傳輸方向可分為發(fā)送部分和接收部分。發(fā)送部分即為USB設(shè)備給USB主機(jī)發(fā)送數(shù)據(jù),接收部分則為USB設(shè)備從USB主機(jī)那里接收數(shù)據(jù)。如圖2所示。

接收部分:從同步域中恢復(fù)出12 MHz的時(shí)鐘信號(hào),接收主機(jī)過(guò)來(lái)的比特流對(duì)其進(jìn)行不歸零碼(NRZI)解碼,剔除位填充然后進(jìn)行串并轉(zhuǎn)換,最后將轉(zhuǎn)換后的數(shù)據(jù)以字節(jié)的形式傳給協(xié)議層。接收部分還要能判斷出一個(gè)包的開(kāi)始,在USB傳輸過(guò)程中,是以包為單的,因此接收部分首先要測(cè)包的開(kāi)始SOP(Start of Packet),所有包都是從同步字段(SYNC)開(kāi)始的,同步字段是產(chǎn)生最大的邊緣轉(zhuǎn)換密度(Endge Transition Density)的編碼序例。以NR—ZI編碼的二進(jìn)制串“KJKJKJKK”同步字段最后2位是同步字段結(jié)束的標(biāo)記,同時(shí)標(biāo)志了包標(biāo)識(shí)符(Pacekt Iden一tiler,PID)的開(kāi)始。只有當(dāng)檢測(cè)到包SOP才開(kāi)始后面的NRZI解碼、去位填充和串并操作,否則就繼續(xù)處于等待階段。

在接收部分還需要有檢錯(cuò)部分,在檢查到傳輸過(guò)來(lái)的數(shù)據(jù)有錯(cuò)誤時(shí),要進(jìn)行相應(yīng)的錯(cuò)誤處理。如在NRZI解碼后,在對(duì)數(shù)據(jù)進(jìn)行去位填充時(shí)發(fā)現(xiàn)了有連續(xù)7個(gè)“1”則可以認(rèn)為數(shù)據(jù)在傳輸過(guò)程中出現(xiàn)了錯(cuò)誤,數(shù)據(jù)包已經(jīng)損壞,必須通知協(xié)議層。在接收部分需要特別注意的是:在接收USB主機(jī)過(guò)來(lái)數(shù)據(jù)時(shí),是不同的時(shí)鐘域,因此必須考慮到亞穩(wěn)態(tài)問(wèn)題。在本設(shè)計(jì)中,由于只處理單個(gè)比特信號(hào),因此用了兩級(jí)寄存器來(lái)消除亞穩(wěn)態(tài)。

發(fā)送部分:將協(xié)議層打包好的加上同步字段,然后進(jìn)行并串轉(zhuǎn)換,將字節(jié)形式轉(zhuǎn)換成比特流形式,接著根據(jù)協(xié)議將數(shù)據(jù)進(jìn)行位填充和NRZI編碼,通過(guò)D+和D一信號(hào)傳送給USB主機(jī)。這個(gè)同步字段也是告訴USB主機(jī)有一個(gè)新數(shù)據(jù)包發(fā)送過(guò)來(lái)了,在發(fā)送部分還要產(chǎn)生包結(jié)束EOP(End of Packet)的信號(hào)。

3.3 USB協(xié)議層

協(xié)議層主要分成三個(gè)子模塊:解包模塊、打包模塊和協(xié)議引擎模塊。這一層主要是將經(jīng)過(guò)串口接口引擎模塊過(guò)來(lái)的數(shù)據(jù)進(jìn)行解包,剔除USB協(xié)議中的信息。同時(shí)將端點(diǎn)中要發(fā)送的數(shù)據(jù),在協(xié)議引擎控制下進(jìn)行相應(yīng)的打包,然后通過(guò)SIE模塊傳送給USB主機(jī)。 3.3.1 解包模塊

本模塊主要將接收到的信息包數(shù)據(jù)進(jìn)行解析,解析出包標(biāo)識(shí)(PID),端點(diǎn)地址和USB設(shè)備地址以及包含在包中的有效數(shù)據(jù)。在解包時(shí),對(duì)令牌包進(jìn)行CRC5校驗(yàn),對(duì)數(shù)據(jù)包進(jìn)CRCl6檢驗(yàn),若出錯(cuò)則進(jìn)行相應(yīng)的出錯(cuò)處理。從上面所述可知,任何包都有同步字段而同步字段在串口接口引擎模塊中已經(jīng)除去了,因此本模塊不用關(guān)心同步字段。整個(gè)解包數(shù)據(jù)流如圖3所示。

整個(gè)解包過(guò)程如下:首先判斷接收的包是什么包,若為TOKEN包(0UT或IN或SOF或SETUP或ACK或NAK或STALL或PRE)則轉(zhuǎn)入到TOKEN包的處理進(jìn)程,若為數(shù)據(jù)包(DATA0或DATAl)則轉(zhuǎn)入到DATA包的處理進(jìn)程。在TOKEN包或DATA包中若發(fā)現(xiàn)數(shù)據(jù)有錯(cuò)則丟棄此包并報(bào)錯(cuò)。

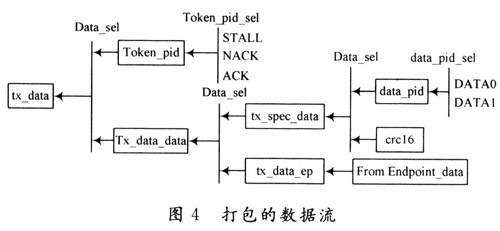

3.3.2 打包模塊

根據(jù)PE送來(lái)的PID組織相應(yīng)的信息包,把要發(fā)送的數(shù)據(jù)安排在相應(yīng)的數(shù)據(jù)包,或者組織令牌包。發(fā)送令牌包時(shí),不必產(chǎn)生CRC5校驗(yàn)位。在發(fā)送數(shù)據(jù)包時(shí),需要把有效數(shù)據(jù)的CRCl6校驗(yàn)位放在末尾一起發(fā)送。這個(gè)模塊主要就是如何把協(xié)議層引擎模塊送過(guò)來(lái)的數(shù)據(jù)進(jìn)行打包,打包的概念其實(shí)質(zhì)就是把要發(fā)送的數(shù)據(jù)根據(jù)其相應(yīng)的信息安排相應(yīng)的發(fā)送順序。同樣打包的過(guò)程中也不用考慮同步字段,同步字段在串口接口引擎層加入。整個(gè)打包數(shù)據(jù)流如圖4所示。

3.3.3 協(xié)議層引擎模塊

在USB設(shè)備中,某一個(gè)時(shí)刻和主機(jī)通信的只能是一個(gè)端點(diǎn),當(dāng)前操作都基于這個(gè)端點(diǎn)地址。主機(jī)不能同時(shí)和幾個(gè)端點(diǎn)進(jìn)行通信,端點(diǎn)的屬性在設(shè)備和主機(jī)剛開(kāi)始連接時(shí)進(jìn)行的枚舉過(guò)程中已經(jīng)確定,保存在各端點(diǎn)對(duì)應(yīng)的寄存器中,比如是IN還是OUT端點(diǎn),是支持控制傳輸、批量傳輸還是中斷傳輸?shù)亩它c(diǎn)等。協(xié)議引擎模塊是整個(gè)協(xié)議層的核心控制單元,控制了其他所有模塊的工作方式,根據(jù)當(dāng)前端點(diǎn)的配置或當(dāng)前狀態(tài)處理傳輸事務(wù),并在傳輸事務(wù)中實(shí)時(shí)更新控制與狀態(tài)寄存器。他的功能包括:有效處理IN,OUT和SETUP事務(wù),確定當(dāng)前傳輸事務(wù)要操作的端點(diǎn)地址,正確應(yīng)答各種包和管理數(shù)據(jù)的發(fā)送和接收,同時(shí)實(shí)現(xiàn)USB協(xié)議中的錯(cuò)誤恢復(fù)機(jī)制。

3.4 端點(diǎn)控制模塊和端點(diǎn)模塊

端點(diǎn)模塊:端點(diǎn)其實(shí)就是USB進(jìn)行通信時(shí),用于存數(shù)據(jù)的緩沖區(qū),為了提高數(shù)據(jù)存取的速度,本IP核的端點(diǎn)設(shè)計(jì)成FIFO。端點(diǎn)控制模塊:主要是端點(diǎn)控制寄存器和端點(diǎn)狀態(tài)寄存器,此模塊中包含了USB IP核的頂層控制和狀態(tài)寄存器。如USB設(shè)備的狀態(tài)控制寄存器、設(shè)備地址寄存器、中斷屏蔽寄存器和中斷源寄存器等。為了增加靈活性,在設(shè)計(jì)時(shí)針對(duì)每一個(gè)端點(diǎn)分別設(shè)計(jì)了設(shè)置和功能相同但地址不同的寄存器,包括端點(diǎn)的控制狀態(tài)寄存器、中斷源寄存器、中斷屏蔽寄存器、緩沖區(qū)的指針寄存器。端點(diǎn)根據(jù)協(xié)議可以配置1到16個(gè),在實(shí)際設(shè)計(jì)中根據(jù)本身系統(tǒng)需要可以對(duì)USB IP核配置端點(diǎn)數(shù),增加了USB IP核端點(diǎn)可擴(kuò)展性。

3.5 總線適配器模塊

此模塊是為了提高本IP核的可重用性而設(shè)計(jì)的。他主要包括WishBone總線接口、AMBA ASB總線接口和相應(yīng)的配置寄存器。若使用于WishBone總線結(jié)構(gòu)的SoC中,則在綜合前通過(guò)宏定義進(jìn)行設(shè)置啟用WishBone總線接口,這樣整個(gè)USB IP核可以無(wú)縫接入WishBone總線結(jié)構(gòu)的SoC中。若使用于AMBA ASB總線結(jié)構(gòu)的SoC中,則在綜合前通過(guò)宏定義進(jìn)行設(shè)置啟用AMBA總線接口無(wú)縫接入其SoC中。由于是在綜合前通過(guò)宏定義的,因此在實(shí)際綜合的時(shí)候,只會(huì)將宏定義的總線模塊綜合成實(shí)際電路,而不會(huì)兩個(gè)總線接口模塊都給綜合,節(jié)省資源。同時(shí)當(dāng)此IP核要應(yīng)用于其他的總線結(jié)構(gòu)SoC中,如Altera的Avalon總線,則只要根據(jù)此總線協(xié)議再設(shè)計(jì)一個(gè)總線接口模塊,在綜合時(shí)啟用此總線接口模塊就可以將此IP核直接應(yīng)用于此SoC中。因此本USB IP核對(duì)于不同總線的SoC利用總線適配器使具體較強(qiáng)靈活性,可重用性強(qiáng)。

4 FPGA驗(yàn)證

本USB IP核已經(jīng)應(yīng)用于一款數(shù)據(jù)采集單芯片系統(tǒng)中。因此在進(jìn)行FPGA驗(yàn)證時(shí),是將此IP核嵌入于此單芯片系統(tǒng)中進(jìn)行的。此單芯片系統(tǒng)中嵌入U(xiǎn)ART模塊可與PC機(jī)的串口進(jìn)行通信,此系統(tǒng)中的增強(qiáng)型8051MCU核對(duì)整個(gè)USB IP核進(jìn)行相應(yīng)的控制。FPGA驗(yàn)證采用了Xilinx公司的ISE集成開(kāi)發(fā)環(huán)境,在調(diào)試的過(guò)程中用了ChipSeope Pro軟邏輯分析儀。硬件平臺(tái)用Xilinx公司的Virtex4系列中XC4VLX60器件。

整個(gè)過(guò)程如下:

(1)USB從設(shè)備與PC機(jī)的USB接口連接,此時(shí)USB從設(shè)備要完成設(shè)備枚舉的過(guò)程。

(2)設(shè)備枚舉完成PC機(jī)會(huì)提示驅(qū)動(dòng)程序還沒(méi)有裝,要求加載驅(qū)動(dòng)程序在PC機(jī)上加驅(qū)動(dòng)程序,USB的驅(qū)動(dòng)程序直接與PC機(jī)的操作系統(tǒng)聯(lián)系,項(xiàng)目中的USB接口是在Windows XP操作系統(tǒng)中調(diào)試的。

(3)在驅(qū)動(dòng)程序加載完成后,PC機(jī)會(huì)提示“現(xiàn)在可以正常通訊”,表明現(xiàn)在可以利用USB的應(yīng)用層軟件進(jìn)行通信了。

(4)將數(shù)據(jù)從PC機(jī)的應(yīng)用層輸入,通過(guò)USB接口發(fā)給嵌入U(xiǎn)SB IP核的數(shù)據(jù)采集SoC芯片,然后通過(guò)其中的SoC中UART將數(shù)據(jù)返回給PC機(jī),經(jīng)過(guò)比較兩者數(shù)據(jù)完全相同,驗(yàn)證表明了此IP核的正確。

圖5是在進(jìn)行IP核FPGA驗(yàn)證時(shí),設(shè)備枚舉階段PC的USB主機(jī)發(fā)送給USB IP核的幀開(kāi)始(SOF)包。

fs_clk為從PC機(jī)發(fā)過(guò)來(lái)的比特流恢復(fù)過(guò)來(lái)的12 MHz的時(shí)鐘信號(hào)。rx_data表示收到的數(shù)據(jù),如圖5所示在rx_valid高電平時(shí),表明收到的rx_data是有效的,從圖中可以看出收到了十六進(jìn)制數(shù)“A5—43—85”,此包正是PC機(jī)發(fā)給USB IP核的SOF包。rxdp和rx_dn是串口接口引擎模塊中的信號(hào),他經(jīng)過(guò)一個(gè)三態(tài)門與圖1所示的D+和D一相連接。由圖中可以看出,在“85”收到時(shí),rxdp和rx_dn的波形表明收到了PC機(jī)發(fā)過(guò)來(lái)的兩個(gè)fS_clk時(shí)鐘周期的"SE0”表示包結(jié)束的信號(hào)。

5 結(jié) 語(yǔ)

本USB IP核在設(shè)計(jì)時(shí),充分考慮到可重用性,其USB端點(diǎn)可進(jìn)行相應(yīng)的配置和擴(kuò)展。同時(shí)針對(duì)目前SoC中常用的WishBone總線和AMBA ASB總線結(jié)構(gòu)設(shè)計(jì)了總線適配器,在綜合前進(jìn)行相關(guān)的宏定義就可以無(wú)縫接入SoC中。本USB IP核在實(shí)際項(xiàng)目中,與MCU核以及其他的IP核集成于一款數(shù)據(jù)采集SoC芯片中,該數(shù)據(jù)采集SoC已經(jīng)處于版圖后仿真階段,即將流片。