液晶顯示器由于具有低壓、微功耗、顯示信息量大、體積小等特點(diǎn),在移動(dòng)通信終端、便攜計(jì)算機(jī)、GPS衛(wèi)星定位系統(tǒng)等領(lǐng)域有廣泛用途,成為使用量最大的顯示器件。液晶顯示控制器作為液晶驅(qū)動(dòng)電路的核心部件通常由集成電路組成,通過(guò)為液晶顯示系統(tǒng)提供時(shí)序信號(hào)和顯示數(shù)據(jù)來(lái)實(shí)現(xiàn)液晶顯示。本設(shè)計(jì)是一種基于FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)的液晶顯示控制器。與集成電路控制器相比,F(xiàn)PGA更加靈活,可以針對(duì)小同的液晶顯示模塊更改時(shí)序信號(hào)和顯示數(shù)據(jù)。FPGA的集成度、復(fù)雜度和面積優(yōu)勢(shì)使得其日益成為一種頗具吸引力的高性價(jià)比ASIC替代方案。本文選用Xilinx公司的Spartan3系列XC3S200器件,利用硬件描述語(yǔ)言Verilog設(shè)計(jì)了液晶顯示擰制器,實(shí)現(xiàn)了替代專用集成電路驅(qū)動(dòng)控制LCD的作用。

1 功能分析與設(shè)計(jì)要求

液晶顯示模塊(LCM)采用深圳拓?fù)湮M2028、STN圖形點(diǎn)陣液晶顯示模塊,5.7in,320×240點(diǎn)陣,邏輯電壓輸入為3.0~5.0V,4位控制接口,具有行列驅(qū)動(dòng)電路,白光LED背光源。表l為該液晶顯示模塊的引腳功能描述。

液晶顯示器的掃描方式是逐行掃描,當(dāng)一行被選通以后,這一行中的各列信號(hào)同時(shí)加到列上,并維持一個(gè)掃描行的時(shí)間。這一行維持時(shí)間結(jié)束后,即選通下一行,同時(shí)各列電極也施加下一行的顯示電壓。

列驅(qū)動(dòng)器邏輯電路由移位寄存器和鎖存器構(gòu)成,在一個(gè)顯示數(shù)據(jù)位移脈沖信號(hào)CP作用下,將一組顯示數(shù)據(jù)(4位)位移到寄存器中并保持。當(dāng)下一個(gè)CP到來(lái)后。移位寄存器中第1位顯示數(shù)據(jù)被移至第2位,這樣在80個(gè)CP脈沖作用下,一行顯示數(shù)據(jù)被存入寄存器后,寄存器并口對(duì)接鎖存器,在鎖存脈沖LP的作用下,該行數(shù)據(jù)被鎖存到鎖存器內(nèi)輸出給列電極。鎖存脈沖LP的間隔為一個(gè)行周期,而行移位脈沖間隔也為一個(gè)行周期,因此二者是一致的。

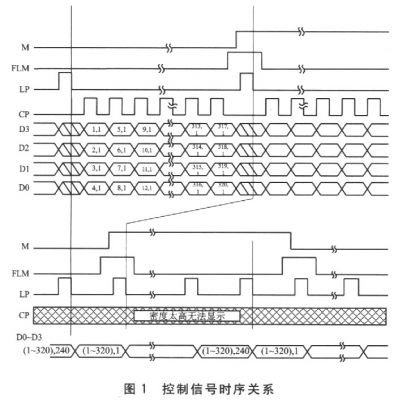

幀掃描信號(hào)FLM即為行選通信號(hào),脈寬為一行時(shí)間,在行移位脈沖LP作用下,存入移位寄存器后逐行位移,在一幀的最后一行輸出高電平,代表下一幀的開(kāi)始。M為液晶顯示交流驅(qū)動(dòng)波形信號(hào),即一幀改變一次波形的極性,防止液晶單方向扭曲變形。更為詳細(xì)的時(shí)序關(guān)系如圖1所示。

2 設(shè)計(jì)與實(shí)現(xiàn)

2.1 液晶控制器總體設(shè)計(jì)

本設(shè)計(jì)的液晶顯示器刷新頻率為70 Hz,每一幀周期為14.28ms,每一行周期為60μs,時(shí)鐘信號(hào)CP的頻率為2 MHz,將一行數(shù)據(jù)輸入列移位寄存器的時(shí)間為40μs,因此每一行設(shè)計(jì)了20μs的空白時(shí)間。

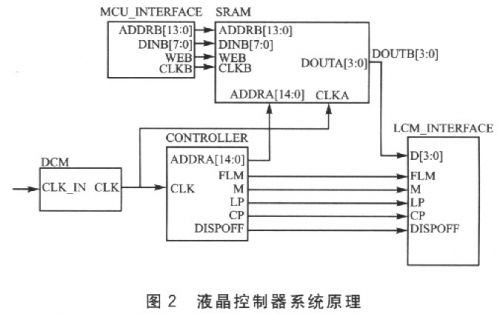

液晶控制器系統(tǒng)原理如圖2所示。時(shí)鐘模塊采用Xilinx公司的Coregen IP工具定制,數(shù)字時(shí)鐘管理器DCM模塊將FPGA 50 MHz時(shí)鐘信號(hào)CLK_IN 25分頻為2 MHz控制器時(shí)鐘信號(hào)CLK。DCM采用了數(shù)字延遲鎖相環(huán)技術(shù)來(lái)消除時(shí)鐘相位的位移,提供比自行分頻更穩(wěn)定的時(shí)鐘信號(hào),以滿足控制系統(tǒng)要求。CONTROLLER模塊為L(zhǎng)CM提供滿足圖l所示時(shí)序要求的控制信號(hào)CP、LP、FLM、M、DISPOFF,并且同步產(chǎn)生SRAM的讀地址ADDRA[14:0]。

SRAM為內(nèi)存模塊。為了提高輸入LCD的數(shù)據(jù)流速度.設(shè)計(jì)了32K×4位的艤端口內(nèi)存,可同時(shí)實(shí)現(xiàn)讀/寫(xiě),并實(shí)現(xiàn)數(shù)據(jù)格式的轉(zhuǎn)化,由上位機(jī)MCU輸入的8位數(shù)據(jù)轉(zhuǎn)為輸入LCM列驅(qū)動(dòng)器的4位數(shù)據(jù);B端口由MCU_INTERFACE與上位機(jī)MCU連接,由MCU微控制器將顯示數(shù)據(jù)寫(xiě)入內(nèi)存SRAM。其中,ADDRB[13:0]控制16K×8位的寫(xiě)地址,DINB[7:O]為寫(xiě)入數(shù)據(jù),WEB為寫(xiě)有效控制,CLKB為寫(xiě)時(shí)鐘;A端口由CONTROLLER模塊控制讀地址ADDRA[14:0],讀時(shí)鐘CLKA由系統(tǒng)時(shí)鐘信號(hào)CLK控制,DOUTA[3:0]將數(shù)據(jù)寫(xiě)入LCM列驅(qū)動(dòng)器。

2.2 控制模塊設(shè)計(jì)

應(yīng)用狀態(tài)機(jī)的方法,用Verilog硬件描述語(yǔ)言設(shè)計(jì)控制模塊CONTROLLER。CLK為2 MHz輸入時(shí)鐘信號(hào)。LP和內(nèi)部控制信號(hào)DEN由狀態(tài)機(jī)1控制產(chǎn)生,F(xiàn)LM由狀態(tài)機(jī)2控制產(chǎn)生,M由狀態(tài)機(jī)3控制產(chǎn)生,CP信號(hào)和ADDRA[14:0]根據(jù)CLK和DEN信號(hào)控制得到。狀態(tài)機(jī)1有3個(gè)狀態(tài):狀態(tài)1,LP為O,DEN為1,持續(xù)80個(gè)CLK脈沖后轉(zhuǎn)向狀態(tài)2;狀態(tài)2,LP為l,DEN為0,持續(xù)1個(gè)CLK脈沖后轉(zhuǎn)向狀態(tài)3;狀態(tài)3,LP為O,DEN為O,持續(xù)39個(gè)CLK脈沖后轉(zhuǎn)向狀態(tài)1。狀態(tài)機(jī)2有2個(gè)狀態(tài):狀態(tài)1,F(xiàn)LM為l,持續(xù)1個(gè)LP周期時(shí)間,即120個(gè)CLK脈沖;狀態(tài)2,F(xiàn)LM為O,持續(xù)剩下的239個(gè)LP周期,即28 680個(gè)CLK脈沖。狀態(tài)機(jī)3有2個(gè)狀態(tài),狀態(tài)l,M為1。持續(xù)1個(gè)FLM周期時(shí)間,即28800個(gè)CLK脈沖;狀態(tài)2,M為0,也持續(xù)1個(gè)FLM周期時(shí)間。CP信號(hào)和ADDRA由于含有空白信號(hào),所以由內(nèi)部控制信號(hào)DEN和時(shí)鐘信號(hào)CLK得到。以下為設(shè)計(jì)的源代碼初始化部分:

3 仿真、下載測(cè)試分析

在ISE6.3環(huán)境下完成控制器設(shè)計(jì)后,在MODELSIM6.1b環(huán)境下完成仿真測(cè)試,波形如圖3所示。

仿真波形結(jié)果符合設(shè)計(jì)要求。完成仿真后,經(jīng)過(guò)綜合實(shí)現(xiàn),生成編程文件并且通過(guò)下載軟件實(shí)現(xiàn)對(duì)Xilinx公司FPGA器件XC3S200編程,并用泰克邏輯分析儀TLA721分析測(cè)試,所得結(jié)果如圖4所示。

圖4中各控制信號(hào)之間的時(shí)序關(guān)系完全符合設(shè)計(jì)要求。測(cè)得一個(gè)CP脈沖周期為500ns,在每行結(jié)束處有40個(gè)CP脈沖周期約20μs的空白信號(hào);LP周期為60μs,高電平持續(xù)時(shí)間為500 ns,即一個(gè)CP周期;FLM周期為14.28 ms,約為70 Hz,高電平持續(xù)時(shí)間為60μs,即1個(gè)LP周期。測(cè)試結(jié)果表明,本設(shè)計(jì)液晶控制器完全符合LCM對(duì)控制信號(hào)的要求。

結(jié)語(yǔ)

利用硬件描述語(yǔ)言Verilog設(shè)計(jì)LCM控制器的方法,具有減小電路板尺寸、易于集成到片上系統(tǒng)、縮小系統(tǒng)體積、方便修改、適應(yīng)不同液晶顯示器等特點(diǎn),具有很好的可重用性;同時(shí)也是后續(xù)開(kāi)發(fā)其他種類液晶顯示控制器的基礎(chǔ)。

本液晶顯示控制器與MCU組成顯示系統(tǒng)后,MCU將顯示數(shù)據(jù)寫(xiě)入SRAM中,控制器將顯示數(shù)據(jù)讀出并與控制信號(hào)同步送入LCM中,很好地實(shí)現(xiàn)了圖形顯示。表明該液晶顯示控制器成功地替代了傳統(tǒng)的ASIC液晶控制器,具有良好的應(yīng)用前景。

本文來(lái)源于與非網(wǎng) http://www.eefocus.com

原文地址:http://www.eefocus.com/article/10-09/2075521285834790.html