FPGA/EPLD的自上而下(Top-Down)設(shè)計(jì)方法:

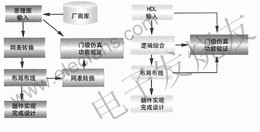

傳統(tǒng)的設(shè)計(jì)手段是采用原理圖輸入的方式進(jìn)行的,,如圖1所示。通過調(diào)用FPGA/EPLD廠商所提供的相應(yīng)物理元件庫,,在電路原理圖中繪制所設(shè)計(jì)的系統(tǒng),,然后通過網(wǎng)表轉(zhuǎn)換產(chǎn)生某一特定FPGA/EPLD廠商布局布線器所需網(wǎng)表,通過布局布線,,完成設(shè)計(jì),。原理圖繪制完成后可采用門級(jí)仿真器進(jìn)行功能驗(yàn)證。

圖1:傳統(tǒng)的設(shè)計(jì)手段與Top-Down設(shè)計(jì)工具的比較

然而,,工程師的最初設(shè)計(jì)思想不是一開始就考慮采用某一FPGA/EPLD廠商的某一特定型號(hào)器件,,而是從功能描述開始的。設(shè)計(jì)工程師首先要考慮規(guī)劃出能完成某一具體功能,、滿足自己產(chǎn)品系統(tǒng)設(shè)計(jì)要求的某一功能模塊,,利用某種方式(如HDL硬件描述語言)把功能描述出來,通過功能仿真(HDL仿真器)以驗(yàn)證設(shè)計(jì)思路的正確性,。當(dāng)所設(shè)計(jì)功能滿足需要時(shí),,再考慮以何種方式(即邏輯綜合過程)完成所需要的設(shè)計(jì),并能直接使用功能定義的描述,。實(shí)際上這就是自頂而下設(shè)計(jì)方法,。

與傳統(tǒng)電原理圖輸入設(shè)計(jì)方法相比,Top-Down設(shè)計(jì)方法具體有以下優(yōu)點(diǎn):

1,、完全符合設(shè)計(jì)人員的設(shè)計(jì)思路,,從功能描述開始,,到物理實(shí)現(xiàn)的完成。

2,、功能設(shè)計(jì)可完全獨(dú)立于物理實(shí)現(xiàn)

在采用傳統(tǒng)的電原理輸入方法時(shí),,F(xiàn)PGA/EPLD器件的采用受到器件庫的制約。由于不同廠商FPGA/EPLD的結(jié)構(gòu)完全不同,,甚至同一廠商不同系列的產(chǎn)品也存在結(jié)構(gòu)上的差別,,因此,在設(shè)計(jì)一開始,,工程師的設(shè)計(jì)思路就受到最終所采用器件的約束,,大大限制了設(shè)計(jì)師的思路和器件選擇的靈活性。而采用Top-Down設(shè)計(jì)方法,,功能輸入采用國(guó)際標(biāo)準(zhǔn)的HDL輸入方法,,HDL可不含有任何器件的物理信息,因此工程師可以有更多的空間去集中精力進(jìn)行功能描述,,設(shè)計(jì)師可以在設(shè)計(jì)過程的最后階段任意選擇或更改物理器件,。

3、設(shè)計(jì)可再利用

設(shè)計(jì)結(jié)果完全可以以一種知識(shí)產(chǎn)權(quán)(IP-Intellectual Property)的方式作為設(shè)計(jì)師或設(shè)計(jì)單位的設(shè)計(jì)成果,,應(yīng)用于不同的產(chǎn)品設(shè)計(jì)中,,做到成果的再利用。

4,、易于設(shè)計(jì)的更改

設(shè)計(jì)工程師可在極短的時(shí)間內(nèi)修改設(shè)計(jì),,對(duì)各種FPGA/EPLD結(jié)構(gòu)進(jìn)行設(shè)計(jì)結(jié)果規(guī)模(門消耗)和速度(時(shí)序)的比較,選擇最優(yōu)方案,。

5,、設(shè)計(jì)、處理大規(guī)模,、復(fù)雜電路

目前的FPGA/EPLD器件正向高集成度,、深亞微米工藝發(fā)展。為設(shè)計(jì)系統(tǒng)的小型化,,低功耗,、高可靠性等提供了集成的手段。設(shè)計(jì)低于一萬門左右的電路,,Top-Down設(shè)計(jì)方法具有很大的幫助,,而設(shè)計(jì)更大規(guī)模的電路,Top-Down設(shè)計(jì)方法則是必不可少的手段,。

6,、設(shè)計(jì)周期縮短,生產(chǎn)率大大提高,,產(chǎn)品上市時(shí)間提前,,性能明顯提高,,產(chǎn)品競(jìng)爭(zhēng)力加強(qiáng)。據(jù)統(tǒng)計(jì),,采用Top-Down設(shè)計(jì)方法的生產(chǎn)率可達(dá)到傳統(tǒng)設(shè)計(jì)方法的2到4倍,。

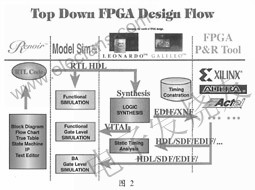

Top-Down設(shè)計(jì)流程如圖2所示,其核心是采用HDL語言進(jìn)行功能描述,,由邏輯綜合(Logic Synthesis)把行為(功能)描述轉(zhuǎn)換成某一特定FPGA/EPLD的工藝網(wǎng)表,,送到廠商的布局布線器完成物理實(shí)現(xiàn)。在設(shè)計(jì)過程的每一個(gè)環(huán)節(jié),,仿真器的功能驗(yàn)證和門級(jí)仿真技術(shù)保證設(shè)計(jì)功能和時(shí)序的正確性,。

FPGA/EPLD To p-Down 設(shè)計(jì)工具的黃金組合

Mentor Graphics公司提供一整套基于UNIX平臺(tái)和Windows 95/NT 平臺(tái)的FPGA/EPLD Top-Down設(shè)計(jì)工具:Renoir/ModelSim 和Exemplar,如圖2所示,。兩種平臺(tái)的工具具有相同的用戶界面,,并保證數(shù)據(jù)庫的完全統(tǒng)一。目前,,在FPGA/EPLD Top-Down設(shè)計(jì)方法全球市場(chǎng)上,,Mentor已擁有42%的市場(chǎng)份額,遠(yuǎn)遠(yuǎn)領(lǐng)先于其他任何一個(gè)廠家,。

采用Top-Down設(shè)計(jì)方法進(jìn)行FPGA/EPLD設(shè)計(jì),,其設(shè)計(jì)結(jié)果的優(yōu)劣與否取決于三個(gè)重要的因素:描述手段(即HDL語言)、設(shè)計(jì)方法(Style)和設(shè)計(jì)工具,。描述手段是基礎(chǔ),設(shè)計(jì)方法需要工程經(jīng)驗(yàn),,而設(shè)計(jì)工具則是Top-Down設(shè)計(jì)的關(guān)鍵,。一套完整、強(qiáng)大,、性能卓越的設(shè)計(jì)工具,,可幫助設(shè)計(jì)工工程師最大限度的發(fā)揮其設(shè)計(jì)能力。

1. 圖形化輸入工具-Renoir

----設(shè)計(jì)工程師采用Top-Down方法進(jìn)行FPGA/EPLD設(shè)計(jì)所面臨到的第一個(gè)問題就是HDL語言的學(xué)習(xí),。語言的學(xué)習(xí)過程和應(yīng)用能力直接影響設(shè)計(jì)產(chǎn)品的完成及其性能,。但是設(shè)計(jì)師進(jìn)行產(chǎn)品設(shè)計(jì)的最初并不是考慮如何去寫語言,而是習(xí)慣于畫出設(shè)計(jì)的框圖,,并采用圖形化方法(流程圖,、狀態(tài)圖、真值表等)把它描述出來,。Renoir這一圖形化輸入工具,,不僅可以幫助設(shè)計(jì)師完成產(chǎn)品的功能描述,更可以自動(dòng)生成HDL語言,,為邏輯綜合提供必要的輸入數(shù)據(jù),。

---- 采用圖形化輸入方法主要優(yōu)點(diǎn)體現(xiàn)在:

提供框圖,、流程圖、狀態(tài)圖,、真值表等圖形輸入方法,,使設(shè)計(jì)工程師從純文本的設(shè)計(jì)方法理解脫出來,設(shè)計(jì)手段更貼近于設(shè)計(jì)師的思維過程:

便于工程師之間進(jìn)行設(shè)計(jì)的相互交流以及對(duì)前人/他人設(shè)計(jì)結(jié)果的理解與再利用; 便于初學(xué)者學(xué)習(xí)HDL語言;

便于設(shè)計(jì)成果的存檔,,以便設(shè)計(jì)交流與再利用,。

---- Renoir作為新一代的圖形化輸入工具更具有以下諸多優(yōu)點(diǎn):

自動(dòng)生成高效的HDL語言描述,生成結(jié)果可進(jìn)行功能驗(yàn)證及邏輯綜合;

完全支持VHDL和Verilog兩種國(guó)際標(biāo)準(zhǔn),,并完全支持VHDL/Verilog的混合描述;

支持UNIX和Win95/NT兩種平臺(tái),,具有相同界面和數(shù)據(jù)庫。Win95/NT平臺(tái)采用標(biāo)準(zhǔn)的Windows界面,,易學(xué)易用;

支持框圖/流程圖的動(dòng)畫(Animation)仿真,、調(diào)試過程便于設(shè)計(jì)的調(diào)試;

即插即用(plug and play),與多種仿真器,、綜合器及軟硬件協(xié)同驗(yàn)證工具有完善的接口,,組成各種設(shè)計(jì)流程;

在線查錯(cuò)功能(On line checking),進(jìn)行語法和可綜合性檢查; 語言到圖形的轉(zhuǎn)換,,可以把VHDL,、Verilog或混合HDL語言描述換成框圖、流程圖或狀態(tài)圖,,并保持原設(shè)計(jì)的層次結(jié)構(gòu);

支持OLE(Object Liking and Embedding)標(biāo)準(zhǔn),,可把Renoir中的任何圖形設(shè)計(jì)形式連接或嵌入到任一支持OLE的應(yīng)用程序中,如Word,、Powerpoint等,,以便用戶建立設(shè)計(jì)文檔;

支持在圖形輸入中加入注釋、屬性(pragma,, attribute),、并可自動(dòng)加到所產(chǎn)生的HDL源碼中;

支持IP調(diào)用,并可自動(dòng)生成相應(yīng)符號(hào),,以使IP嵌入到所設(shè)計(jì)的系統(tǒng)中;

完善的設(shè)計(jì)管理,,支持設(shè)計(jì)項(xiàng)目管理、設(shè)計(jì)層次管理,、設(shè)計(jì)小組管理及設(shè)計(jì)數(shù)據(jù)版本管理等;

通過需求與設(shè)計(jì)可跟蹤(Requirement & Tracebility)管理,,不僅保證設(shè)計(jì)正確,而且保證正確設(shè)計(jì)(Design thing Right and Design Right thing),。

2. 邏輯綜合工具-Exemplar

---- 邏輯綜合工具是通過映射和優(yōu)化過程,,把設(shè)計(jì)功能描述轉(zhuǎn)換成與物理實(shí)現(xiàn)密切相關(guān)的工藝網(wǎng)表。在轉(zhuǎn)換過程中,,不僅需要確保每一功能映射正確,還需保證盡量采用較少的硬件開銷,滿足設(shè)計(jì)的時(shí)序要求,。因此,邏輯綜合工具是FPGA/EPLD Top-Down設(shè)計(jì)過程的關(guān)鍵,。 Exemplar的主要特點(diǎn):

完全支持VHDL/Verilog兩種國(guó)際標(biāo)準(zhǔn);

針對(duì)不同結(jié)構(gòu)的FPGA/EPLD器件,采用不同的綜合優(yōu)化算法,,以保證結(jié)果的最優(yōu)化;

支持不同類型器件的重映射,,設(shè)計(jì)師可直接從一種器件的工藝網(wǎng)表映射到另一種器件的工藝網(wǎng)表,無需重新設(shè)計(jì);

支持各廠商器件網(wǎng)表的不同格式輸入與輸出,。如:XNF,,EDIF等:

支持布局、布線后設(shè)計(jì)的反標(biāo)注,,產(chǎn)生后仿真所需功能網(wǎng)表(HDL)及延時(shí)網(wǎng)表(SDF);

持靜態(tài)時(shí)序分析;

支持綜合結(jié)果的圖形輸出,,設(shè)計(jì)師可通過圖形輸出跟蹤分析關(guān)鍵路徑(Critical Path);

支持廣泛的FPGA廠商及其最新芯片型號(hào),包括采用深亞微米技術(shù)的器件,。廠商包括:Actel,、Altera、Atmel,、Cypress,、Lattice、Lucent,、Motorola,、Quicklogic、Xilinx等;

FPGA/EPLD設(shè)計(jì)到ASIC設(shè)計(jì)可實(shí)現(xiàn)無縫升級(jí),,保證設(shè)計(jì)數(shù)據(jù)的兼容性及可再利用性;

即插即用,,可與各種前端/后端工具結(jié)合使用,設(shè)計(jì)數(shù)據(jù)無虛人為干預(yù)/修改;

持UNIX平臺(tái)和Win95/NT平臺(tái),,不同平臺(tái)工具具有相同的用戶界面、功能,、并完全保證設(shè)計(jì)數(shù)據(jù)的兼容性,。

3. 功能仿真與時(shí)序驗(yàn)證-ModelSim

---- 在FPGA/EPLD Top-Down設(shè)計(jì)流程中,設(shè)計(jì)仿真包含在設(shè)計(jì)過程的每一環(huán)節(jié)中,,以保證設(shè)計(jì)的正確性,。 ModelSim不僅可以完成設(shè)計(jì)的功能驗(yàn)證(RTL級(jí)),也可實(shí)現(xiàn)邏輯綜合后的門級(jí)仿真以及布局布線后的功能和時(shí)序驗(yàn)證,。

---- ModelSim的主要特點(diǎn):

完全支持VHDL和Verilog標(biāo)準(zhǔn);

采用直接編輯技術(shù)(Direct-Compiled),,大大提高HDL編譯和仿真速度;

唯一支持VHDL和Verilog混合描述的仿真工具;

支持RTL級(jí)和門級(jí)驗(yàn)證,支持VITAL,,SDF等;

具有友好的用戶界面,,仿真器包括主控窗口,、源碼窗口、仿真波形窗口,、列表窗口,、數(shù)據(jù)流窗口、設(shè)計(jì)結(jié)構(gòu)/層次窗口,、過程管理窗口等;

支持單步調(diào)試,,斷點(diǎn)設(shè)置,批命令處理方式,,幫助設(shè)計(jì)師快速完成設(shè)計(jì)調(diào)試和驗(yàn)證;

可與Renoir協(xié)同工作,,完成狀態(tài)圖和流程圖的動(dòng)畫調(diào)試;

即插即用,可與其它工具結(jié)合,,完成各種流程;

支持UNIX和Window 95/NT平臺(tái),,不同平臺(tái)間具有相同的用戶界面和數(shù)據(jù)庫。