位于840MHz左右的RF干擾影響配置成UART" title="UART">UART的串行通信端口" title="通信端口">通信端口,該接口位于包含一個(gè)AD6903(LeMansLCR+)數(shù)字式基帶處理器的調(diào)制解調(diào)器和一臺(tái)主處理機(jī)之間。

出現(xiàn)的問題是連接到AD6903GPIO_1引腳的UARTRX信號(hào)中出現(xiàn)噪聲,每當(dāng)射頻(RF)干擾源出現(xiàn)時(shí),信號(hào)平均電壓就會(huì)遠(yuǎn)離其期望值。平均電壓的偏移幅度取決于RF源的功率和頻率。

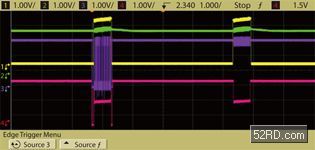

圖1顯示當(dāng)射頻功率放大器接通時(shí),進(jìn)入AD6903的GPIO_1引腳上的UARTRX信號(hào)受到影響的情況。在圖1中,進(jìn)入AD6903的UARTRX用粉紅色表示,來自主處理機(jī)的UARTTX信號(hào)用紫色表示,功率放大器使能用黃色表示,而AD6903VEXT電源用綠色表示。

圖1:UART通信端口上的RF干擾

當(dāng)功率放大器接通(黃色)時(shí),從主處理器的TX引腳到AD6903的RX引腳(桃紅色)的UART數(shù)據(jù)傳輸發(fā)生了故障,因?yàn)镽X信號(hào)上升到高低電平之間的中間位置,而與TX信號(hào)(紫色)不一致。在第二個(gè)脈沖期間,當(dāng)功率放大器接通時(shí),主處理器的TX引腳和AD6903的RX引腳應(yīng)該都保持高電平;但是TX引腳上有噪聲,而且RX信號(hào)下降至其高低電平的中間位置。并且注意VEXT電源電壓(綠色)上的噪聲增大,并且當(dāng)功率放大器接通時(shí)其值還會(huì)略為上升。

然而,問題必須是與功率放大器的使能信號(hào)和同一個(gè)調(diào)制解調(diào)器的功率放大器無關(guān),因?yàn)閺母浇渌碾娫捇蛐盘?hào)發(fā)生器帶來的RF能量也會(huì)影響進(jìn)入AD6903的UARTRX信號(hào)。使用信號(hào)產(chǎn)生器掃描來檢查對(duì)射頻干擾" title="射頻干擾">射頻干擾的易受度時(shí)發(fā)現(xiàn),最壞的地方約在840MHz,而在高頻或更低的頻率上則較好。

在主處理器和AD6903之間的這個(gè)信號(hào)的串聯(lián)電阻器被用于使邏輯高電平從3.3V降低到2.8V。這個(gè)電阻器的額定阻值是10kΩ。可以用較小的電阻、包括0Ω電阻器來替換之,因?yàn)榻档妥柚悼梢詼p小噪聲,但是這并不能解決問題,除非用短路線來代替。

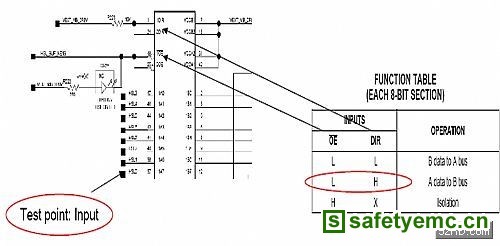

這個(gè)問題也不是AD6903才特有的。來自其他廠商的芯片也具有相似的現(xiàn)象。比如,SN74AVCA16425GR的引腳37上也有同樣的問題。其功能框圖請(qǐng)參考圖2。

圖2:SN74AVCA16425GR功能框圖

這里的1DIR、2DIR為高電平,OE為低電平,因此操作是從A口到B口,引腳37(1A7)將接收來自另一個(gè)芯片組的數(shù)據(jù)。這意味著它是輸入型。

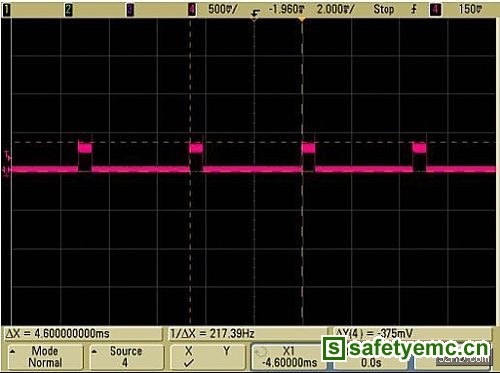

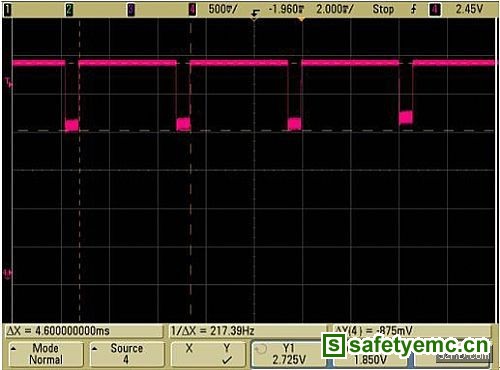

在附近存在RF干擾的情況下,即在測(cè)試點(diǎn)附近(5米以內(nèi))用手機(jī)打電話,來測(cè)試SN74AVCA16425GR的引腳37上的信號(hào)。圖3顯示當(dāng)設(shè)備不加電時(shí)(I/O狀態(tài)未知),其輸出反常;而圖4則顯示當(dāng)設(shè)備加電(輸入狀態(tài))時(shí)其輸出的反常情況。

圖3:低電平升高

干擾原理

進(jìn)入AD6903的UARTRX信號(hào)的這種“RF干擾拾取”行為的發(fā)生以一個(gè)特定的RF頻率為中心,而這些信號(hào)跡線沒有完全被屏蔽。這種現(xiàn)象是可以解釋的:主板的印刷導(dǎo)線拾取干擾,因?yàn)閷?dǎo)線上有寄生電感、寄生電阻和寄生電容,而導(dǎo)線的兩端連接的是高阻抗;一側(cè)是一個(gè)10kΩ電阻器,另一側(cè)則是CMOS輸入。電路板上的導(dǎo)線就像一個(gè)具有1/4波長響應(yīng)的天線。

圖4:高電平降低

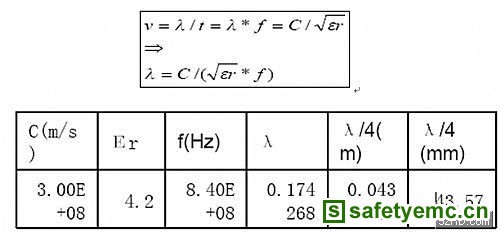

在客戶模塊中,計(jì)算GPIO1導(dǎo)線時(shí),模塊上按30mm計(jì)算,而主板上則大約為15mm。所以這條線能夠拾取RF噪聲并對(duì)840MHz敏感就不奇怪了。具體可以參考圖5。

圖5:RF干擾計(jì)算公式

根據(jù)上述理論,建議在信號(hào)通道上增加一只電容器來阻尼RF的干擾振蕩。電容器的作用是改變天線的調(diào)諧頻率和降低天線阻抗從而降低天線增益。隨后,我們聽取了有關(guān)報(bào)告,即通過選取適當(dāng)?shù)碾娙荩乖肼暅p少到了可接受的水平。