FPGA/CPLD在數(shù)字系統(tǒng)設計中的廣泛應用,影響到了生產生活的各個方面。在FPGA/CPLD的設計開發(fā)中,VHDL語言作為一種主流的硬件描述語言,具有設計效率高,可靠性好,易讀易懂等諸多優(yōu)點。作為一種功能強大的FPGA/CPLD數(shù)字系統(tǒng)開發(fā)環(huán)境,Altera公司推出的Quar-tUSⅡ,為設計者提供了一種與結構無關的設計環(huán)境,使設計者能方便地進行設計輸入、快速處理和器件編程,為使用VHDL語言進行FPGA/-CPLD設計提供了極大的便利。矩陣鍵盤作為一種常用的數(shù)據(jù)輸入設備,在各種電子設備上有著廣泛的應用,通過7段數(shù)碼管將按鍵數(shù)值進行顯示也是一種常用的數(shù)據(jù)顯示方式。在設計機械式矩陣鍵盤控制電路時,按鍵防抖和按鍵數(shù)據(jù)的譯碼顯示是兩個重要方面。本文在QuartusⅡ開發(fā)環(huán)境下,采用VHDL語言設計了一種按鍵防抖并能連續(xù)記錄并顯示8次按鍵數(shù)值的矩陣鍵盤及顯示電路。

1 矩陣鍵盤及顯示電路設計思路

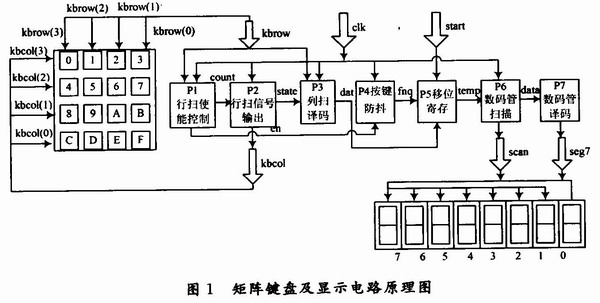

矩陣鍵盤及顯示電路能夠將機械式4×4矩陣鍵盤的按鍵值依次顯示到8個7段數(shù)碼管上,每次新的按鍵值顯示在最右端的第O號數(shù)碼管上,原有第0~6號數(shù)碼管顯示的數(shù)值整體左移到第1~7號數(shù)碼管上顯示,見圖1。總體而言,矩陣鍵盤及顯示電路的設計可分為4個部分:

(1)矩陣鍵盤的行及列的掃描控制和譯碼。該設計所使用的鍵盤是通過將列掃描信號作為輸入信號,控制行掃描信號輸出,然后根據(jù)行及列的掃描結果進行譯碼。

(2)機械式按鍵的防抖設計。由于機械式按鍵在按下和彈起的過程中均有5~10 ms的信號抖動時間,在信號抖動時間內無法有效判斷按鍵值,因此按鍵的防抖設計是非常關鍵的,也是該設計的一個重點。

(3)按鍵數(shù)值的移位寄存。由于該設計需要在8個數(shù)碼管上依次顯示前后共8次按鍵的數(shù)值,因此對已有數(shù)據(jù)的存儲和調用也是該設計的重點所在。

(4)數(shù)碼管的掃描和譯碼顯示。由于該設計使用了8個數(shù)碼管,因此需要對每個數(shù)碼管進行掃描控制,并根據(jù)按鍵值對每個數(shù)碼管進行7段數(shù)碼管的譯碼顯示。

2 矩陣鍵盤及顯示電路的實現(xiàn)

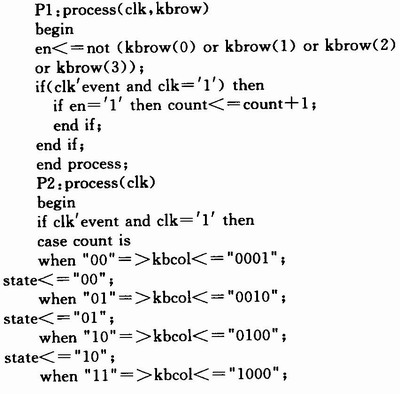

本文所設計的矩陣鍵盤及顯示電路的電路符號如圖2所示。其中,clk為時鐘信號輸入端(頻率可為1 024~32 768Hz);start為清零控制端;kbrow為列掃描信號輸入端;kbeol為行掃描信號輸出端;scan為數(shù)碼管地址掃描信號輸出端;seg7為數(shù)碼管顯示信號輸出端。

限于篇幅,在此不詳述所設計矩陣鍵盤及顯示電路的全部VHDL代碼,只對部分重要代碼段落進行詳細說明。

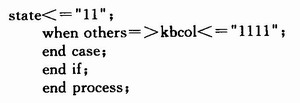

如圖1所示,全部代碼由7個進程(process)組成。其中,進程P1和P2用于對列掃描輸入信號kbrow進行讀取,并通過或非運算產生行掃描使能控制信號en對行掃描輸出信號kbcol進行控制,并生成一個與kbcol對應的狀態(tài)信號state。若沒有按鍵被按下(即kbrow="0000"),則en= '1',行掃描輸出信號kbcol不斷循環(huán)掃描各行;若有按鍵被按下,en=‘O’,則行掃描停止,并鎖存當前kbcol的值。進程P1和P2的代碼如下:

進程P3使用“case…when”語句,根據(jù)狀態(tài)信號state的值(即kbcol的值)和列掃描輸入信號kbrow的值進行按鍵值譯碼,生成一個4位二進制按鍵數(shù)值信號dat,用以記錄當前按鍵值。例如,當kbcol=“0010”,kbrow=“0001”時,“B”鍵按下,dat=“1011”。進程P3的代碼在此不再贅述。

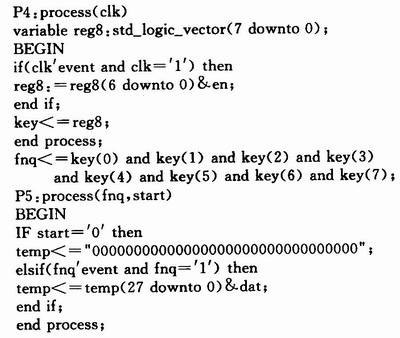

進程P4和P5用于按鍵的防抖和按鍵值的移位寄存。通過將行掃描使能控制信號en不斷賦給一個8位二進制變量reg8,再將reg8賦給8位二進制信號key,實現(xiàn)對按鍵狀態(tài)的記錄,然后通過對key的各位數(shù)值進行與運算,生成防抖控制信號fnq。一旦有按鍵按下,en=‘O’,則即便是按鍵在抖動,key中至少也有1位數(shù)值為‘0’,從而使fnq=‘O’。只有當按鍵再次彈起,并且在連續(xù)8個時鐘周期內不再有新的按鍵按下,key的數(shù)值全為‘1’,則fnq=‘1’,fnq產生一個上升沿,從而觸發(fā)按鍵數(shù)值信號dat進入數(shù)值寄存信號temp(32位二進制數(shù))的第0~3位,并將temp原來的第0~27位左移到第4~31位,實現(xiàn)1次按鍵按下的數(shù)值存儲。進程P4和P5的代碼如下:

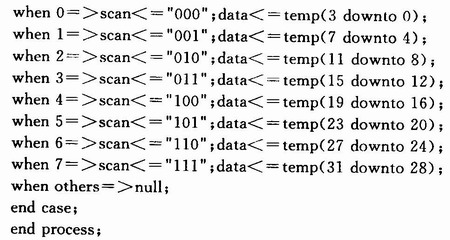

進程P6用于將數(shù)值寄存信號temp的32位二進制數(shù)分配給8個數(shù)碼管,從而生成數(shù)碼管地址掃描輸出scan,以及數(shù)碼管數(shù)值信號data(4位2進制數(shù))。進程P6代碼如下:

進程P7用于將數(shù)碼管數(shù)值信號data譯碼成為7段數(shù)碼管顯示輸出seg7,進程P7的代碼在此不再贅述。值得注意的是,本文設計的矩陣鍵盤及顯示電路在按鍵防抖和數(shù)據(jù)寄存部分設計得更加簡潔可靠,實現(xiàn)的功能更加強大,其具有如下特點:

(1)為了實現(xiàn)按鍵防抖,本文采用對按鍵狀態(tài)連續(xù)記錄的方式,即在按鍵彈起后連續(xù)8個時鐘周期均無按鍵信號才確認1次按鍵有效,從而避免了按鍵按下和彈起過程中的數(shù)據(jù)抖動,相比于使用計數(shù)器從按鍵按下開始計數(shù),直到5~10 ms后才讓按鍵有效的防抖方式,這里設計的按鍵防抖更加可靠,且可有效避免長時間按下按鍵產生的重復數(shù)據(jù)輸出,使每次按鍵無論時間長短均可且只會產生1次數(shù)據(jù)輸出。另外,當電路采用32 768 Hz以上的時鐘作為系統(tǒng)時鐘時,可以通過增加按鍵狀態(tài)連續(xù)記錄的時鐘周期數(shù),實現(xiàn)可靠的防抖。

(2)該設計采用一個32位一維數(shù)組temp作為數(shù)據(jù)寄存器,使用移位寄存方式,實現(xiàn)了對連續(xù)8次按鍵數(shù)據(jù)的存儲和調用,從而可以在8個數(shù)碼管上連續(xù)顯示數(shù)據(jù)。

3 仿真結果分析

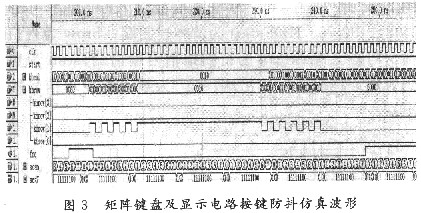

本文設計的矩陣鍵盤及顯示電路在QliartusⅡ開發(fā)環(huán)境下進行了仿真驗證。其中,按鍵防抖功能的仿真波形如圖3所示。仿真結果分析如下:

(1)clk為時鐘輸入信號,作為系統(tǒng)時鐘;

(2)start為清零控制端,當其為高電平時,按鍵有效;

(3)kbrow為列掃輸入信號,kbcol為行掃輸出信號,圖3中對kbrow[1]的輸入波形進行設置,模擬了“A”鍵按下和彈起的過程;

(4)fnq為防抖控制信號,scan為數(shù)碼管地址掃描輸出,seg7為數(shù)碼管顯示輸出。由圖3可知,只有在按鍵彈起后,才有數(shù)據(jù)輸出,從而實現(xiàn)防抖功能。

該設計的其他功能也可以通過仿真驗證,不再贅述。

4 結語

本文設計矩陣鍵盤及顯示電路在QuartusⅡ開發(fā)環(huán)境下進行仿真驗證后,下載到湖北眾友科技實業(yè)股份有限公司的ZYllEDAl3BE實驗箱中進行了硬件驗證。該實驗箱使用ACEXlK系列EPlK30QC208芯片作為核心芯片。實驗證明,當電路的系統(tǒng)時鐘頻率在1 024~32 768 Hz范圍內時,電路均可穩(wěn)定運行,按鍵防抖可靠、功能完整。當系統(tǒng)時鐘頻率低于1 024 Hz時,需要減少防抖記錄時鐘周期的個數(shù),否則容易錯過短時按鍵動作;當系統(tǒng)時鐘頻率高于32 768 Hz時,需要增加防抖記錄時鐘周期的個數(shù),以確保可靠的按鍵防抖。