0 引言

隨著通信事業(yè)的發(fā)展,信息傳輸量日益增加,無論公用通信網(wǎng)還是專用通信網(wǎng),通信的業(yè)務(wù)量都在迅猛增長,紅外和光系統(tǒng)已出現(xiàn)局限性,微波頻譜也已經(jīng)非常擁擠,面臨這樣的局面,毫米波通信以其得天獨厚的優(yōu)點得到各個領(lǐng)域的廣泛應(yīng)用。

毫米波波長短,其設(shè)備體積小、重量輕、耗電小、機動性好,在同樣口徑天線下,短波長的毫米波能實現(xiàn)窄波束、低副瓣,因而在目標(biāo)跟蹤和識別上能提供極高的精度和良好的分辨率,同時窄波束還可提高系統(tǒng)的隱蔽性和抗干擾能力。可通過構(gòu)建基于軟件無線電原理的毫米波通用硬件平臺將其系統(tǒng)化,而基于軟件無線電原理的毫米波硬件平臺,要求系統(tǒng)的各個組成部分具有可編程、靈活以及小型化的特點。在最大程度上實現(xiàn)該硬件平臺的開放性、數(shù)字化、標(biāo)準(zhǔn)化和可編程化。數(shù)字上變頻和下變頻技術(shù)是構(gòu)建毫米波通用硬件平臺的關(guān)鍵技術(shù)。基于此,本文給出一種兩次變頻法的毫米波發(fā)射端上變頻方案,并利用Altera公司的Cyclone系列EP1Cl2F324完成基帶數(shù)字信號處理,實現(xiàn)對AD9-857的控制,在數(shù)字域完成基帶數(shù)字信號的內(nèi)插濾波、正交調(diào)制、D/A變換等功能,實現(xiàn)70 MHz中頻載波上的QDPSK調(diào)制。

1 毫米波發(fā)射機

發(fā)射機是毫米波通信設(shè)備中的重要組成部分,其作用是將已調(diào)波經(jīng)過變頻、放大、濾波等處理后,輸送給天饋系統(tǒng),發(fā)向通信對方或轉(zhuǎn)發(fā)中繼站。發(fā)射機的變頻方案可分為兩種:直接變頻法和兩步變換法。直接變頻法是將調(diào)制和上變頻合二為一,在一個電路里完成;兩步變換法是將調(diào)制和上變頻分開,先在較低的中頻上進行調(diào)制,然后將已調(diào)信號上變頻到較高的載頻上(毫米波頻率)。

直接變頻法雖然簡單,但由于其承受功率限制,電路不能有效地提供足夠的輸出功率和較大的動態(tài)范圍,并且其他諧波的電平會遠(yuǎn)高于所需的信號,對濾波器和放大器的要求也非常高。兩步變換法可減弱直接變頻法的缺點,并且對載波適應(yīng)性強,頻率靈活性好,合理的頻率配置可有效地抑制各種雜散和變頻過程中產(chǎn)生的諧波、交調(diào)分量,提高系統(tǒng)的抗干擾性能。本方案采用兩步變換法,又由于系統(tǒng)工作在毫米波頻段,其工作頻率比較高,采用二次或多次的變頻方案。

本設(shè)計要將70 MHz的信號上變頻到31 GHz輸出,考慮到經(jīng)過功率放大后的強發(fā)射信號泄漏對發(fā)射機性能指標(biāo)將造成影響,并且此時采用濾波器來提取輸出信號非常困難,代價昂貴,因此采用兩次變頻的方法,將中頻信號調(diào)制后上變頻到毫米波頻段。設(shè)計方案如圖1所示。

圖1中,基帶信號經(jīng)中頻調(diào)制后得到70 MHz的中頻信號,中頻信號經(jīng)中頻放大和低通濾波后與2.93 GHz混頻得到3 GHz,再將3 GHz與29 GHz混頻得到31 GHz,即利用混頻上變頻到毫米波頻段。其中帶通濾波器用于抑制邊帶噪聲及倍頻產(chǎn)生的干擾,射頻放大器用于補償倍頻損耗。對于第一本振為獲得較高的頻率穩(wěn)定度、相位噪聲指標(biāo)和頻率分辨率,可采用混頻鎖相法設(shè)計。對于第二本振,由于其頻率達到29 GH- z,接近毫米波頻段,可采用微波鎖相,然后再倍頻的方案實現(xiàn)。

2 中頻調(diào)制方式選擇

毫米波信道一般為非線性信道。主要是以數(shù)字恒包絡(luò)調(diào)制為主,非恒包絡(luò)調(diào)制信號或多載波信號經(jīng)過毫米波非線性信道時,將導(dǎo)致頻譜擴展或產(chǎn)生交調(diào)失真信號。帶內(nèi)失真分量會干擾調(diào)制信號,產(chǎn)生矢量偏差,影響調(diào)制精度,使接收解調(diào)時的誤碼率增加;帶外失真分量則會干擾鄰近的信道。同時由于毫米波的功率放大技術(shù)成本較高,功率輸出有限,毫米波信道是屬于功率受限型,在接收端應(yīng)采用相干解調(diào)技術(shù)。因此在選擇適合毫米波通信信道的調(diào)制方式時,要注意以下幾點:

(1)要注意它與系統(tǒng)在信噪比方面的匹配度,要盡量使用在相同信噪比的條件下,具有較低誤碼率的調(diào)制方式,同時要考慮其頻帶的利用率;

(2)要考慮其在非線性信道上性能的惡化量,要盡量使用恒包絡(luò)調(diào)制方式;

(3)要分析其抗衰落的性能并考慮采用適當(dāng)?shù)拇胧┯枰匝a償。

數(shù)字通信系統(tǒng)中主要有ASK,F(xiàn)SK和PSK三種基本的調(diào)制方式,對目前常用的調(diào)制解調(diào)方式進行性能比較,可得出,在調(diào)制方式的實現(xiàn)方面,2PSK/2DPSK設(shè)備簡單、抗干擾能力強,對衰落信道和非線性信道的適應(yīng)能力強,但頻譜利用率不高。2FSK設(shè)備簡單,對衰落信道和非線性信道的適應(yīng)能力強,但其頻譜利用率和抗干擾能力都比2PSK/2DPSK差。4PSK/4DPSK的頻譜利用率是2PSK/2DPSK的兩倍,抗干擾能力與后

者一樣。設(shè)備復(fù)雜程度只有少許增加,對衰落信道的適應(yīng)能力適中,對信道的線性指標(biāo)要求也不太高。8PSK與4PSK/4DPSK相比,具有更高的頻率利用率,但設(shè)備復(fù)雜程度有所增加,對信道的衰落和失真特性也比后者敏感,需要采取一定措施來改善性能。

在抗噪方面,PSK性能最好、DPSK次之,其三是FSK,而ASK性能最差。但是,PSK系統(tǒng)的性能雖然優(yōu)于DPSK系統(tǒng),可它容易出現(xiàn)“相位模糊”。從系統(tǒng)的頻帶利用率來看,PSK和ASK比FSK占據(jù)更窄的信道帶寬,即PSK和ASK更有效,所以從抗噪聲性能和提高信道帶寬利用率角度來看,PSK是所有二進制鍵控方式中最優(yōu)的一種。

通過以上分析,由于QDPSK的頻譜利用率高于BPSK等方式,而抗噪聲性能要高于8PSK,16QAM等,且工程實現(xiàn)簡單,成本較低,因此本設(shè)計選用QDPSK調(diào)制方式。

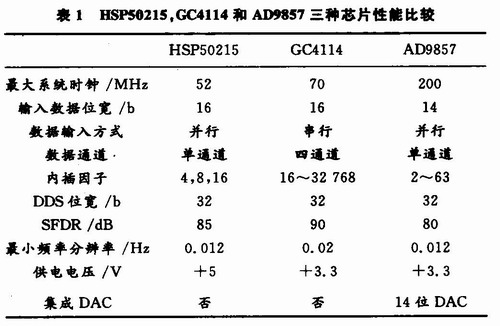

3 數(shù)字正交上變頻器選擇

數(shù)字上變頻器主要是對輸入數(shù)據(jù)進行各種調(diào)制和頻率變換,即在數(shù)字域內(nèi)實現(xiàn)調(diào)制和混頻。表1給出了具有代表性的數(shù)字上變頻器HSP-50215,GC4114和AD9857三種芯片的性能比較。

在比較了3種芯片的雜散性能和頻率分辨率等性能參數(shù)的基礎(chǔ)上,可得出AD9857的工作頻率最高,由于集成的高速直接數(shù)字合成器輸出頻率要小于系統(tǒng)時鐘的43%,因此輸出頻率范圍最大。此外AD9857內(nèi)部的14位高性能高速數(shù)/模轉(zhuǎn)換器,可提高系統(tǒng)的集成度和穩(wěn)定度。綜上所述,本文采用AD9857實現(xiàn)毫米波系統(tǒng)數(shù)字上變頻。

4 中頻調(diào)制設(shè)計

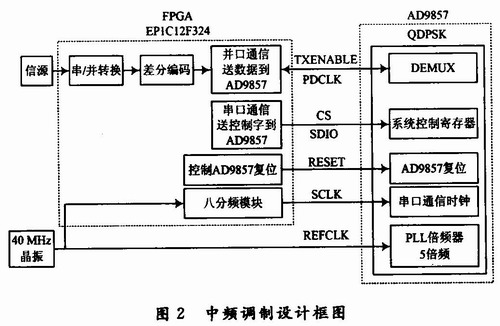

本設(shè)計采用基于DDS技術(shù)的正交上變頻器AD9857與FPGA相結(jié)合的方案實現(xiàn)70 MHz中頻的QDPSK調(diào)制。系統(tǒng)框圖如圖2所示。

由圖2可知,基于EP1Cl2F324的FPGA主要實現(xiàn)基帶信號處理、FPGA與AD9857的串口通信、FPGA與AD9857的并口通信和時鐘控制設(shè)計。

信源首先經(jīng)串并轉(zhuǎn)換將輸入的單路串行數(shù)據(jù)轉(zhuǎn)換為雙路并行數(shù)據(jù),經(jīng)過串并轉(zhuǎn)換產(chǎn)生的數(shù)據(jù)速率減半,再經(jīng)過“差分編碼”轉(zhuǎn)換為相對碼,通過并口送入AD9857進行絕對調(diào)相。在FPGA與AD9857串口通信中,當(dāng)CS為低電平時,開啟AD9857的串口,F(xiàn)PGA通過SDIO將控制字發(fā)送給AD9857,設(shè)置AD9857的工作方式,當(dāng)CS為高電平時,關(guān)閉AD9857的串口,串口通信仿真如圖3所示。在FPGA與AD9857的并口通信中,當(dāng)TXEN-ABLE為高電平時,通過PDCLK讀取FPGA中的14位并行數(shù)據(jù)送入AD9857,當(dāng)TXENABLE為低電平時,關(guān)閉AD9857的并口,并口通信仿真如圖4所示。

40 MHz晶振為EPlCl2F324提供系統(tǒng)時鐘;經(jīng)FPGA八分頻后通過SCLK送入AD9857中,作為串口通信時鐘;經(jīng)AD9857內(nèi)部PLL倍頻器五倍頻后,作為AD9857的內(nèi)部系統(tǒng)時鐘。

AD9857工作在正交調(diào)制模式,14位并行I/Q數(shù)據(jù)分成兩路交替輸入,經(jīng)過CIC濾波器,可編程內(nèi)插器后送人正交調(diào)制器。DDS核產(chǎn)生正交本振信號到正交調(diào)制器,分別與I/O信號相乘后相加或相減,產(chǎn)生正交調(diào)制信號。最后通過14位DAC轉(zhuǎn)變?yōu)檎徽{(diào)制的模擬信號輸出。

5 結(jié)語

采用AD9857和FPGA相結(jié)合的方法實現(xiàn)了中頻調(diào)制,由于AD9857采用了直接數(shù)字頻率合成技術(shù),消除了由模擬調(diào)制所引起的相位、增益的失衡和交調(diào)失真。該設(shè)計簡化了系統(tǒng)結(jié)構(gòu),降低了成本,提高了系統(tǒng)的性能和可靠性。同時提出了一種采用兩次變頻的上變頻方案,此方案降低了毫米波濾波器的設(shè)計難度,減弱了功率放大后的強發(fā)射信號泄漏對發(fā)射機性能指標(biāo)造成的影響。